内存管理单元(Memory Management Unit )

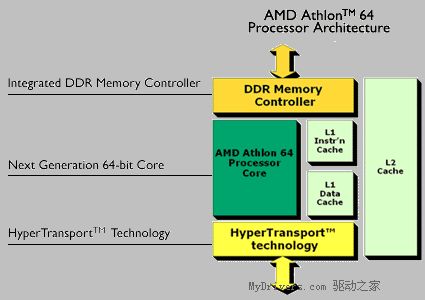

内存管理单元是在CPU内部

内存管理单元的作用:

虚拟地址到物理地址映射

存储器访问权限控制

高速缓存支持

以下出自:https://blog.csdn.net/yetaibing1990/article/details/88344416

如果CPU没有MMU、,或者有MMU但没有启用,CPU核在取指令或访问内存时发出的地址将直接传到CPU芯片的外部地址引脚上,直接被内存芯片(以下称为物理内存,以便与虚拟内存区分)接收,这称为物理地址。

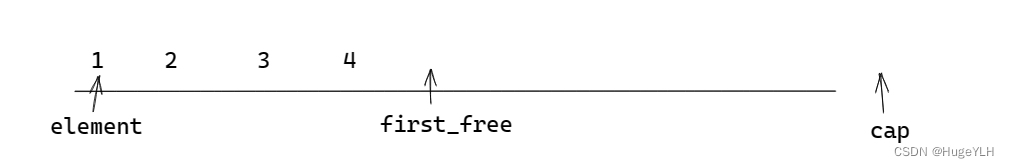

如果CPU启用了MMU,CPU核发出的地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(Virtual Address,以下简称VA),而MMU将这个地址翻译成另一个地址发到CPU芯片的外部地址引脚上,也就是将虚拟地址映射成物理地址,如下图所示。

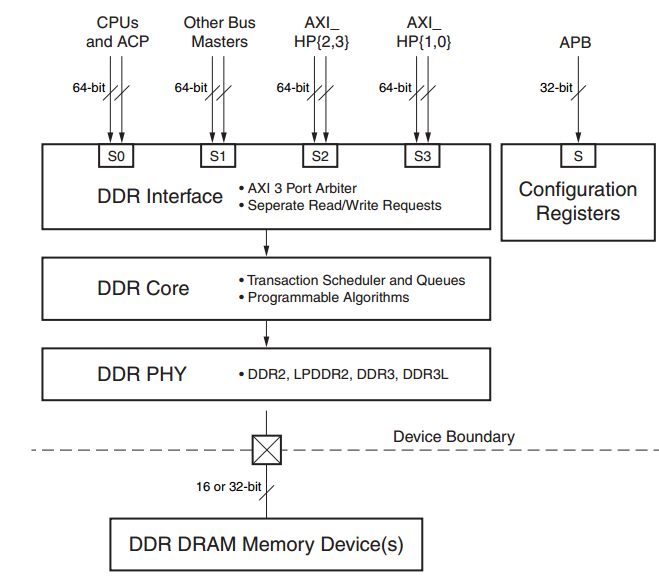

内存控制器(MEMORY CONTROLLER)

内存控制器是在CPU外部?

内存控制器的作用:

为外部存储器存储提供内存控制信号