1DDR内存控制器介绍

DDR内存控制器支持DDR2,DDR3,DDR3L和LPDDR2设备,包括三个主要块:AXI存储器端口接口(DDRI),带有交易调度器(DDRC)的核心控制器和具有数字PHY(DDRP)的控制器。

它具有四个64位同步AXI接口的DDRI块接口,可同时为多个AXI主机提供服务,每个AXI接口都有自己的专用交易FIFO。

DDRC包含两个32输入内容可寻址存储器(CAM),以执行DDR数据服务调度,以最大限度地提高DDR内存效率。它还包含用于低延迟通道的飞频通道,以允许访问DDR存储器而不通过凸轮。

PHY处理来自控制器的读/写请求,并将它们转换为目标DDR内存的时序约束中的特定信号,来自控制器的信号由PHY使用,以产生通过数字物理的连接到引脚的内部信号, DDR引脚通过PCB信号迹线直接连接到DDR设备。

系统通过其四个64位AXI内存端口通过DDRI访问DDR,一个AXI端口专用于CPU和ACP的L2-Cache,两个端口专用于AXI_HP接口,第四端口由AXI互连上的所有其他主控器共享。

DDR接口(DDRI)仲裁来自八个端口的请求(四个读取和四个写入),仲裁器选择请求并将其传递给DDR控制器和事务调度程序(DDRC),仲裁基于请求等待的长度,请求的紧迫性以及作为先前请求的同一页面中的组合基础。

DDRC通过单个接口从DDRI接收请求,读取和写入流通过此接口,读取请求包括使用DDR的数据返回的标记字段,DDR控制器PHY(DDRP)驱动DDR交易。

2DDR内存控制器特点

DDR控制器系统界面(DDRI)

DDR Controller系统界面具有以下功能:

-

四个相同的64位AXI端口支持Incr和Wrap Burst类型

-

四个64位AXI接口,具有单独的读/写端口和32位寻址

-

写入数据字节为每个数据击穿支持支持

-

复杂的仲裁计划,以防止数据饥饿

-

使用紧急比特来绕过仲裁逻辑的低延迟路径

-

深度读写命令验收能力

-

使用不同主设备ID的请求返回的无序读取数据

-

所有端口上的9位AXI ID信号

-

突发长度支持从1到16个数据节拍

-

突发大小为1,2,4,8(每个节拍的字节)

-

不支持来自任何AXI端口的锁定访问

-

使用HPR队列的低延迟读取机制

-

每个端口的特殊紧急信令

-

在64 MB边界上可编程的TrustZone区域

-

每个端口的两个不同ID的独占访问

DDR控制器PHY(DDRP)

DDR Controller PHY具有以下功能:

-

兼容DDR I / O.

-

1.2V LPDDR2.

-

1.8V DDR2.

-

1.5V DDR3和1.35V DDR3L

-

-

可选择的16位和32位数据总线宽度

-

16位数据宽度配置中的可选ECC

-

软件命令的自刷新条目和命令到达时自动退出

-

基于可编程空闲时段的自主DDR递减输入和退出

-

数据读取选通自动校准

DDR控制器核心和事务调度程序(DDRC)

DDR控制器核心和事务调度程序具有以下功能:

-

高效事务调度以优化数据带宽和延迟

-

高级重新订购引擎,以最大限度地提高内存访问效率,以实现连续读取和写入以及随机读取和写入

-

写入 - 读取地址碰撞检测以避免数据损坏

-

obeys axi订购规则

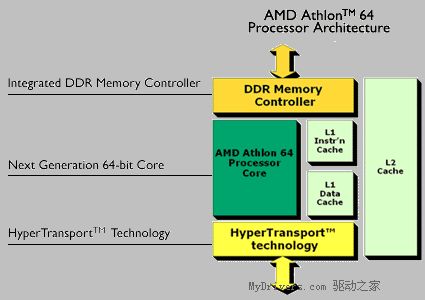

3DDR内存控制器框图

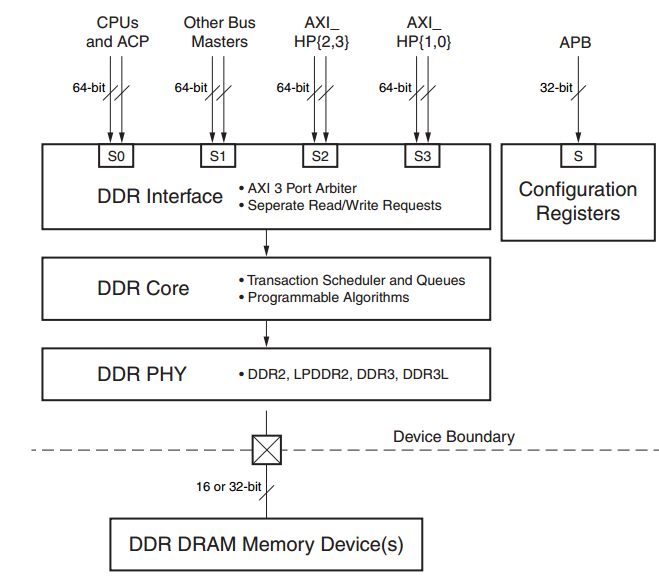

DDR内存控制器的框图如图所示,DDR内存控制器由仲裁器,具有事务调度器的核心组成,以及DDR存储器信号的物理排序。

DDR内存控制器块图

控制器核心和事务调度程序包含两个32输入凸轮,以执行DDR数据服务重新订购以最大限度地提高DDR内存访问效率,它还包含一个逐个通道,用于低延迟访问DDR存储器而不通过凸轮。

PHY处理来自控制器的读/写请求,并将它们转换为目标DDR内存的时序约束中的特定信号,来自控制器的信号由PHY使用,以产生使用PHY连接到PS焊盘的内部信号,焊盘通过PCB信号迹线直接连接到外部存储器设备。

仲裁器仲成四个AXI端口以访问DDR内核, 仲裁是基于优先权的,并且还通过紧急机制促进优先事项。

4DDR内存控制器工作原理

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。