High-Definition Multimedia Interface (HDMI)

参考xilinx application note XAPP460

HDMI来自High-Definition Multimedia Interface 高分辨率多媒体接口,多媒体一般包含图像和声音。

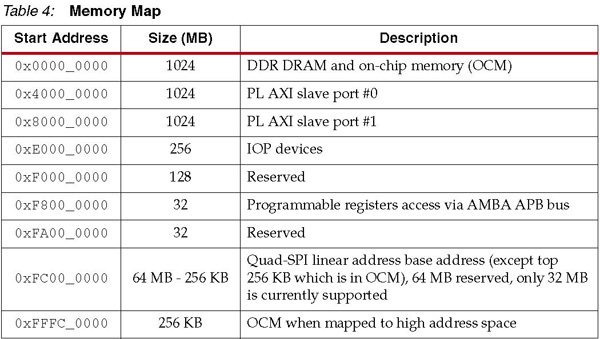

Transition Minimized Differential Signaling (TMDS) 是HDMI的物理层。

TMDS有三个串行通道,分别为Channel 0,Channel 1,Channel 2 ,Pixel Clock。

每个通道把输入的并行信号进行串行编码,然后进行发送,接受后把串行数据解码转换为并行数据。

并行传输需要使用大量位宽,在传输线上1 BIT就需要一根线,并行传输必然会产生大量的传输线,线越多传输越困难。

所以把并行数据转换为串行信号(一条数据线)可以减少数据线,提高传输能力。

Transition Minimized 我的理解是传输位宽尽量的小。

Differential Signaling 差分信号传输,提高传输信号在物理层的抗干扰性。

Transition Minimized Differential Signaling (TMDS) 具体的拓扑图如下所示

在Channel 0,Channel 1,Channel 2上分别传输Blue,Green,Red 分量的颜色信号。

D[7:0] 表示传输位宽为8 bit,所以TMDI的RGB信号是分为三个通道传输。

Channel 0 可以携带行场同步信号

Channel 1,Channel 2 携带 额外的控制字段。

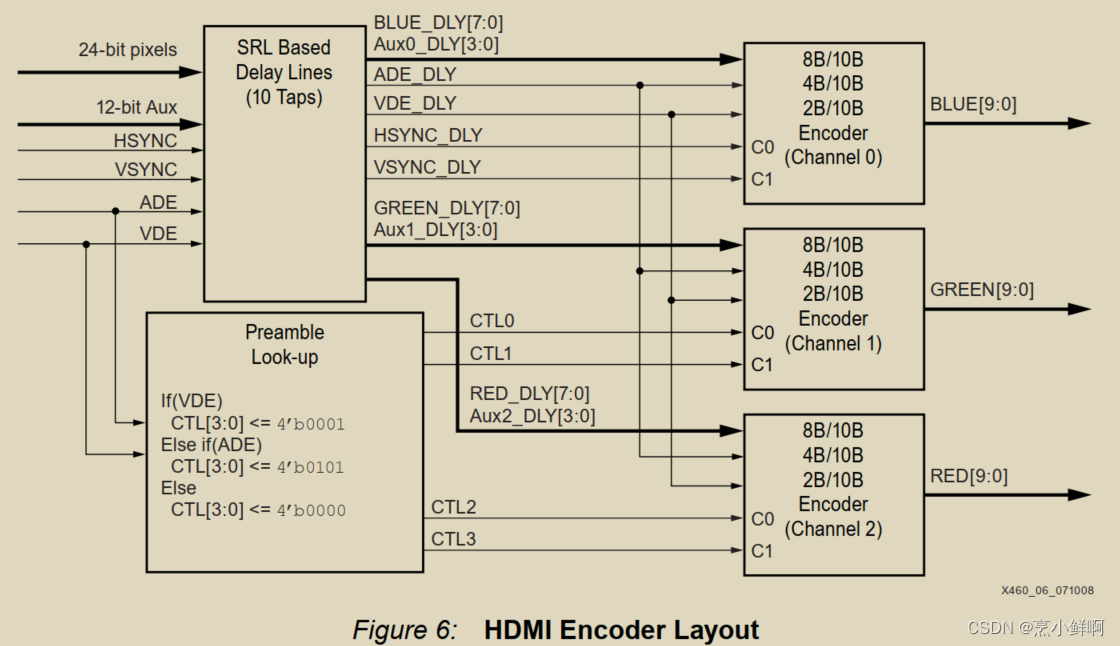

HDMI在TMDI基础上进行在扩展,在原有TMDI基础上每个通道多传输4 bit位宽的信息,可以用来传输声音,字幕等等。

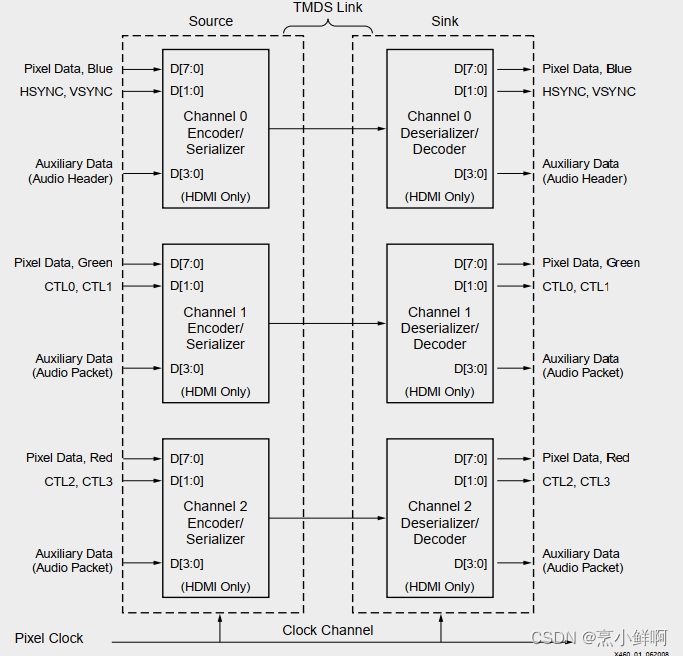

传输时序 DVI

DVI为数字影响传输接口,其物理层也是使用TMDI

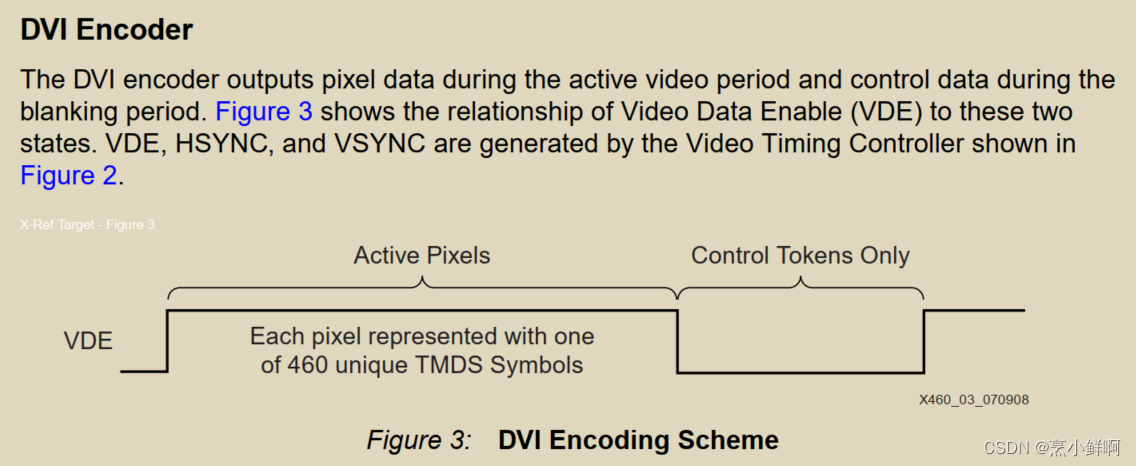

VDE表示Video Data Enbale,有效时表示正在传输图像信号RGB,8 bit 的数据经过编码变成 10bit。低电平时,称为消隐期间(blanking period),用来传输非图像数据。也就是每个通道除了图像信号的其他信号,行场同步控制字同样是 2bit 转为10bit。

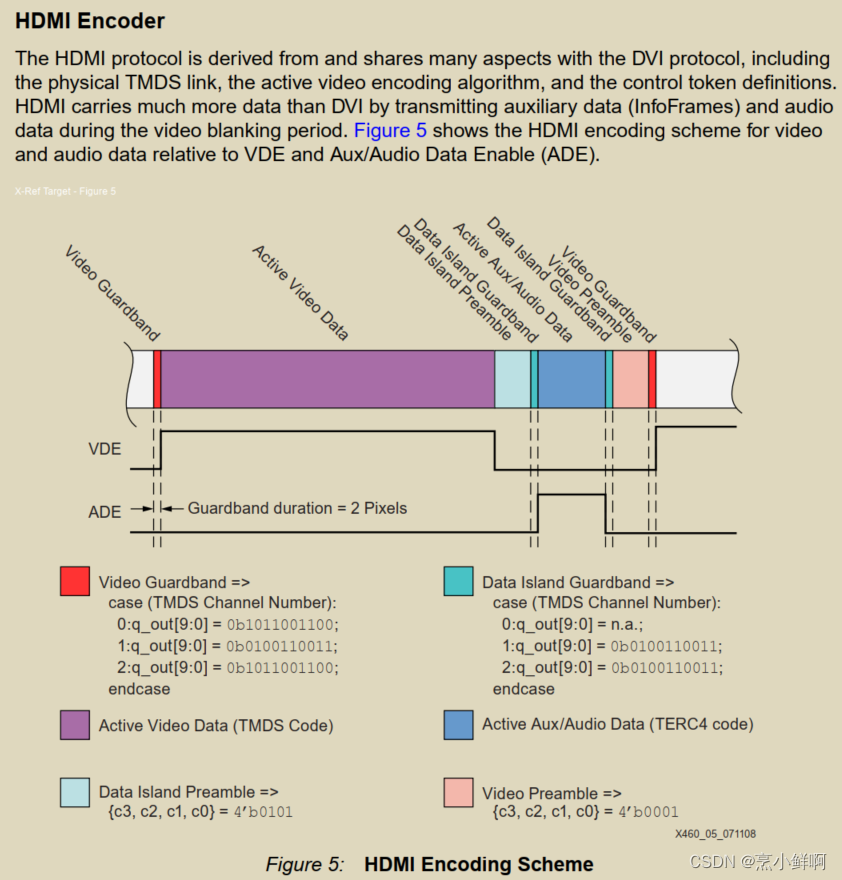

HDMI的编码规则沿用TMDI,区别在于HDMI在VDE消隐期间传输了更多的数据。

同时在消隐期传输是加入了跟过的冗余数据。前导数据,数据岛前后字段。总体理解还是不难。