1 开发工具

1.1 独立开发环境

PL—>Vivado

PS(ARM)-->SDK(Xilinx)或者第三方ARM开发工具

1.2 集成开发环境

SDSoC

1.3 总结

Ø 独立开发环境大概分为四个步骤:

(1) 系统架构师确定硬件-软件分区方案;

(2) 硬件工程师处理被分配到硬件中的功能,并将它们转换或设计成IP核(Verilog/VHDL,也可用Vivado HLS实现C/C++高层次综合);

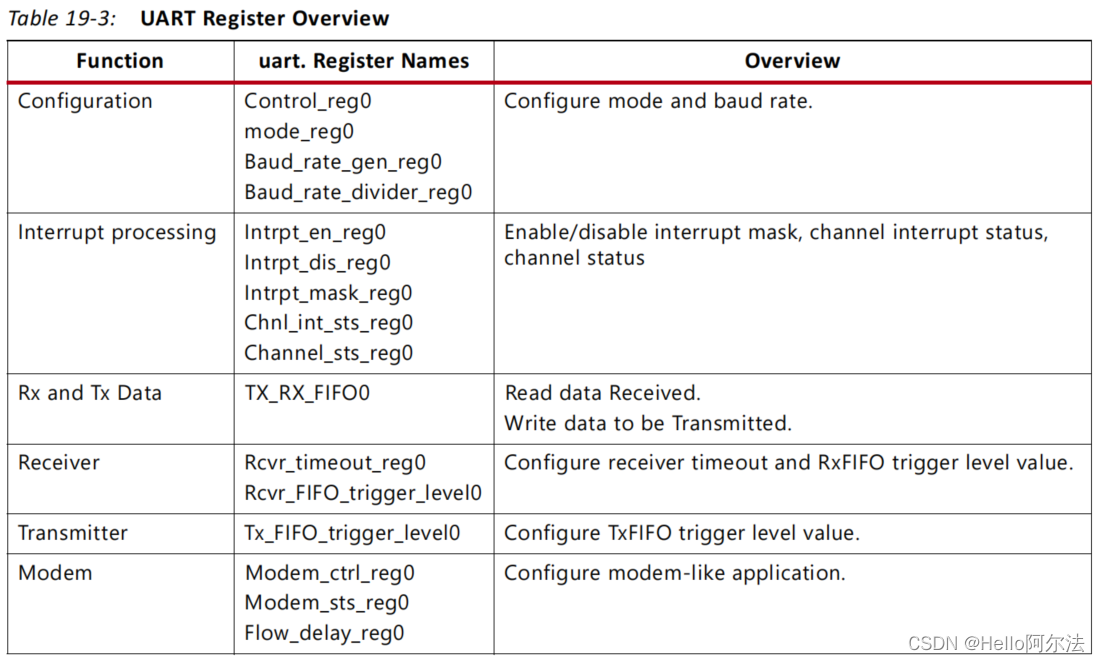

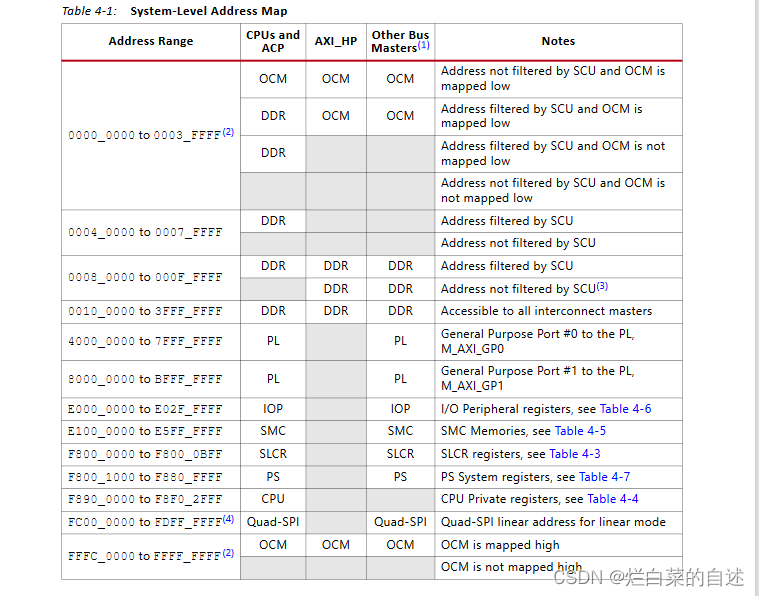

(3) 利用Vivado IP Integrator 创建整个嵌入式系统的模块化设计。包括开发需要的数据移动工具(AXI-DMA、AXI Memory Master、AXI-FIFO 等),以及连接 PL IP 与 PS 的 AXI 接口(GP、HP 和 ACP),之后将此项目导入到SDK中;

(4) 软件工程师使用SDK开发PS中ARM处理器的驱动程序和应用。

对于以硬件为中心的优化流程,矛盾往往出现在不同的数据移动工具和PL-PS接口以及写入和调试驱动程序与应用,为避免重构硬件造成软件的变化,使得PS-PL开发更加紧密,赛灵思推出了SDSoC开发环境。将上述步骤(2)、(3)和(4)实现高度自动化,以缩短开发时间。该开发环境会生成必要的硬件和软件组件,用以同步硬件和软件并保存源程序语义,同时支持任务级并行处理和流水线化的通信与计算,从而实现高性能。SDSoC 环境会自动安排所有必要的赛灵思工具(Vivado、IP Integrator、HLS 和 SDK),以生成针对 Zynq SoC 的完整软硬件系统,而且所需的用户介入程度很小。

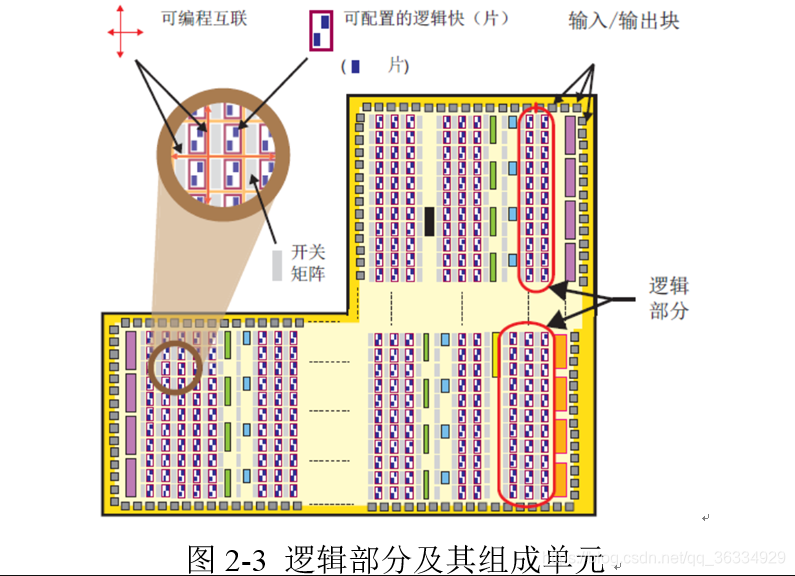

2 Vivado

Vivado是基于IP的设计,称为blockdesign(BD),调用已有的IP,用户自己编写的逻辑模块也封装成IP,然后在模块blcok中连线。逻辑开发完毕,再转到SDK,SDK会根据Vivado的硬件设计设置调用相应的内部驱动代码。(PL部分就如同ARM的总线AXI等挂的外设)

2.1 开发步骤

(1) 新建工程,选择要开发的zynq芯片型号;

(2) 点击“Create Block Design”,新建一个模块block,并命名;

(3) 点击“IP Catalog”,添加所需要的IP(包括ARM,PL-PS的接口,外围接口模块等等),用户自己编写的逻辑模块封装成IP,与固定IP一样在此添加到BD中。

(4) 约束文件(管脚约束、时序约束);

(5) 点击“Generate Bitstream”,开始综合、布线、生成bit文件;

(6) 最后File -> Export ->Export Hardware 导出 .hdf 硬件描述文件给SDK用。

3 SDK

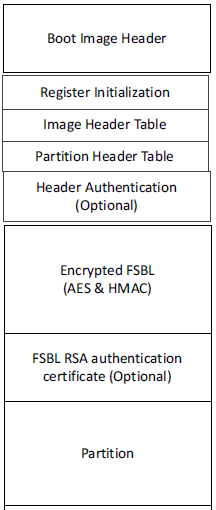

SDK根据上述生成的.hdf文件匹配FSBL,只需添加main.c文件即可。

3.1 步骤

(1) 在SDK中会根据.hdf文件显示配置好的硬件配置环境;

(2) File -> New ->Application Project

(3) 系统会根据hdf配置好对应的板级支持包bsp,这个就是库函数。在src里面添加main.c,写控制代码,保存的时候会自动编译

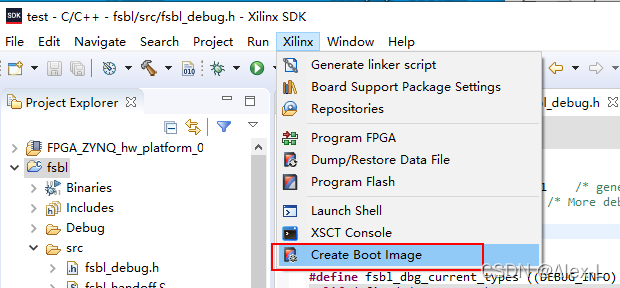

(4) 烧写FPGA的bit文件,然后点击Run,临时调试,也可以做成boot.bin文件烧写到外flash或SD卡里面;

4 类似嵌入式 C/C++/OpenCL 应用开发的体验--SDSoC

SDSoC™ 开发环境可为异构 Zynq® AllProgrammable SoC 及 MPSoC 部署提供类似嵌入式 C/C++/OpenCL 应用的开发体验,其中包括简单易用的 Eclipse IDE 和综合设计环境。SDSoC 提供业界首款 C/C++/OpenCL 全系统优化编译器,可实现系统级的特性描述、可编程逻辑中的自动软件加速、自动系统连接生成以及可加速编程的各种库。此外,它还可帮助最终用户及第三方平台开发人员快速定义、集成和验证系统级解决方案,为其最终用户实现定制化编程环境。(软件工程师能够对 Zynq SoC 中的可编程逻辑和 ARM 处理系统进行编程)

l 简单易用的 EclipseIDE 可用于开发支持嵌入式 C/C++/OpenCL 应用的全面 Zynq All Programmable SoC 和 MPSoC 系统

l 只需一点按钮,就可对可编程逻辑 (PL) 中的功能进行加速

l 支持作为目标 OS 的裸机、Linux 与 FreeRTOS

l Xilinx 库作为 Vivado HLS 的一部分,由联盟成员提供,是可选硬件优化的库。

l OpenCL 在 2016.3 版中为早期的测试版。请联系您的当地销售代表提出申请

4.1 系统级的特性描述

l 快速性能估算与面积估算可在几分钟内完成,包括 PS、数据通信以及 PL

l 高速缓存、存储器以及总线利用率的自动运行时仪表

l 可实现最佳总体系统架构的便捷生成与探索

4.2 全系统优化编译器

l 可将C/C++/OpenCL 应用编译成全功能 Zynq SoC 与 MPSoC 系统

l 可在生成 ARM 软件与 FPGA 比特流的可编程逻辑中实现自动功能加速

l 不仅可优化系统连接,而且还支持吞吐量、时延以及面积权衡的快速系统探索

4.3 SDSoC开发流程

1. SDSoC 环境使用快速估算流程(通过调用内含的Vivado HLS)构建应用项目。这样在数分钟内就能大致估算出性能和资源情况。

2. 如果有必要,用适当的指令优化 C/C++ 应用和硬件功能,并重新运行估算直到实现所需的性能和占位面积。

3. 然后,SDSoC 环境构建整个系统。该过程会生成完整的 Vivado Design Suite 项目和比特流,以及一个针对 Linux、FreeRTOS 或裸机的可引导的运行时间软件映像。