摘要

本文参考芯片手册详细介绍了ZYNQ7000芯片的信号、接口与引脚,结合芯片封装说明了引脚的类别与分布,并说明了MIO与EMIO的区别。

关键词:ZYNQ;信号;引脚;MIO;EMIO;Bank

前言

了解ZYNQ7000的基础知识可参考我的另一篇博客:

传送门:ZYNQ-7000概述

一. ZYNQ7000的信号、接口与引脚

参考:UG585 - Zynq-7000 SoC Technical Reference Manual (v1.12.2) 42~59页–Ch2: Signals, Interfaces, and Pins。

1.1 ZYNQ7000引脚分组

下图展示了ZYNQ7000信号、接口与引脚的大致分组。

可见,ZYNQ7000分为PS与PL两部分,信号、接口和引脚也分属这两部分。

PS部分:

| 分类 | 名称 | 说明 |

|---|---|---|

| PS信号与接口 | PS_CLK | PS侧专用时钟引脚,为CPU工作提供外部时钟 |

| POR_RST_N SRST_N | power on reset 上电复位 外部输入的同步复位 | |

| DDR Memory | 连接DDR的接口 | |

| USB | 连接USB的接口 | |

| Quad-SPI | 连接FLASH的接口 | |

| NAND, NOR/SRAM | 连接SRAM的接口 | |

| PS Power Pins | PS Power Pins | PS电源引脚,提供多种电平的电源 |

| Boot Mode MIO | Boot Mode MIO | PS侧的启动模式引脚,控制ZYNQ的启动模式 |

| MIO Pins, EMIO Signals | GigE, SDIO, SPI, I2C, CAN, UART, GPIO, TTC, SWDT | PS侧多种外设,既可以使用MIO引脚, 也可以使用EMIO引脚 |

| JTAG | JTAG | PS与PL共有的JTAG引脚, 烧写与调试PS/PL程序 |

PL部分:

| 分类 | 名称 | 说明 |

|---|---|---|

| PL Signals | User SelectIO | PL为FPGA,用户可更加需要任意指定信号对应的引脚 |

| XADC | PL部分的ADC,对应引脚为固定的ADC专用引脚 | |

| MGTX | 只所示这几种芯片才有的MGTX专用引脚 | |

| PL Power Pins | PL Power Pins | PL供电引脚,提供多种PL电平 |

PS-PL交互部分(交互在芯片内部,故只存在接口与信号,不存在引脚):

| 分类 | 名称 | 说明 |

|---|---|---|

| AXI Interfaces | M_AXI_GP × 2 | 2组AXI GP主机接口 |

| S_AXI_GP × 2 | 2组AXI GP从机接口 | |

| S_AXI_HP × 4 | 4组AXI HP从机接口 | |

| S_AXI_ACP | 1组AXI ACP从机接口 | |

| Misc(杂项), PL Signals | FCLKS | PS提供给PL的时钟信号 |

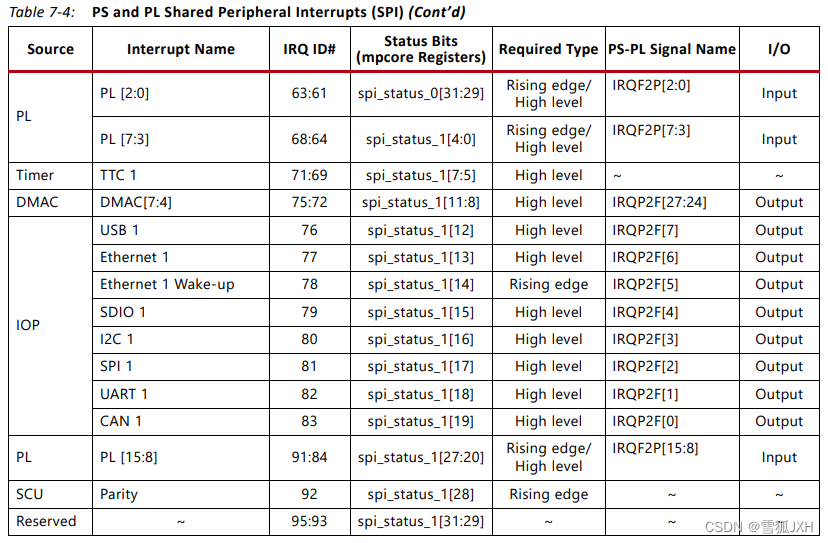

| IRQ, Event, Standby | PL <-> PS 中断 | |

| DMA Req/Ack | DMA请求与应答 | |

| DDR Arb, AXI Idle, SRAM Int | 存储器控制 | |

| FTMD Trace, FTMT Trigs | 调试信号 |

总结一下,除去电源、地、时钟、复位、JTAG这五种引脚外,PS部分还有专门对接DDR,SRAM,USB的引脚,PL部分只有XADC和一些芯片的MGTX引脚是专用的,其余引脚均可任意配置。

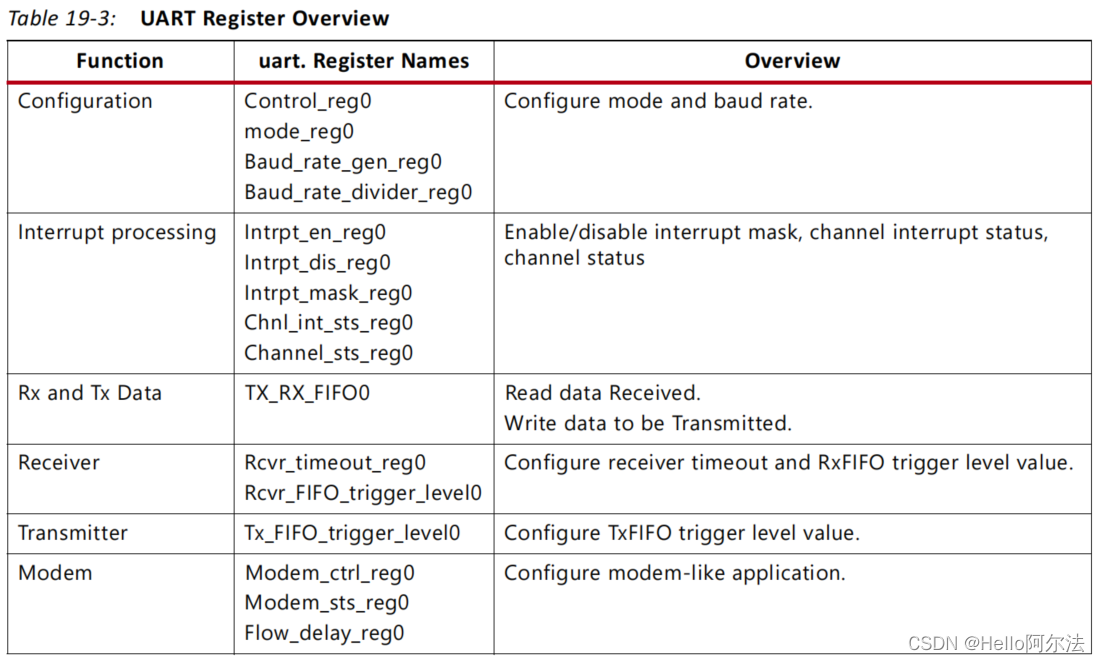

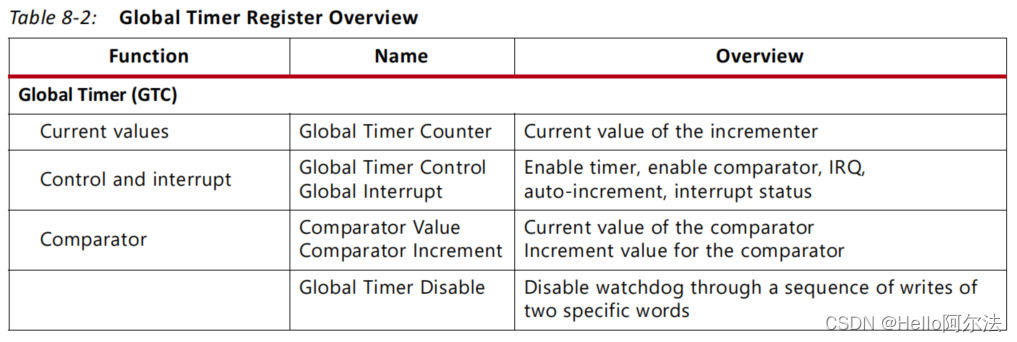

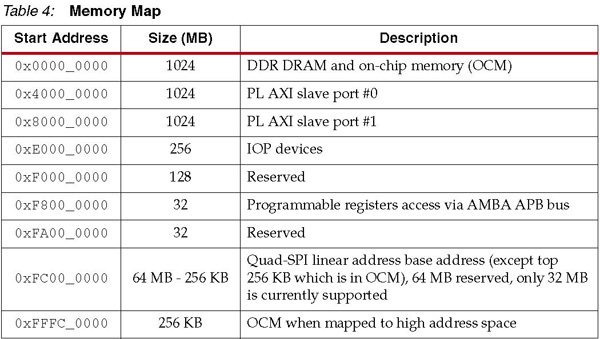

1.2 电源引脚

PS与PL部分均需要多种电平的供电电源,电源需要从特定的电源引脚接入芯片。相关电源引脚(包含ADC与地)信息如下表所示。

1.3 PS信号引脚

PS部分除电源引脚外的引脚信息如下图所示。从这里可以看出来,PS部分的引脚除了电源、地、时钟、复位和DDR专用引脚外均为MIO引脚。

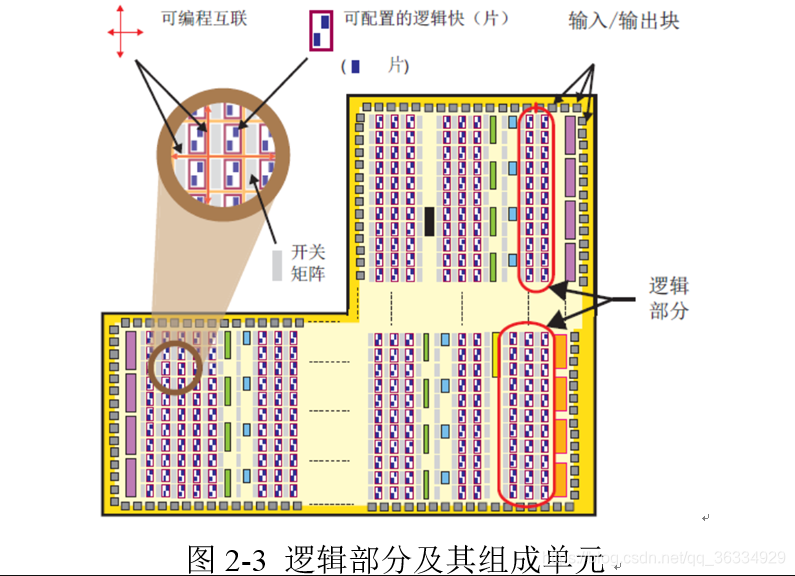

1.4 PL信号引脚

PL部分有少量的引脚用作特殊功能,绝大部分引脚为用户引脚,可任意配置,这些User I/O Pins即为EMIO引脚。

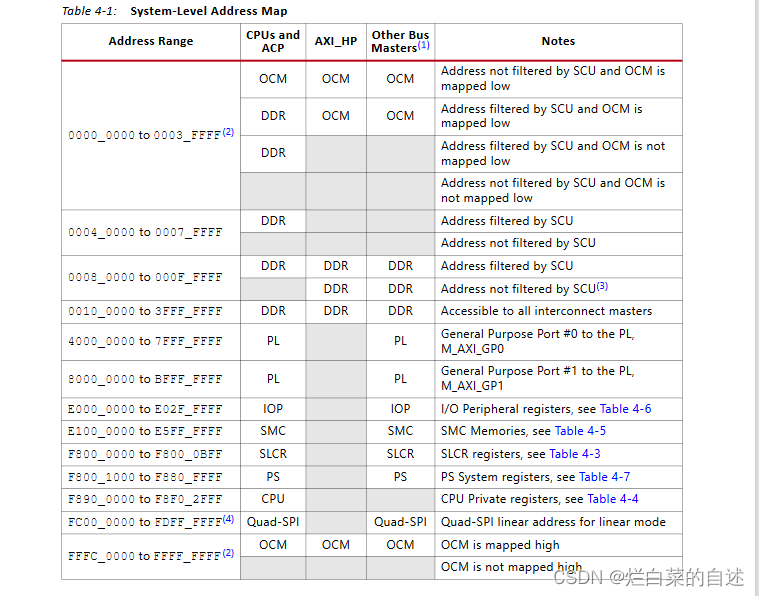

二. ZYNQ7000某芯片的引脚分布

参考:ug865 Zynq-7000 SoC Packaging and Pinout 30~32页 CL225/CLG225 Packages—XC7Z007S, XC7Z010, and XA7Z010

以最简单CL225封装引脚图为例,查看下ZYNQ芯片的引脚分布情况。

可以看到,空白圆⚪️为EMIO,空白六边形为MIO。

除了Dedicated Pins(专用引脚)与 Other Pins(其它引脚,由电源、地以及NC引脚组成)外,剩下的引脚根据各自的供电引脚不同分组即分为不同的Bank,Banks分布图如下:

其中,500, 501, 502这些50X的Bank为PS侧的引脚,34, 35这些3X的Bank为PL侧的引脚。其它封装也遵循此Bank命名方式。

也可以看出,PS侧的Bank主要是由DDR引脚与MIO引脚构成。PL侧Bank由少量Multi-Function引脚和EMIO构成。

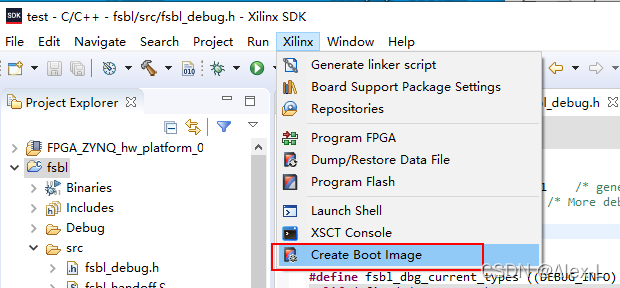

三. MIO与EMIO概览及两者的区别

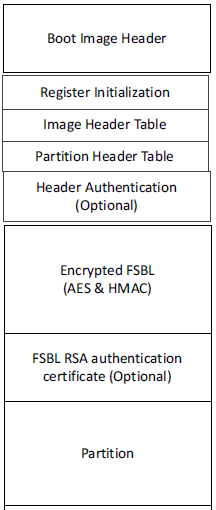

下图展示了MIO与EMIO接口概览。

MIO,Multiuse I/O,称为复用输入/输出,对应PS侧的可配置的多功能引脚。

EMIO,Extent MIO,称为扩展复用输入/输出,对应PL侧的可配置的多功能引脚。

MIO是外设的基础引脚,因为MIO引脚数量较少,ZYNQ也提供了EMIO接口作为MIO的扩展,外设可通过EMIO接口路由到PL侧的引脚上,来实现与MIO几乎相同的功能。

几乎相同也就意味着有些许不同,MIO和EMIO作为引脚不同的地方有3点:

1.MIO对于PL侧是透明的,PL无法得到MIO引脚上的电平信息,而EMIO因为就是PL的引脚,所以PS可以通过EMIO与PL通信

2.外设与MIO是固定搭配的,就是说要使用MIO作为外设引脚就必须是一组固定引脚。如下图,举个例子,如果你使用了MIO34作为UART0的一个引脚,那么UART0的另一个引脚必须是MIO35,USB1也是如此,除了GPIO比较特殊外,其它外设MIO都是一组一组起作用的,并且是产商预先定好的位置,不能任意指定,所以在设计硬件电路时,使用哪些引脚来连接外设要遵照这一特性。另外因为电路是确定的,使用MIO也不用指定引脚约束。

EMIO相对灵活,引脚之间预先没有绑定,可任意指定,而且使用EMIO需要加引脚约束指定到PL确定的某个引脚。

3.因为MIO引脚位置更靠近这些外设电路,所以相较于使用EMIO,一些外设使用MIO性能更好。还有一些外设只能使用MIO无法使用EMIO(上图也有展示),UG585中说明了这些差异,如下图所示。

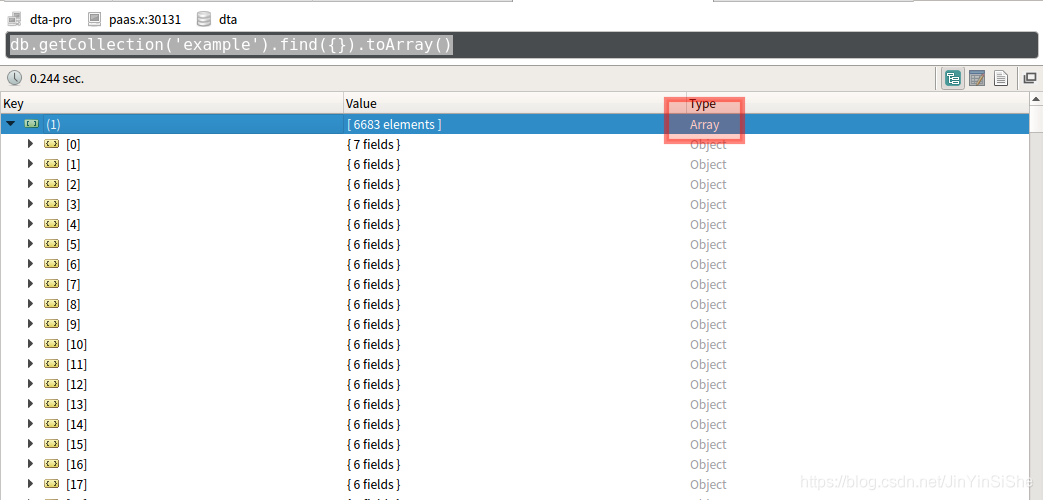

四. MIO Bank与封装Bank的区别与联系

在 二. ZYNQ7000某芯片的引脚分布 中已经说明了封装是分Bank的,而MIO引脚也是分Bank的,MIO分为Bank 0 和 Bank 1,其中 MIO Bank 0是封装Bank 500中的部分引脚,MIO Bank 1是封装Bank501中的部分引脚。具体MIO引脚的Bank分布及其与外设的关系如下图MIO一览表所示。

Bank 0包括MIO 0~15 共16个MIO,Bank 1包括 MIO 16~53 共38个MIO(除了7z010和7z007s外),所以,MIO共54个。

而EMIO共64个。

五. 特殊的MIO

一般来说MIO同一程序只能被配置成一种功能,而MIO[2:8]不同,这些引脚在芯片上电启动时起作用,它们还可被配置为其它功能,这并不冲突,因为其它功能是在芯片启动后起作用,这时MIO[2:8]的启动模式选择功能等就失效了。

MIO[8:7]控制Bank的电压,MIO6控制PLL使能,MIO[5:2]控制Boot Mode。

同时MIOMIO[8:7]只能被配置为输出。

六. 总结

本文介绍了ZYNQ7000系列芯片的引脚的基本信息,包括引脚的分类,分布,Bank等。还重点介绍了MIO与EMIO的定义以及两者间的区别。基本上,MIO可理解外PS侧的用户IO,EMIO则为PL侧的用户IO,它们均被配置为多种功能。EMIO是对MIO的扩展,它可以作为PS与PL通讯的一种媒介。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。