前言

ZYNQ内部集成两个ARM Cortex A9核心,Xilinx也推出了Petalinux工具,与Vidado搭配可以方便地完成Linux的uboot、kernel、rootfs部署。

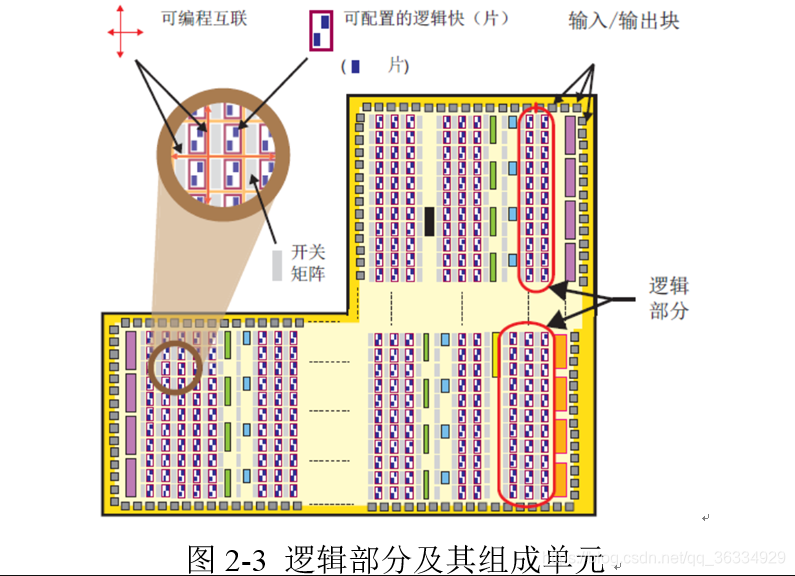

开发板上集成了HDMI,但是需要在FPGA中实现逻辑,但是实现之后占用了7010快一半的资源,多少有点离谱,而且HDMI还是不方便,所以就用linux内核中的fbtft驱动来实现显示,只占用了几个EMIO以及PS端的SPI即可实现。

文中Vivado以及Petalinux版本均为v2018.3。

Vivado

在上文的基础上在PS的ZYNQ7 Processing System中增加使能SD0,ETH0,QSPI Flash,视使用情况而定。

generate output products -> create HDL wapper -> Elaborated Design I/O Ports -> Generate Bitstream -> Export Hardware(勾上include bitstream)。

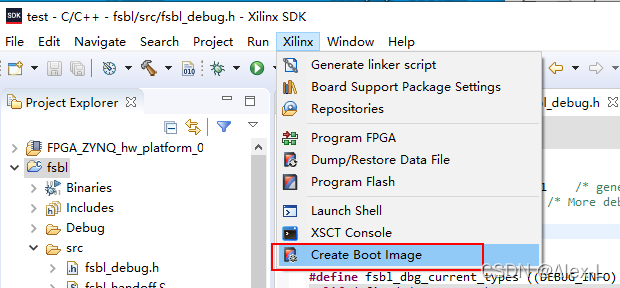

启动一下SDK,在SDK的工作文件夹里找到system.hdf,拷出供Petalinux用。

Petalinux

Petalinux必须在Linux中运行,Vidado可以在Linux和Windows下运行。

Petalinux Config

安装玩Petalinx后,在每次打开终端之后要source一下petalinux安装目录下的setting.sh。

找一个目录新建vidado工程:petalinux-create -t project --template zynq -n <NAME>

进工程目录在载入HDF硬件描述文件:petalinux-config --get-hw-description=.

=后面跟着的是hdf文件所在目录,如果就在当前目录下写个.就行。

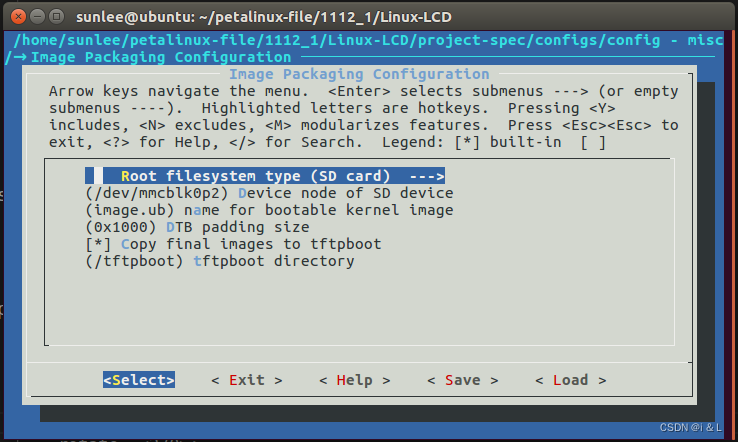

此时会弹出petalinux的配置界面,一般没什么要改的,这里把根文件系统的形式改为SD card。

如果以后要更改这些设置就运行petalinux-config。

Save保存,Exit退出。

Kernel Config

一般都要配置一下内核,主要涉及到一些驱动,不过Petalinux已经帮助配置了大部分功能了,直接编译也可以启动。

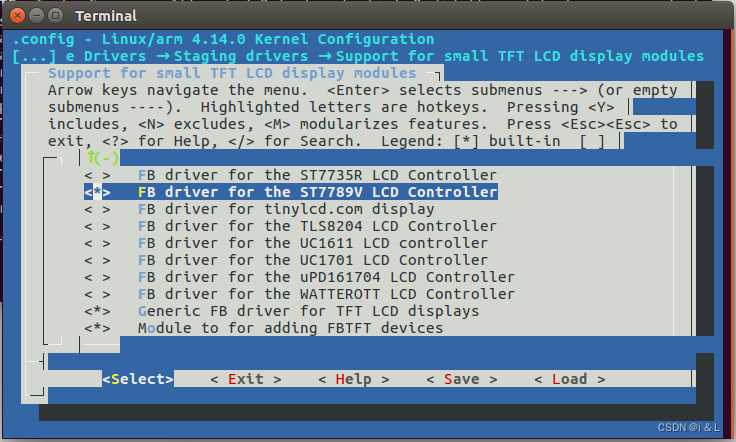

因为板子上连接了一块LCD屏幕,所以这里使能一下fbtft,这是一个Staging Driver,可以把很多LCD配置成fbx显示器。具体位置在Device Drivers → Staging drivers → Support for small TFT LCD display modules,空格使能到[*],即直接编译进内核,再进去使能对应LCD的型号。

保存,退出。

Device Tree

内核使能了驱动相应的功能,Linux ARM系统要把功能与设备连接起来还需要设备树。Petalinux工程的供用户修改设备树在<工程目录>/project-spec/meta-user/recipes-bsp/device-tree/file/下的system-user.dtsi文件夹内。还有一部分由Petalinx自动生成的设备树在<用户目录>/components/plnx_workspace/device-tree/device-tree/下,从system-top.dts中可以看出来,用户可修改的设备树在最后,设备树有覆盖的功能呢,所以这里的设备树就不要动了,有需要添加的地方在system-user.dtsi中覆盖修改即可。

system-user.dtsi文件一般卖板子的会给模板,或者基于别的模板修改也行。

/include/ "system-conf.dtsi"

#define GPIO_ACTIVE_HIGH 0

#define GPIO_ACTIVE_LOW 1

/ { model = "Zybo Development Board"; compatible = "zynq7010,zynq-7020","xlnx,zynq-7000";usb_phy0: phy0 {compatible = "ulpi-phy";#phy-cells = <0>;reg = <0xe0002000 0x1000>;view-port = <0x170>;drv-vbus;};leds {compatible = "gpio-leds";gpio-led1 {label = "led1";gpios = <&gpio0 56 GPIO_ACTIVE_HIGH>;default-state = "off";};gpio-led2 {label = "led2";gpios = <&gpio0 57 GPIO_ACTIVE_HIGH>;default-state = "on";};gpio-led3 {label = "led3";gpios = <&gpio0 58 GPIO_ACTIVE_HIGH>;default-state = "off";};gpio-led4 {label = "led4";gpios = <&gpio0 59 GPIO_ACTIVE_HIGH>;linux,default-trigger = "heartbeat";};};

};

&usb0{dr_mode = "host";usb-phy = <&usb_phy0>;

};

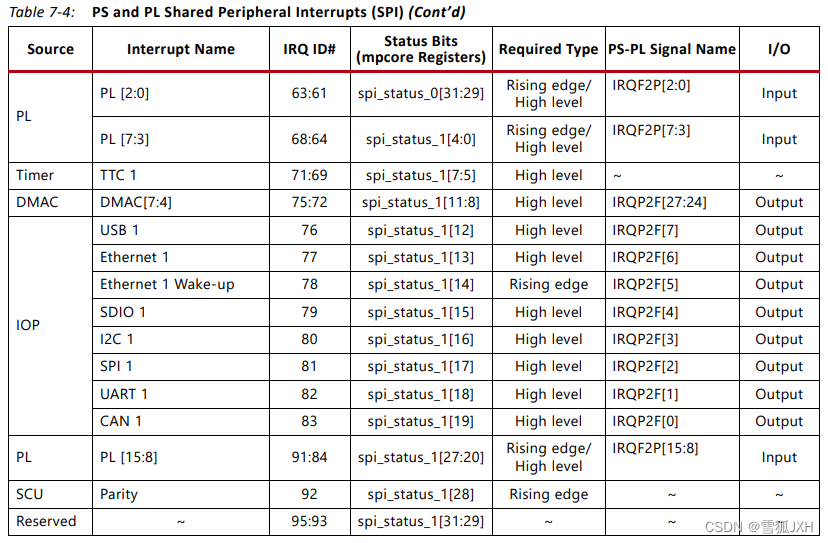

&spi0 {st7789v@0 {status = "okay";compatible = "sitronix,st7789v";reg = <0>;spi-max-frequency =<32000000>; //SPI时钟32Mrotate =<270>;spi-cpol;spi-cpha;rgb; //颜色格式RGBfps =<30>; //刷新30帧率buswidth =<8>; //总线宽度8reset-gpios=<&gpio0 55 GPIO_ACTIVE_HIGH>; //EMIO 55dc-gpios =<&gpio0 54 GPIO_ACTIVE_LOW>; //EMIO 54width = <240>;height= <320>;debug =<0>; //不开启调试};

};

在这里主要添加了四个LED,再在SPI总线上添加LCD显示屏参数,LCD显示屏上还有reset和dc两个GPIO要根据需求添加,这里要注意reset-gpios要设置成GPIO_ACTIVE_HIGH,dc-gpios要设置成GPIO_ACTIVE_LOW。

编译

根文件系统就先不改啥了,直接运行petalinux-build编译。

system-user.dtsi写错了容易编译不通过,所以可以先不改system-user.dtsi编译,第一次通过之后再修改system-user.dtsi,然后只编译内核petalinux-build -c kernel。

打包再烧录到SD card

编译通过后要进行打包,这里应该是考虑到petalinux运行在不同的系统上有不同的启动方式,所以打包需要手动运行。

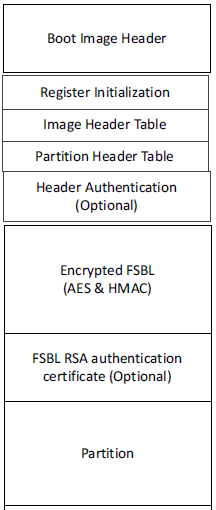

petalinux-package --boot --fsbl --fpga --uboot --force

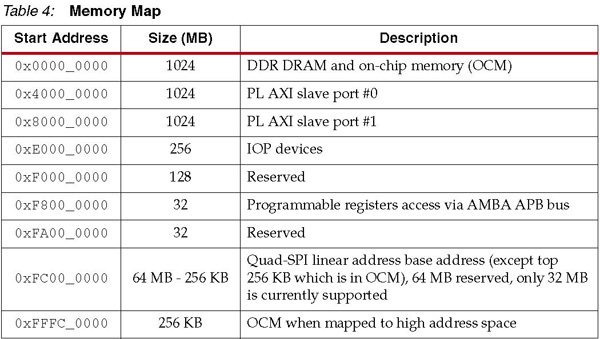

最后的镜像文件在<工程目录>/images/linux/下,fsbl、bitstream以及uboot封装在BOOT.BIN文件中,芯片上电之后即在SD card的第一个分区中寻找这个文件,然后依次加载运行。kernel内核镜像为image.ub中,如果在petalinux设置中不配置根文件系统在SD card那么根文件系统也会在这个镜像文件中,猜测这个镜像会加载到内存中,导致linux运行时对根文件系统的修改断电会丢失。

根文件系统打包在很多个压缩文件中,这里用rootfs.tar.gz。

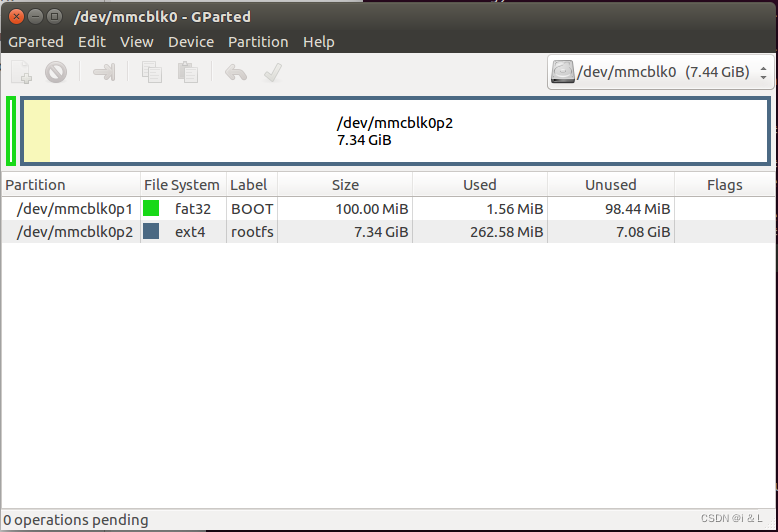

把SD卡挂到Ubuntu里,先对SD卡进行分区,用脚本挺麻烦的,可以用gparted工具来进行分区,‘sudo gparted’。

第一个分区为fat32格式,大小约为100M,能放得下BOOT.BIN和image.ub就行,命名Label为“BOOT”。

第二个分区为ext4格式,可以把SD卡剩下的空间都分进去,命名Label为“rootfs”。

然后在images/linux/文件夹里执行以下脚本:

#!/bin/sh

sudo rm -rf /media/<ubuntu用户>/BOOT/*

sudo rm -rf /media/<ubuntu用户>/rootfs/*

sudo cp BOOT.BIN image.ub /media/<ubuntu用户>/BOOT/

sudo tar -zxvf rootfs.tar.gz -C /media/<ubuntu用户>/rootfs/

sudo umount /media/<ubuntu用户>/BOOT

sudo umount /media/<ubuntu用户>/rootfs

完成后拔出SD卡。

启动

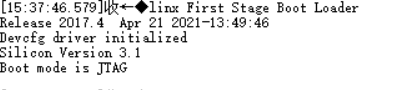

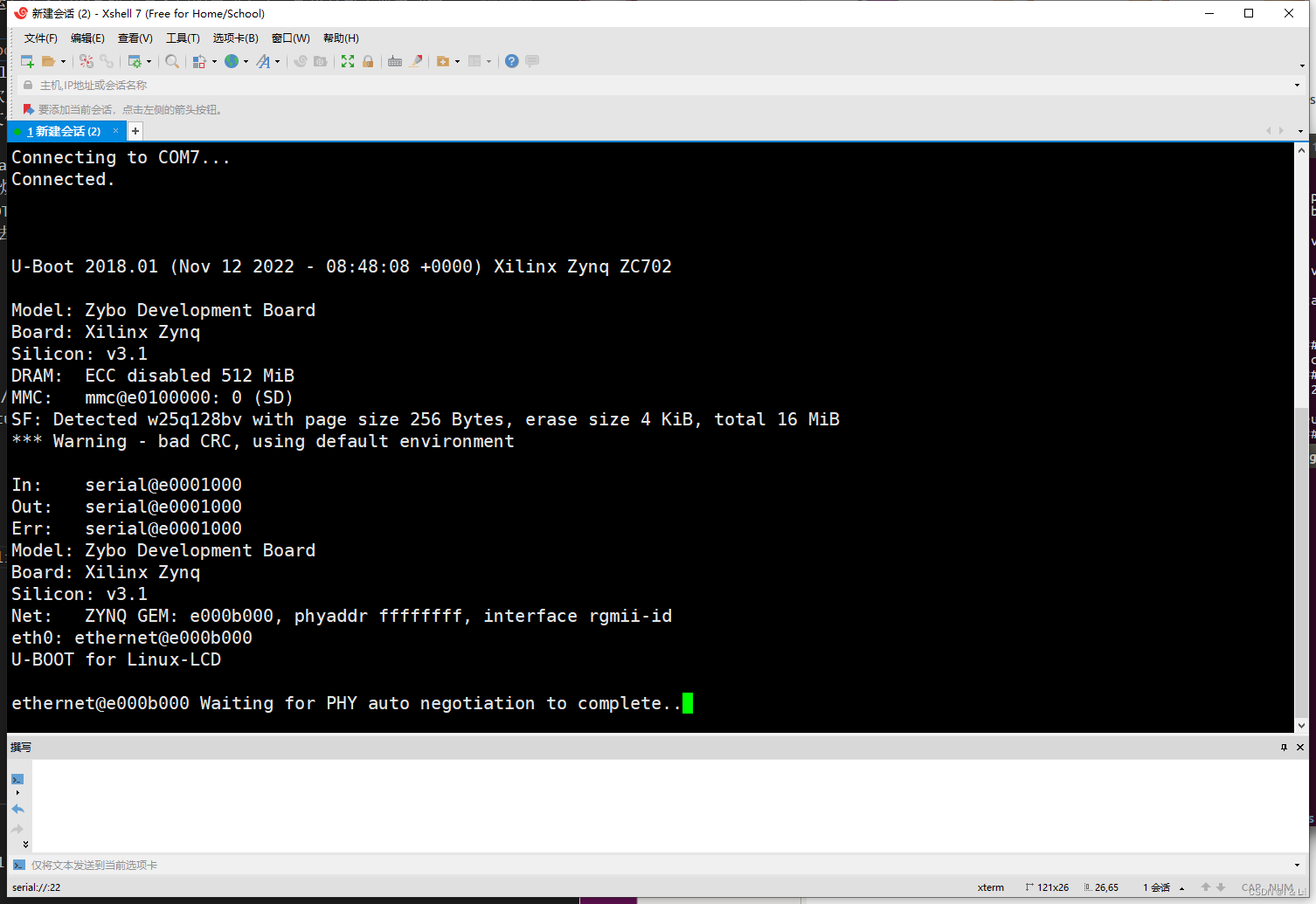

把SD卡插到板子上设置为SD卡启动,上电,如果成功,linux启动串口会打印信息。

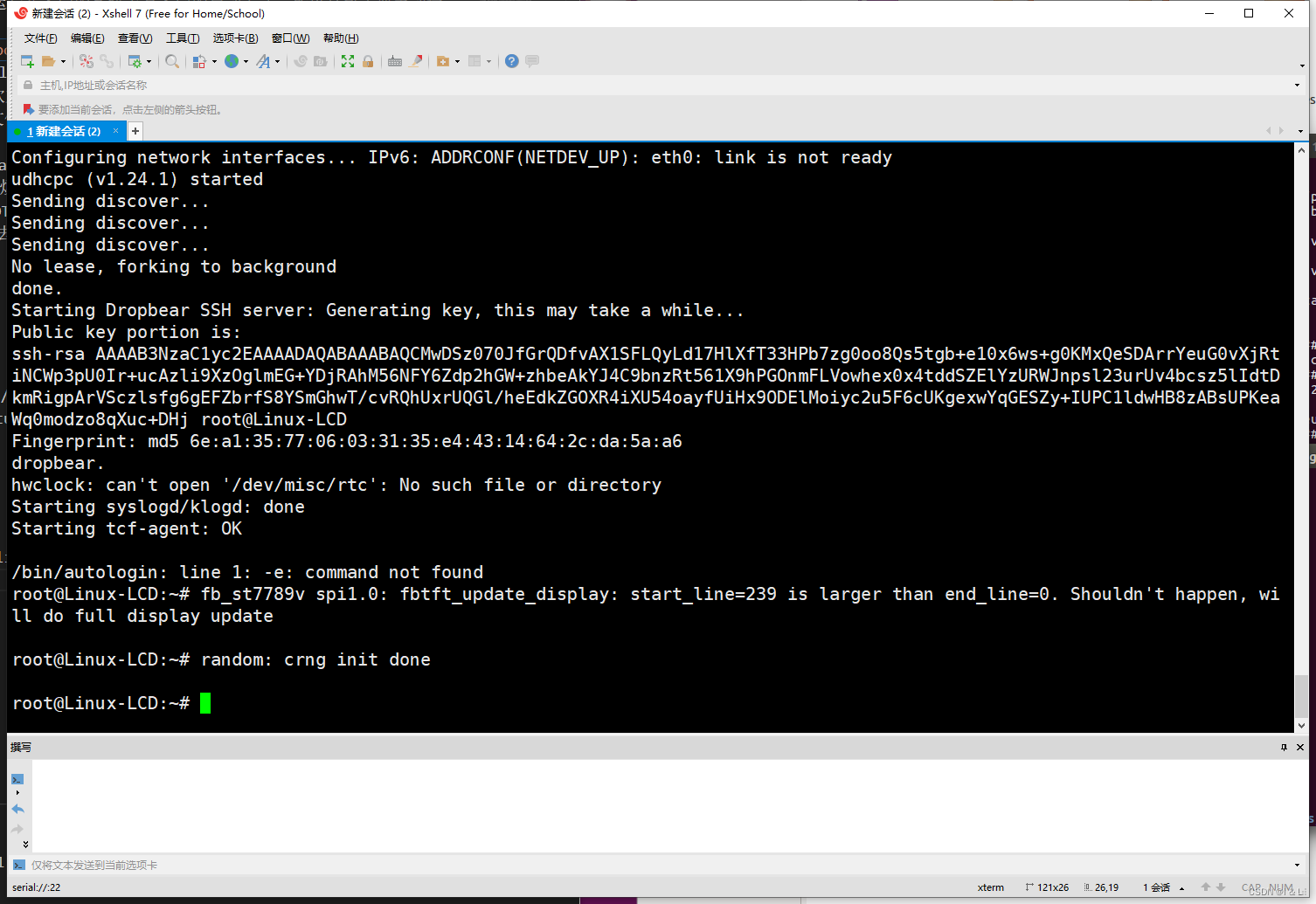

LCD上也会显示命令行运行。

总结

fbtft实现之后,在系统中/dev/下即会出现fb0,即linux系统下的显示器,现在就可以在根文件系统中部署图形界面以及qt、lvgl等应用。