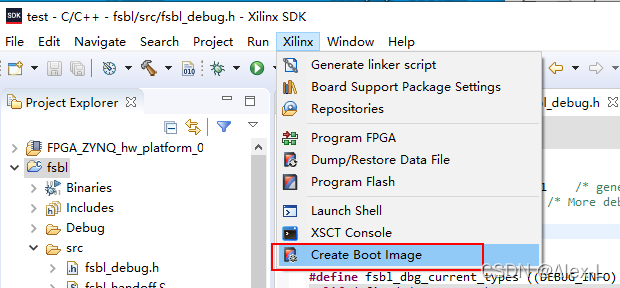

ZYNQ7000固化流程

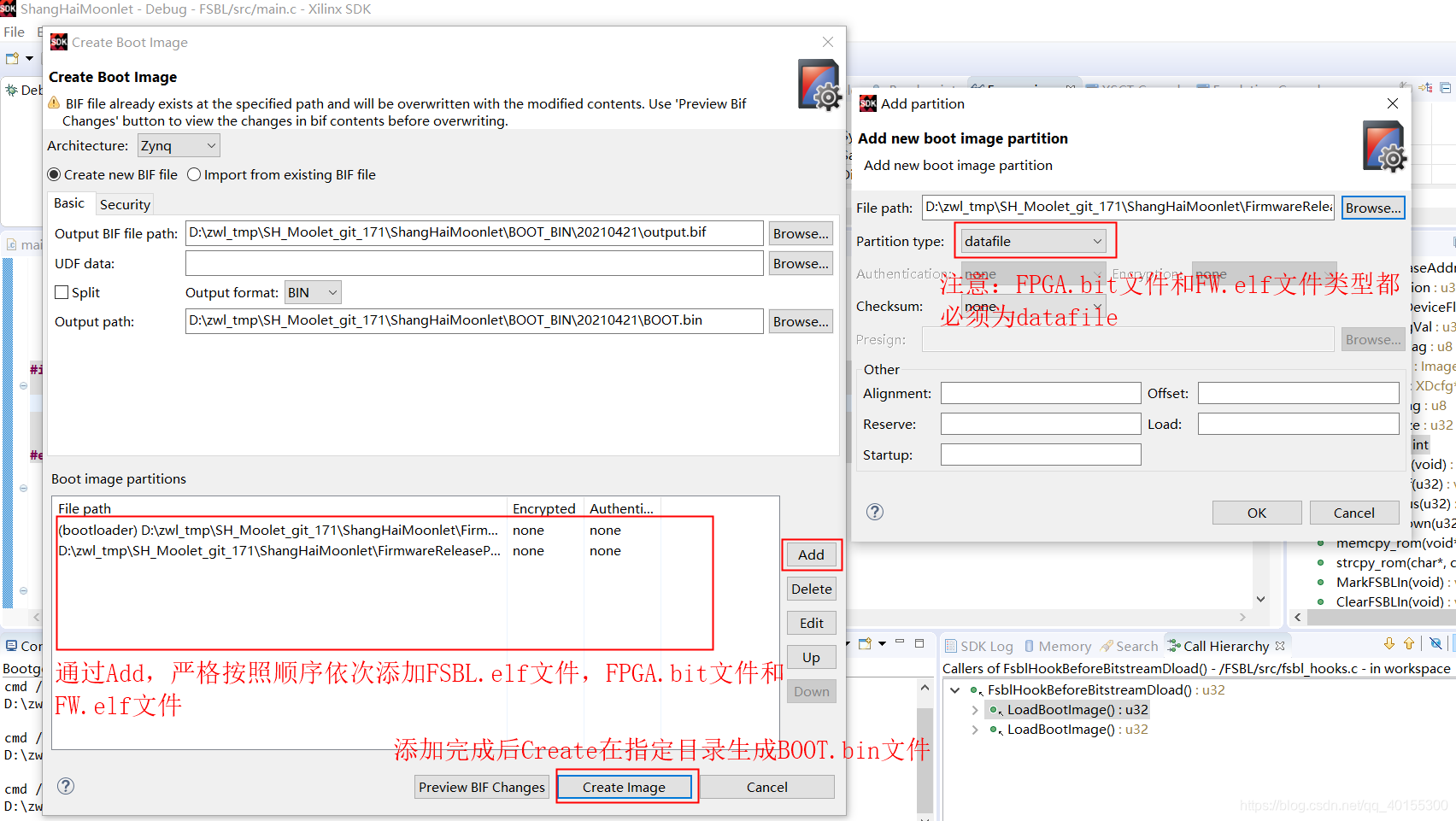

- 生成BOOT.bin文件

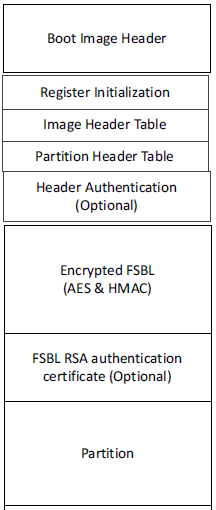

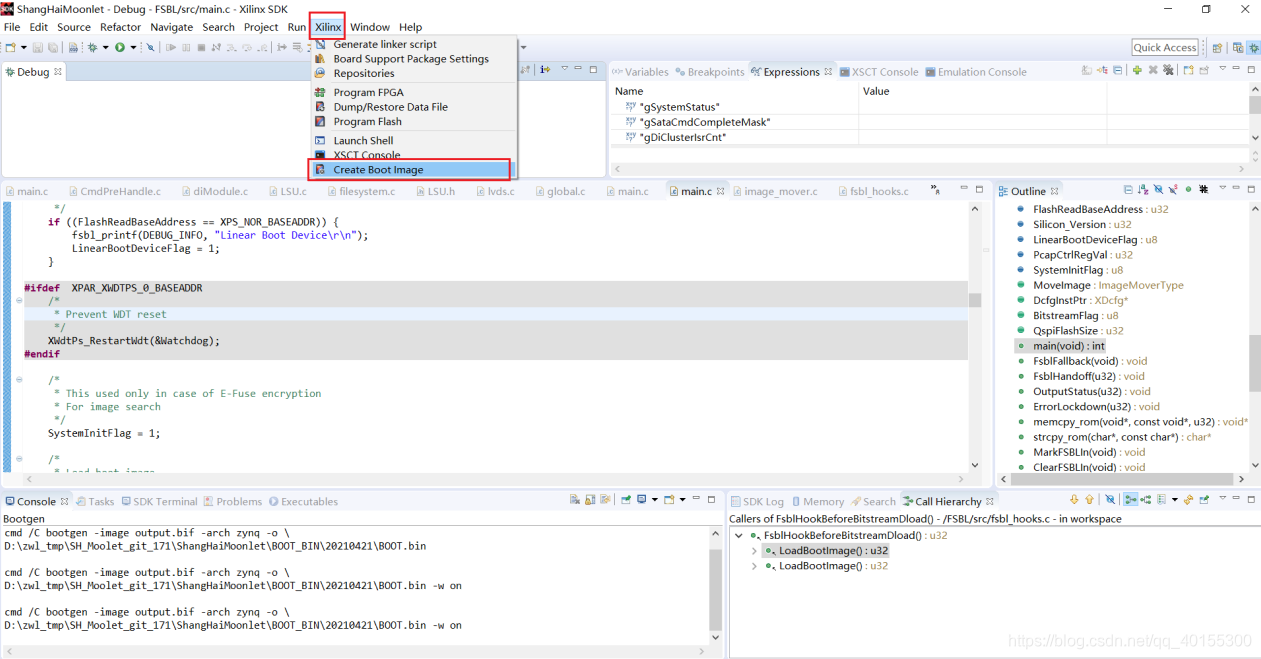

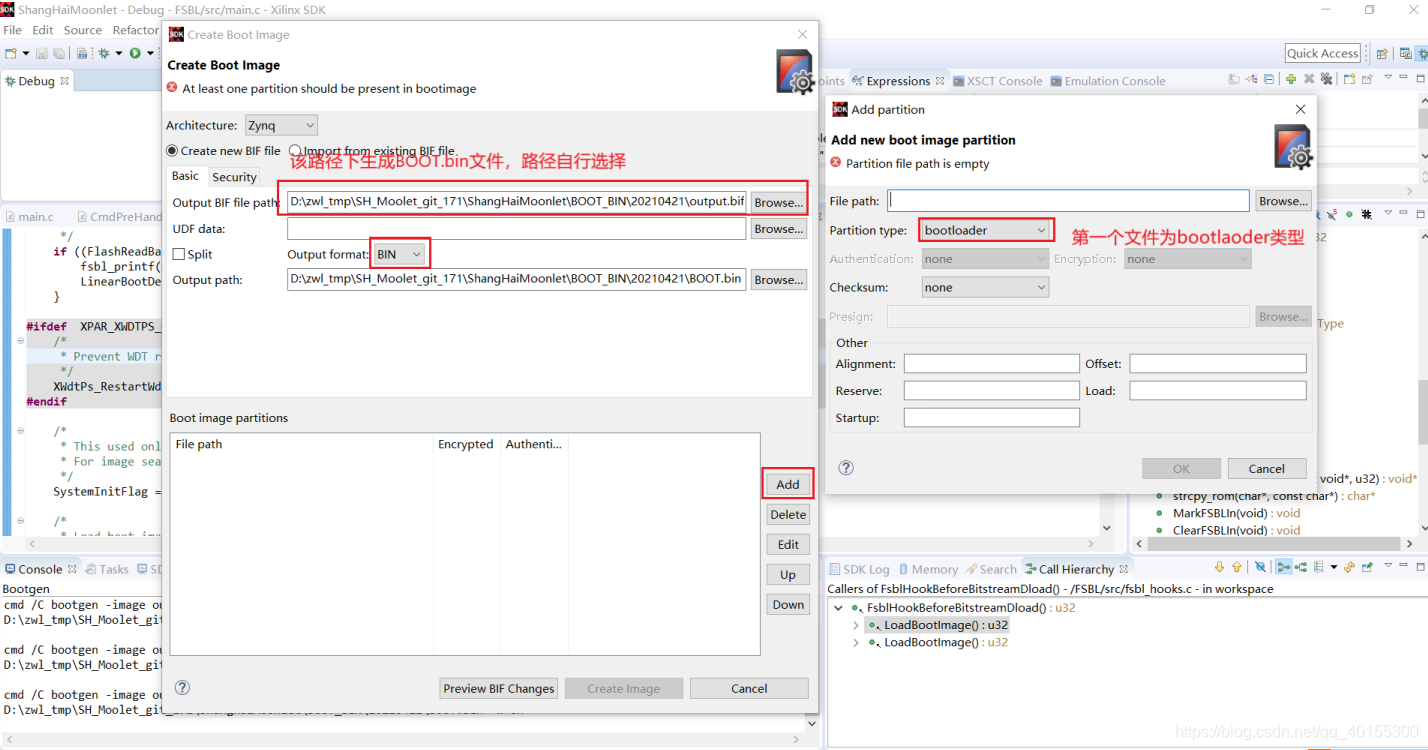

(1)在SDK开发环境下,将FSBL.elf文件,FPGA.bit文件和FW.elf文件按次序添加并打包成BOOT.bin文件

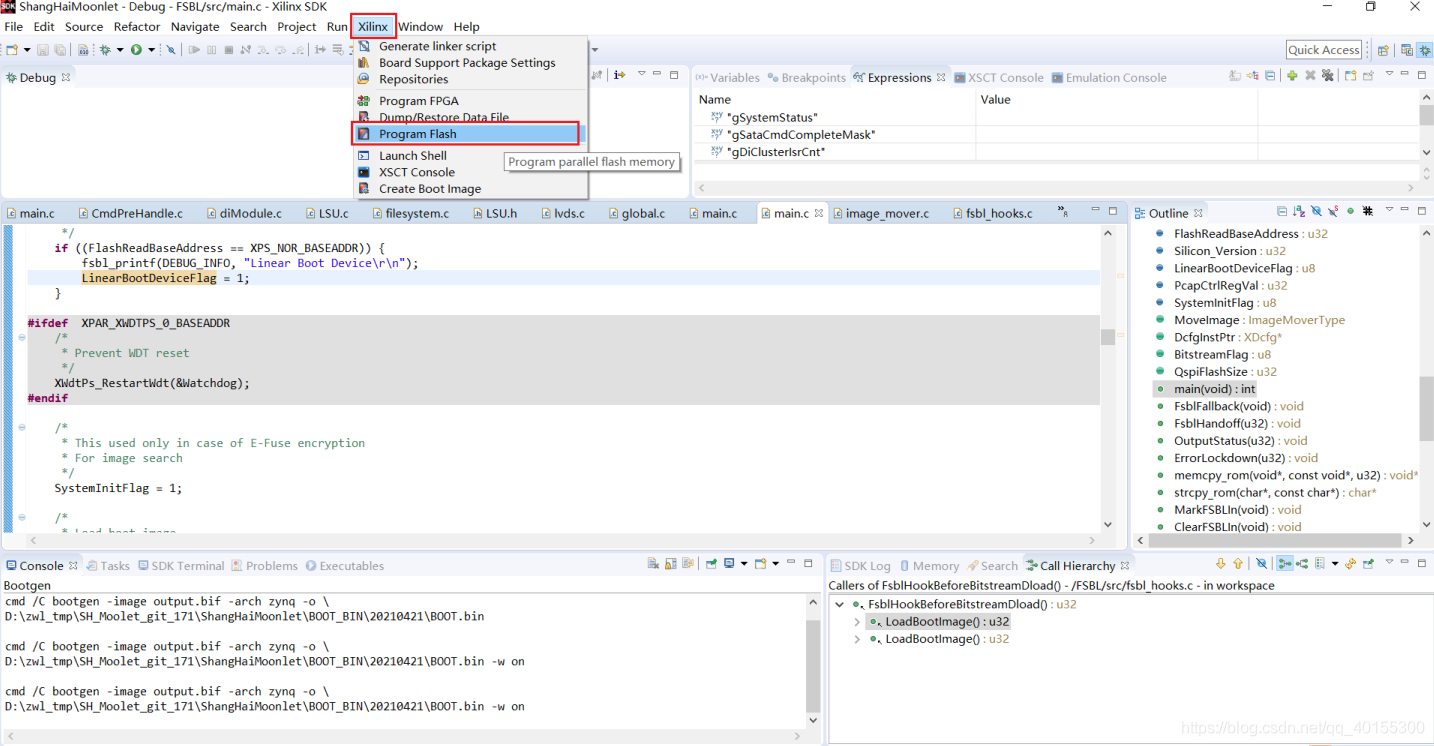

2. BOOT.bin文件固化

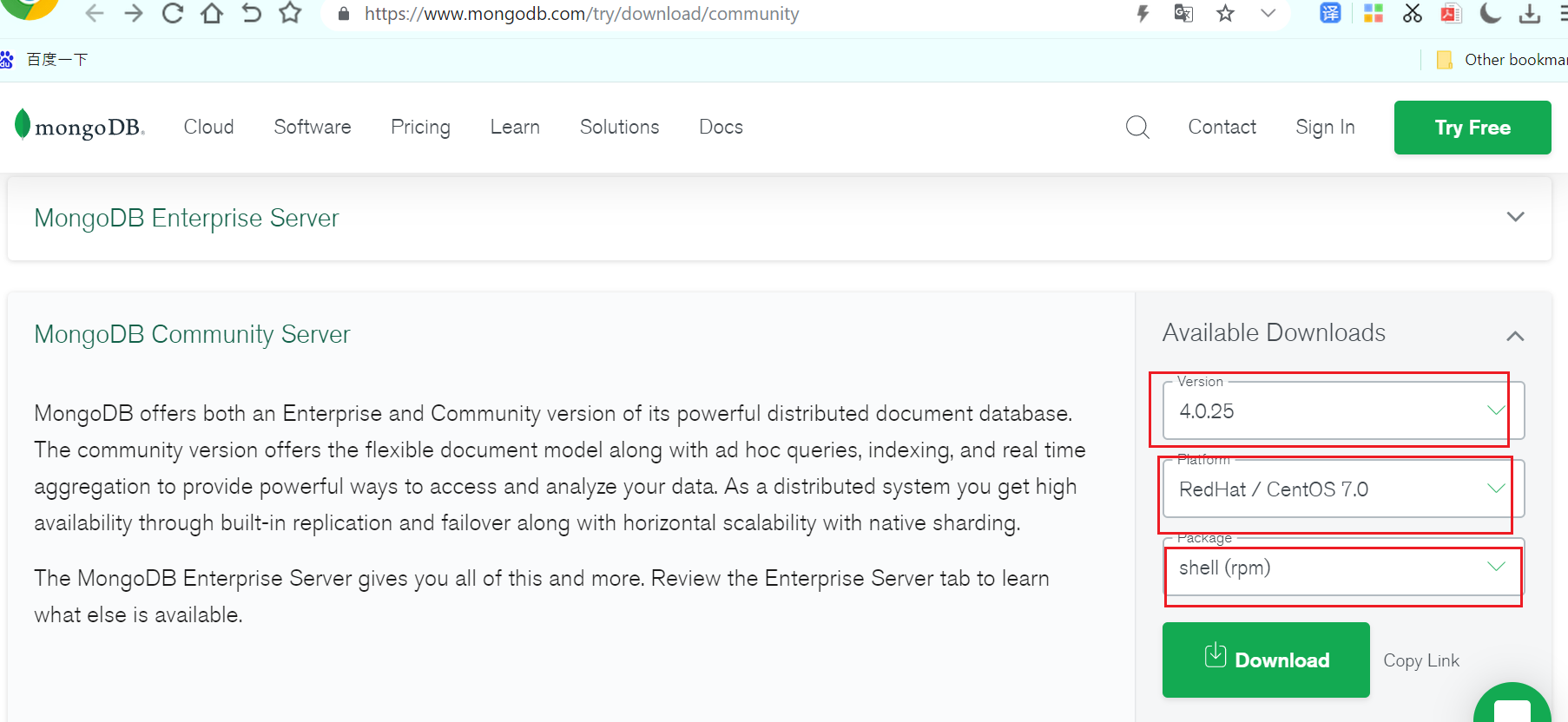

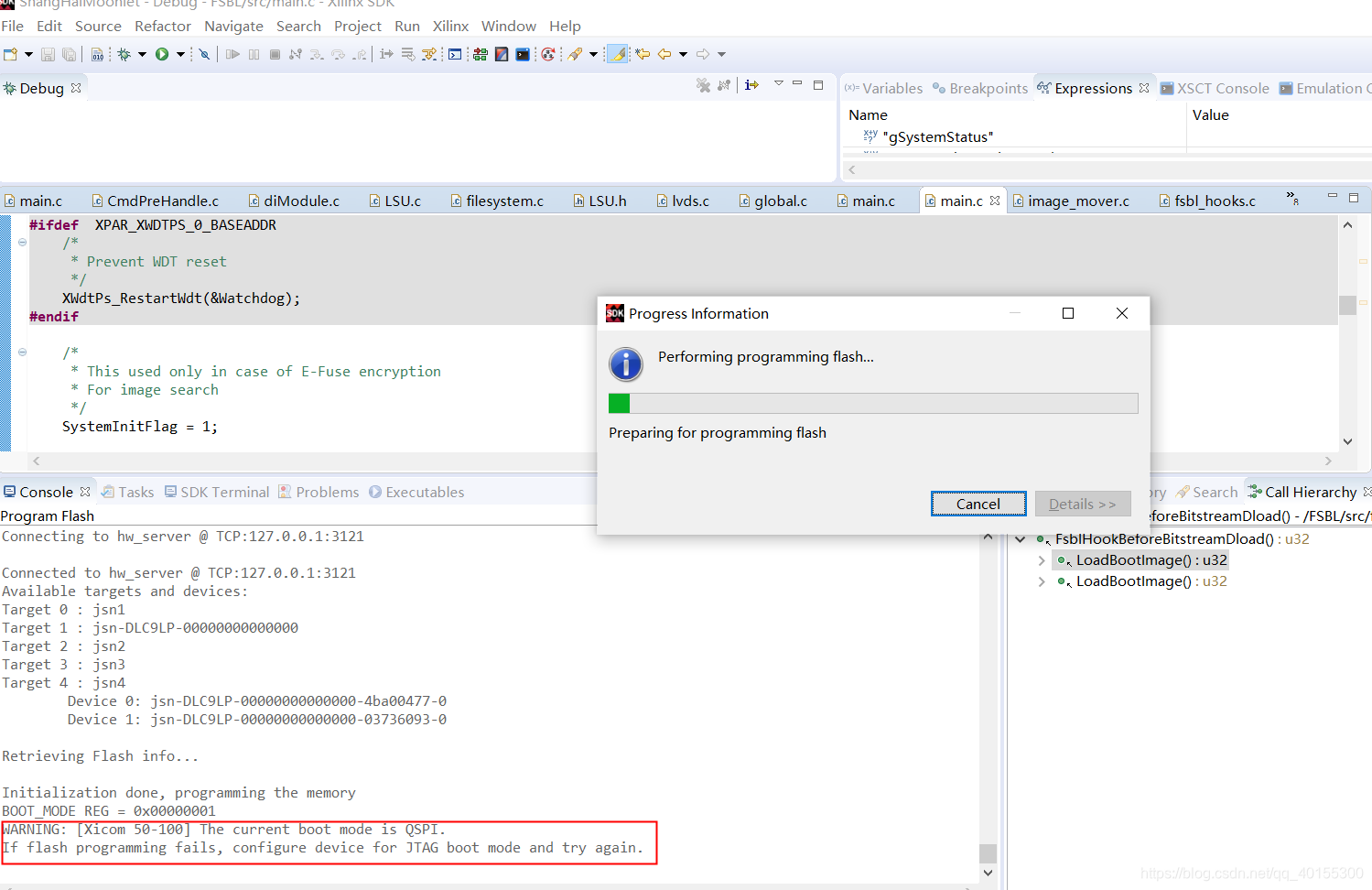

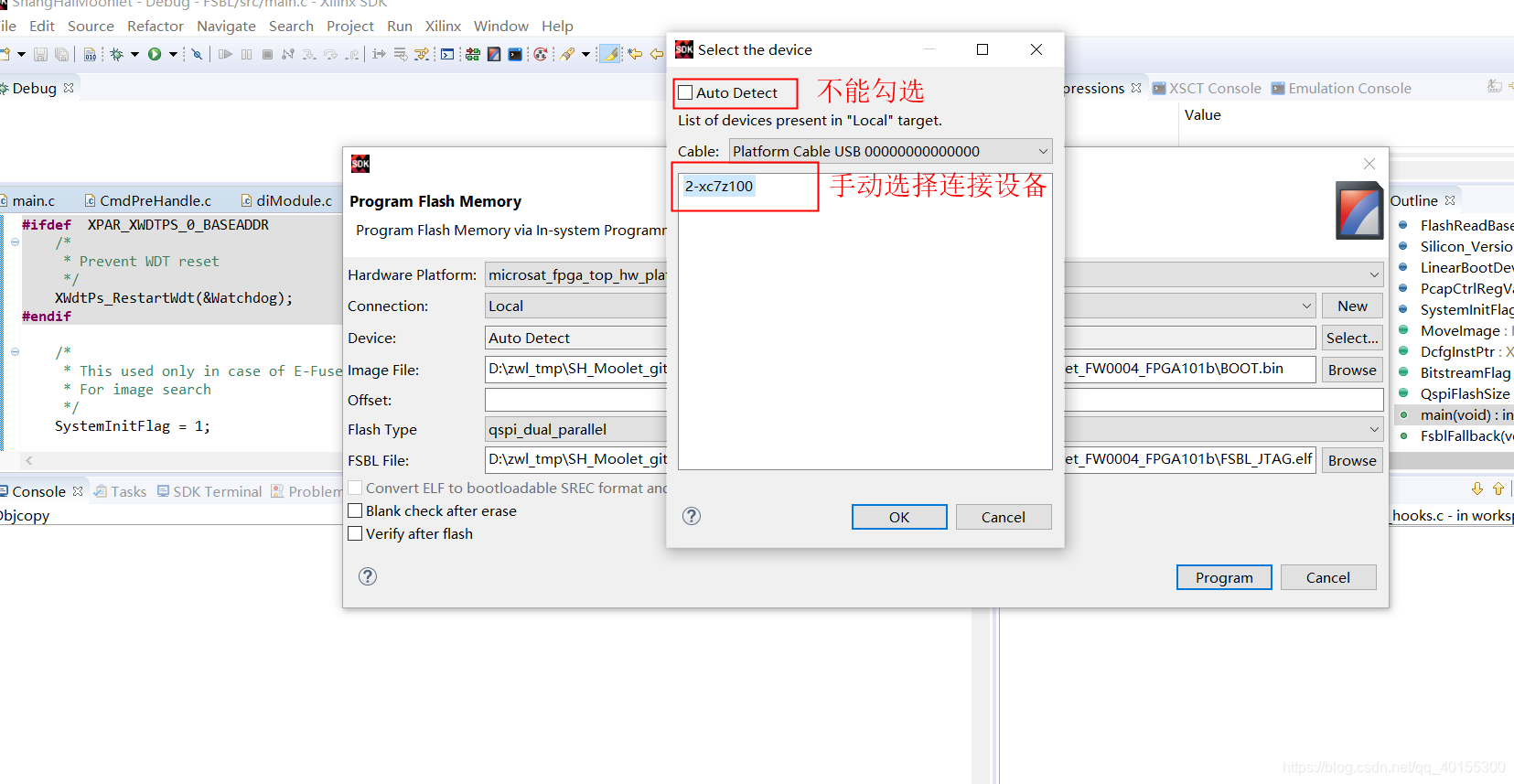

(1)在xilinx SDK环境中通过JTAG进行固化,首先通过选项Xilinx->Program Flash进入到烧写界面

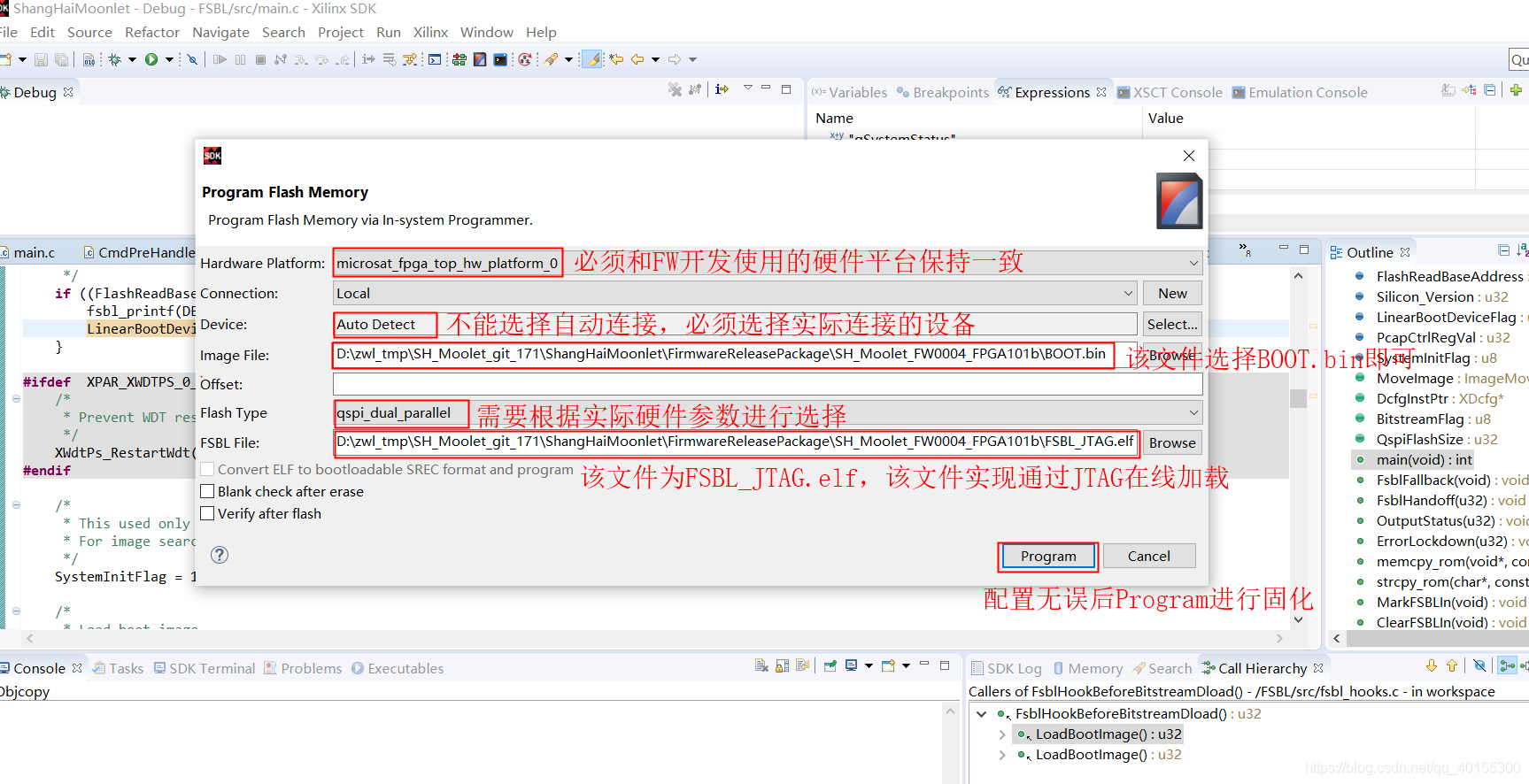

(2)配置并完成固化

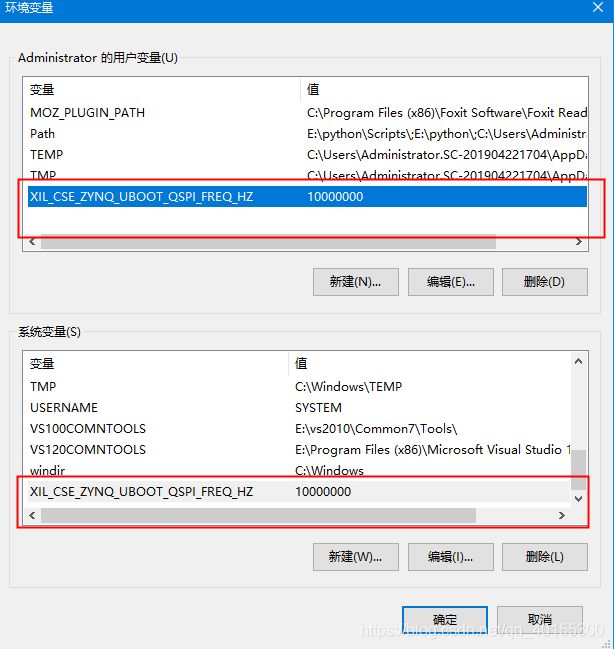

3. 注意事项(仔细阅读)

(1)确保本地电脑环境变量配置正确

(2)生成BOOT.bin时使用的是FSBL.elf文件,固化过程中配置文件为FSBL_JTAG.elf文件

(3)上海小卫星项目中固化前,必须确定跳线帽为JTAG模式,否则固化不能成功

(4)固化配置中连接device不能使用auto detect

(5)固化过程中如果发现卡死,可以尝试采用重新打开xilinx SDK的方式进行恢复

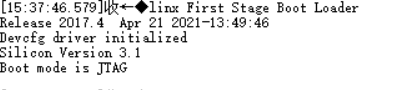

(6)加载成功后首先要确保硬件上跳线帽已经切换为Norflash启动模式,如果为JTAG模式,串口打印log如下:

(7)加载成功后重新上下电就能正常加载,但是必须保证JTAG断开连接,否则会导致无法正常启动

4. 加载全部完成后正常启动串口log如下

[15:42:53.333]收←◆

Xilinx First Stage Bo

[15:42:53.488]收←◆ot Loader

Release 2017.4 Apr 21 2021-13:50:29

Devcfg driver initialized

Silicon Version 3.1

Boot mode is QSPI

Single Flash Information

FlashID=0x1 0x20 0x18

SPANSION 128M Bits

QSPI is in Dual Parallel connection

QSPI Init Done

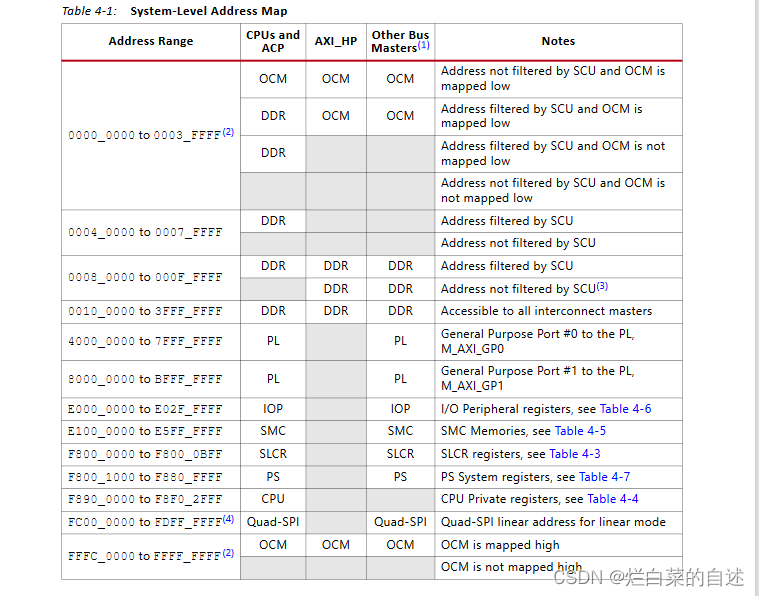

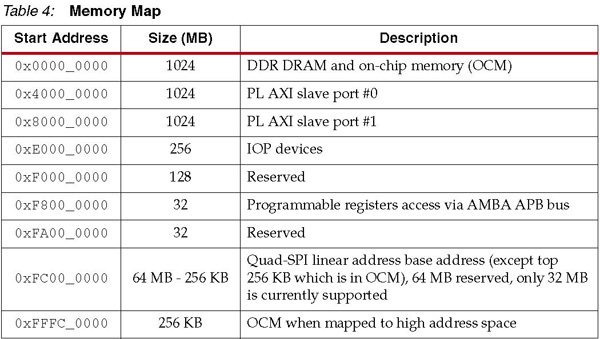

Flash Base Address: 0xFC000000

Reboot status register: 0x60400000

Multiboot Register: 0x0000C000

Image Start Address: 0x00000000

Partition Header Offset:0x00000C80

Partition Count: 3

Partition Number: 1

Header Dump

Image Word Len: 0x00299038

Data Word Len: 0x00299038

Partition Word Len:0x00299038

Load Addr: 0x00000000

Exec Addr: 0x00000000

Partition Start: 0x000055D0

Partition Attr: 0x00000020

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFF82F716

Bitstream

In FsblHookBeforeBitstreamDload function

PCAP:StatusReg = 0x40000A30

PCAP:device ready

PCAP:Clear done

Level Shifter Value = 0xA

Devcfg Status register = 0x40000A30

PCAP:Fabric is Initialized done

PCAP register dump:

PCAP CTRL 0xF8007000: 0x4C00E07F

PCAP LOCK 0xF8007004: 0x0000001A

PCAP CONFIG 0xF8007008: 0x00000508

PCAP ISR 0xF800700C: 0x0802000B

PCAP IMR 0xF8007010: 0xFFFFFFFF

PCAP STATUS 0xF8007014: 0x00000A30

PCAP DMA SRC ADDR 0xF8007018: 0xFC015741

PCAP DMA DEST ADDR 0xF800701C: 0xFFFFFFFF

PCAP DMA SRC LEN 0xF8007020: 0x00299038

PCAP DMA DEST LEN 0xF8007024: 0x00299038

PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF

PCAP MBOOT 0xF800702C: 0x0000C000

PCAP SW ID 0xF8007030: 0x00000000

PCAP UNLOCK 0xF8007034: 0x757BDF0D

PCAP MCTRL 0xF8007080: 0x30800100

...................................................................................................

[15:42:54.714]收←◆

DMA Done !

.................................................................................................

FPGA Done !

In FsblHookAfterBitstreamDload function

Partition Number: 2

Header Dump

Image Word Len: 0x0000C004

Data Word Len: 0x0000C004

Partition Word Len:0x0000C004

Load Addr: 0x00100000

Exec Addr: 0x00100000

Partition Start: 0x0029E610

Partition Attr: 0x00000010

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFFB3D772

Application

PCAP:StatusReg = 0x40000F30

PCAP:device ready

PCAP:Clear done

PCAP register dump:

PCAP CTRL 0xF8007000: 0x4C00E07F

PCAP LOCK 0xF8007004: 0x0000001A

PCAP CONFIG 0xF8007008: 0x00000508

PCAP ISR 0xF800700C: 0x00030004

PCAP IMR 0xF8007010: 0xFFFFFFFF

PCAP STATUS 0xF8007014: 0x00000F30

PCAP DMA SRC ADDR 0xF8007018: 0xFCA79841

PCAP DMA DEST ADDR 0xF800701C: 0x00100001

PCAP DMA SRC LEN 0xF8007020: 0x0000C004

PCAP DMA DEST LEN 0xF8007024: 0x0000C004

PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF

PCAP MBOOT 0xF800702C: 0x0000C000

PCAP SW ID 0xF8007030: 0x00000000

PCAP UNLOCK 0xF8007034: 0x757BDF0D

PCAP MCTRL 0xF8007080: 0x30800110

DMA Done !

Handoff Address: 0x00100000

In FsblHookBeforeHandoff function

SUCCESSFUL_HANDOFF

FSBL Status = 0x1

Firmware Version : SH_Moonlet_FW_VS_00_04

FPGA Version : SHM_FV1.01b

SH_Moonlet Master Firmware Start

[Norflash] init success

[XADC] init success

[LVDS_CMD] init success

[SATA_ARRAY] init success

[ERROR] DI channel up status 0x0

[ERROR] DI lane up status 0x0

[ERROR] DI channel up status 0x0

[ERROR] DI lane up status 0x0

[ERROR] DI channel up status 0x0

[ERROR] DI lane up status 0x0

[ERROR] DI channel up status 0x0

[ERROR] DI lane up status 0x0

[DI Module] init done

[ERROR] DO channel up status 0x0

[ERROR] DO lane up status 0x0

[DO Module] init done

Hardware initialize done

Load SystemInfo from SectorNo = 4, MagicNum = 680

[15:42:54.762]收←◆Software initialize done

All task create done