CGS,代码组同步,ILA,初始化多帧序列帧同步,然后进行数据传输 。

系统复位

在系统复位上:JESD204中提供了一个全局的异步时钟复位,rx_reset用来复位整个系统,AXI4-Lite系统总线复位不受此影响,AXI4-Lite线中带有单独的重置信号,s_axi_aresetn,用来复位和AXI4总线相关的配置寄存器。

在软件复位上:在AXI4-Lite总线中提供了一个寄存器,该寄存器用来复位和软件配置相关的寄存器,用来触发软件相关的逻辑数据路径上的数据路径重置序列,配置寄存器不会受此影响。

在收发器内还提供了一个看门狗定时器,如果长时间不实现同步机制,看门狗定时器会自动提供复位。

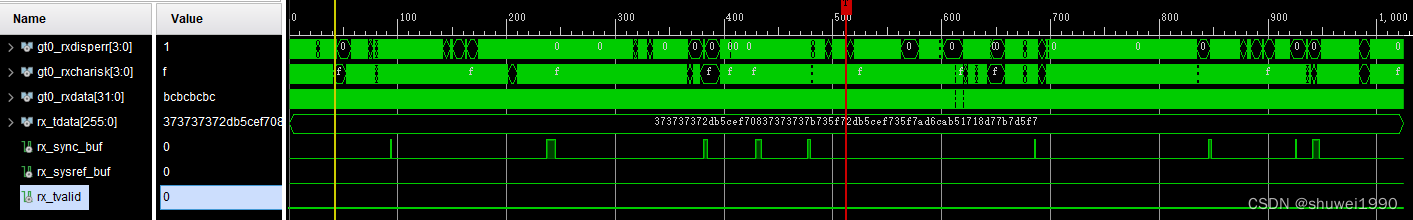

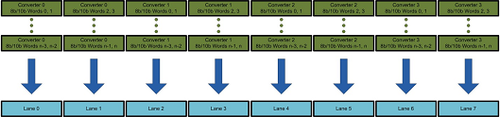

AXI4-Stream数据传输和接受接口用于在JESD204数据格式和Core之间传递数据,在IP设置为传输模式下,数据由Core传递到JESD204 ,在IP设置为接受模式下,数据又JESD204传输到Core,数据的输入输出通道中每个通道每个时钟周期下有4个字节的数据,32位数据,也就是4个字节数据,最低有效字节位传输从AD或者从DA中传输的第一个字节。

Subclass1设备支持确定性延迟操作,链路信号之间的时序关系图如下所示:

确定性延迟

SYSREF是系统的主定时参考,为了实现准确的确定性延迟也就必须同步捕获到核心时钟的SYSREF时钟信号,SYSREF必须是 4字节时钟周期的倍数,默认情况下SYSREF信号在核心时钟的下降沿捕获,以允许时钟的上升沿和SYSREF在设备的边缘对齐。

当JESD204的core使用32位路径也就是4字节数据路径运行时,SYSREF周期必须是多帧周期的整数倍,而且如果多帧周期本身并不是4字节时钟的倍数,它也必须是4字节时钟的倍数。

SYSREF可以在核心时钟的上升沿或者下降沿进行采样,默认情况下SYSREF在核心时钟的下降沿进行采样。

Core_clk是ref_clk还是glb_clk是可选的,同时在SDC中设置时,对捕捉的上升沿和下降沿有确定的建立时间和保持时间,确定采样周期有充足的时间裕量。

采用refclk为core_clk并采用下降沿捕捉SYSREF,其建立时间为1.2ns,保持时间为1.8ns,采用下降沿采样。

采用refclk上升沿采样,建立时间为4.8ns,保持时间为-1.5ns,时序违例??

VIVADO的jesd204IP提供了一个可编程选项可以使sysref长保持为高或者长保持为低。

当长保持为低时,只有在重置时或者链路重新同步链接时才会重新被用来对齐内部的LMFC计数器。

当长保持为高时,所有的sysref事件都被用来重新对齐LMFC计数器,这个设置要求SYSREF周期是多帧周期的正确倍数。

在具体实现时,JESD需要一个初始的SYS信号拉高来同步对齐LMFC然后需要在代码组实现同步时在下一个LMFC边界拉低SYNC。

SYSREF用来LMFC链路重新同步,当SYSREF Required on Re-Sync is set to 0,链路只有在初次同步时需要SYSREF信号来完成同步,后续链路的重新不同不用每次都使用sysref信号来完成重新同步操作,当SYSREF Required on Re-Sync is set to 1也就是每次完成同步时都需要用SYSREF信号来完成同步操作,JESD204B协议要求多帧大小大于链路上可能的最大延迟,只要多帧大小大于链路上延迟的最大变化就可以实现确定性延迟。

JESD204的总体延迟需要考虑跨链接的各种固定和可变延迟源

计算端到端延迟所需的ADC关键参数:

1.SYSREF TO LMFC(T TXLMFC)

2.模拟输入到LMFC的固定延迟。

3.LMFC到JESD204串行输出的固定延迟。

计算端到端时延所需的FPGA端的关键参数:

1.SYSREF到LMFC端的固定延迟。

2.从JESD204输入到LMFC的延迟。

3.固定延迟从LMFC到AXI的数据输出。

总的TX到RX的延迟为T = N*LMFC - TTXLMFC + TRXLMFC:

后面两项的和其实就是两个LMFC之间的差值。

最小的确定性延迟:

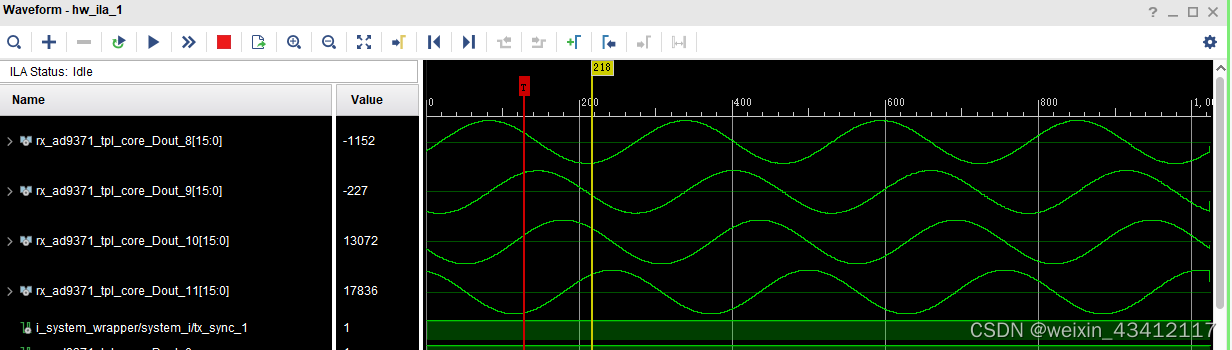

当子类1和子类2设备中首次建立JESD204B链路时,接收端输出的数据如下图:当所有的lane检测到数据后,通过调制buffer_delay的寄存器数量可以支持最小延迟。

确定性延时分为两个方面在TX端从帧的数据输入开始到RX端帧的数据输出截止,在每次上电时或者每次重新连接时其延时是一致和确定的。

在Tx端就是在预定义的时刻所有的lane同时发往ILA数据,预定义的时刻一般指SYNC信号有效后的一个LMFC边界处,也就是说在SYNC信号后指定的几个LMFC边界处开始输出ILA。

在RX端,考虑到从TX端过来的数据经过物理延迟,和每条lane之间必然存在着不确定性的延迟,所有在RX端有必要准备一段缓存,数据进来后先进入缓存,然后经过指定的时间后从缓存中读取数据,也就是在一个预定义的时刻读取数据,通常预定义的时刻是可以被编程定义的。

由此可见要想实现RX端和TX端的同步很有必要的一点就是实现LMFC的对齐,Xilinx手册保证确定性延时最小的情况下给了如下的准则:

Multiframe的长度必须大于Link之间的最大的偏差。

RBD*Tf的值必须大于link之间最大的偏差,Tf指帧周期

RBD的深度为[1:k],其中K为多帧中包含的帧数量。

另外要实现确定性延迟在Rx端还要保证能够缓存所有的ILA帧序列和信息数据,也就是说要整RXbuffer一般要足够大能够缓存一次多帧序列的数据,然后在指定时间同步释放从而保证数据输出时间相同达到同步效果。

如果ILA数据会通过RX elastic buffer,则“有效数据”是指ILA序列;如果ILA数据不通过RX elastic buffer,则“有效数据”是指ILA序列之后的第一个采样数据。当ILA数据不通过RX elastic buffer时,RX elastic buffer的释放时刻应该在上文提到的“第RBD个frame clock时钟周期”之后,再延时4个multiframe周期。(因为subclass 1的ILA就包含4个multiframe,RBD延时之后应该是开始处理第一个ILA的时间,处理完ILA后才能释放采样数据。

DELAYlink = ΔTLMFC = TXdelay + LANEdelay + RXdelay

其中各个变量的定义如下。

TXdelay:从TX端ILA并行数据的产生(该行为对齐于某个LMFC边界)到ILA数据出现在serdes输出端口的这段时间。

LANEdelay:指lane之间的延时。

RXdelay:从输入数据出现在serdes输入端口到RX elastic buffer释放。

ΔTLMFC:从ILA/用户数据被写入到link时所对应的LMFC上升沿开始,到ILA/用户数据出现RX elastic buffer的输出端口处为止的时间差。

RX elastic buffer的最小深度等于:从第一个数据到达RX elastic buffer开始,直到第一个数据释放为止,即LMFC边界后的第RBD个frame clock周期。也就是RBD个frame的深度。

subclass1同步机制

在Subclass1模式中主要通过sysref信号实现同步机制,因此要求SYSREF信号必须分配到每个设备当中。在具体的同步实现当中保证设备时钟和SYSREF信号的高精度就能够保证最小化确定性延迟,因此Xilinx建议所有的SYSREF信号来自同一个芯片从而保证高度精准。

因此Subclass1模式下的对各设备有如下要求:

对RX端要求能够具有generated sysref的能力也就是根据重同步信号发出sysref信号的能力,该信号发送到JESD的各个模块当中实现同步机制,

TX和RX设备能够决定是否响应第一个SYSREF之后的其他SYSREF脉冲,并根据该脉冲对本地帧和多帧时钟进行相位对齐。根据规范,TX和RX设备一般会提供以下选项。

检测每一个SYSREF脉冲,如果当前LMFC和frame clock需要进行相位调整,则进行相应的相位调整。

通过一个输入管脚,或者通过配置接口发送配置命令来控制设备,使其在接收到后续SYSREF时对LMFC和frame clock进行强制相位对齐。

通过一个输入管脚,或者通过配置接口发送配置命令来控制设备,使其忽略后续的所有SYSREF。

上述情况只有在设备已经完成初始化并发送了重同步请求,或者link发现错误并发送了重同步请求的情况下才会发生。此外,subclass 1设备应该给出以下时序参数:

从采样到SYSREF脉冲的Device clock的上升沿,到LMFC上升沿之间的延迟。

如果需要确定性延时等于一个multiframe周期,需要将RBD的值设置为K。下图描述了这种延时的实现过程。

图中上半部分为TX设备,下半部分为RX设备。TX设备一直在发送K码。当TX设备监测到SYSREF之后应该产生本地的LMFC,TX设备需要给出从检测到SYSREF的device clock的上升沿,到下一个LMFC之间的延迟参数。该延迟应该是一个确定的值。

RX设备的所有lane能够正确接收K码之后,会将在下一个LMFC上升沿后撤销SYNC信号(SYNC低有效)。当TX设备检测到SYNC撤销后,会在下一个LMFC上升沿开始发送ILA。

由于不同lane延时不同,RX设备中每个lane收到ILA的时间有差异,但是这些ILA都被elastic buffer缓存。当RX端检测到所有lane都接收到ILA启动信号后(即所有lane都至少检测到R码),将会在下一个LMFC开始同步释放elastic buffer。

最后需要提一下的是,上图是基于TX端和RX端的LMFC严格对齐的前提。如果两者的LMFC有偏差,自然也会导致延时出现一定的偏差。

当需要确定性延时小于multiframe周期时,需要将RBD值设置为小于K的值。

同样假设TX和RX端的LMFC对齐。该例中,RBD设置值小于K。这样elastic buffer才有可能提前释放缓冲区。

当RX端所有lane都完成组同步后,将在下一个LMFC上升沿撤销SYNC。紧接着TX设备检测到SYNC撤销,并且在下一个LMFC开始发送ILA。RX设备的所有lane将会检测ILA起始信号。

在LMFC上升沿后的RBD个frame clock周期后,正常情况下RX设备的所有lane应该都检测到了ILA的起始信号,此时会同步释放elastic buffer。这种情况下,确定性延时等于RBD个frame clock周期。