phy处于physical层,上一层是data link层:MAC,两者通过xMII和MDIO接口通信。

xMII

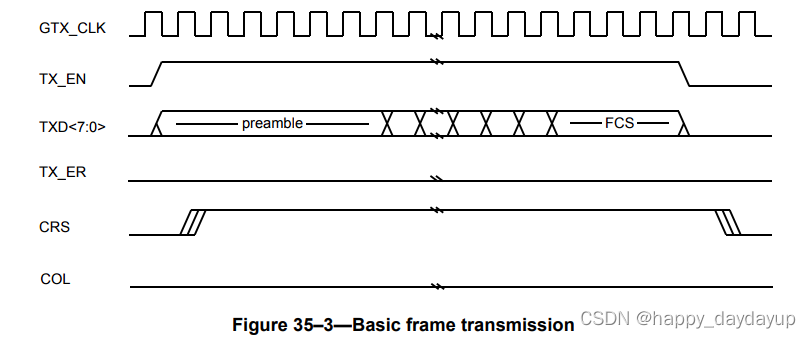

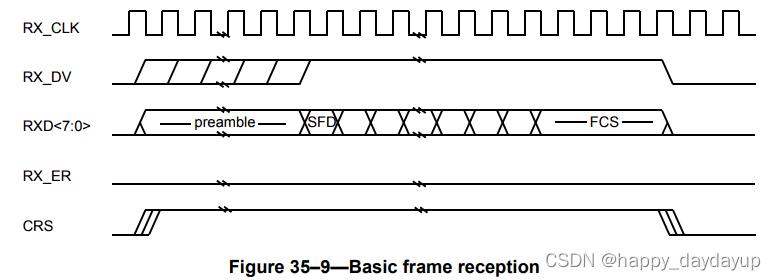

XMII包含MII(802.3 sec22,适用于10M和100M传输),GMII(802.3 sec35.2.2,适用于1000M传输),RGMII(GMII的简化版)等,用于传输Ethernet frame和相关状态信号,分为tx和rx两路,basic frame transmission如下:

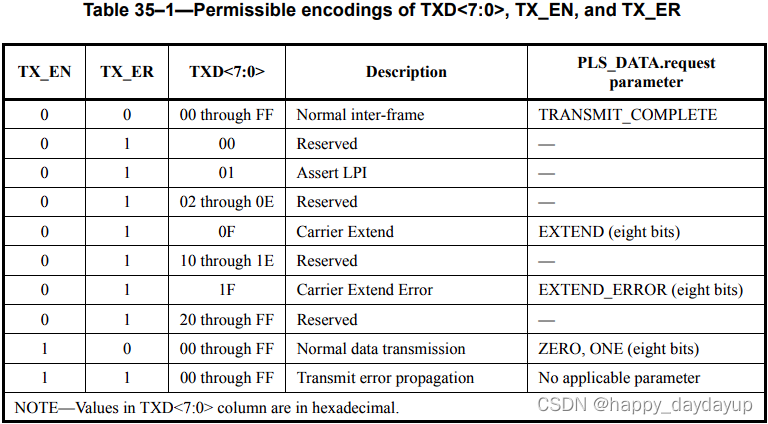

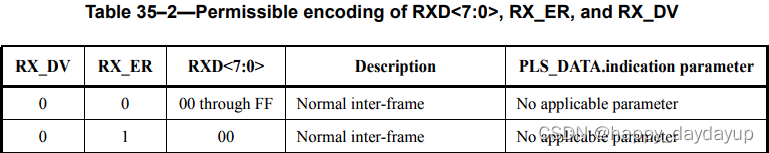

不同的信号组合具有不同的意义:

ethernet frame

MDIO

MDIO是mac用于配置phy的reg的接口。

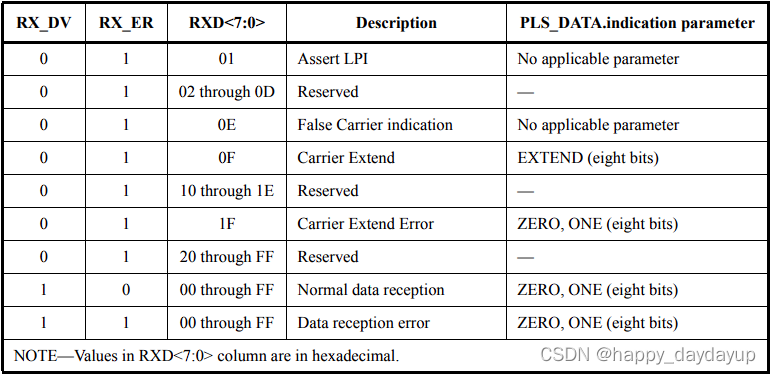

百兆phy的reg((sec 22.2.4)如下,包含control,status,AN,MMD等。1000BASET的reg见sec40.5.1.1。control包含复位,速度,全/半双工,AN,loop back等,status包含link状态等。

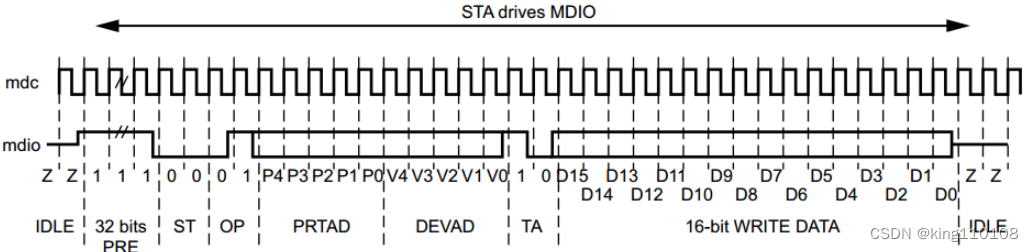

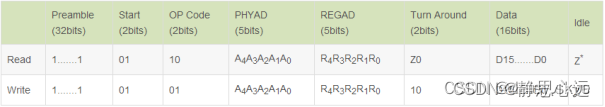

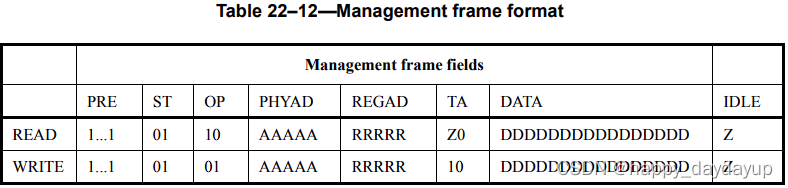

MDIO(sec22.2.2.13)包含上升沿时钟mdc和inout型数据mdio,mdio按下表传输进行reg的读写。

MMD

sec22.2.4.3.11 & sec45.2.8

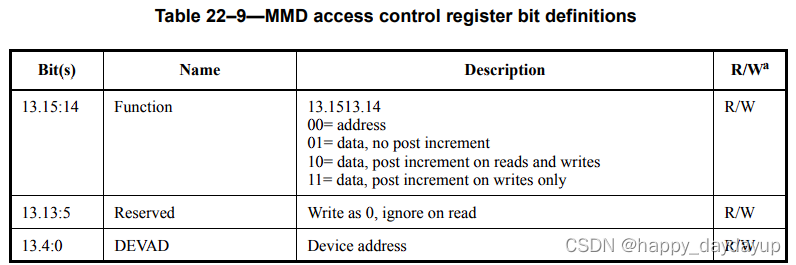

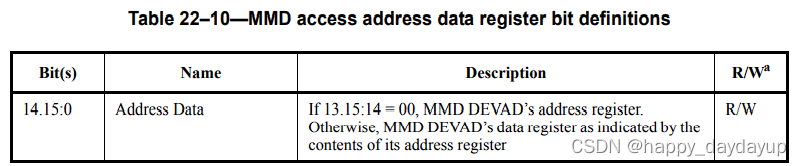

MMD:MDIO manageable device,一种拓展reg访问空间的机制,类似于间接访问。

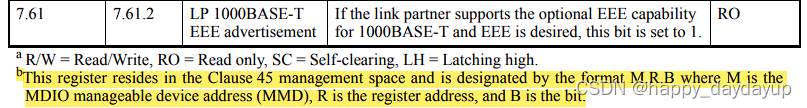

MMD访问的reg格式为M.R,如下所述,M为MMD,r是reg地址。(称之为shadow reg,在rtl中对应的reg名为sh07_61)。

MMD使用两个reg:MMD access control register (Register 13)和MMD access address data register (Register 14),先通过MDIO配置reg13,给出控制信息和device addr,再配置reg14给出响应数据/地址。比如写7.61reg:写reg13=00<<14 | 7,写reg14=61,再写reg13=01<<14 | 7,然后写reg14=xxx写入值。

AN

sec28:10M&100M,sec40.5.1:1000M

AN:auto-negotiation,用于不同end间自动选取最优工作模式。不同的Phy可能支持不同的speed,duplex,要想协同工作,要么手动设置相同的工作模式,要么开启AN进行自协商,确定最优的工作模式。

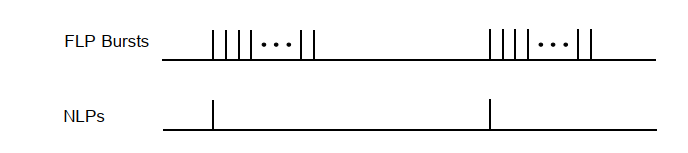

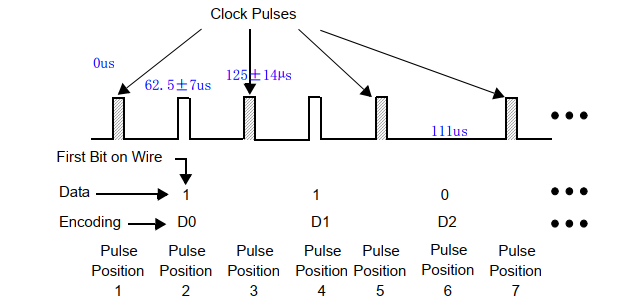

AN主要利用FLP进行信息交互,而FLP利用了NLP。NLP(normal link pulse)是10BASET中data transfer处于idle状态时的Link test pulse信号,间隔16ms ± 8ms。FLP则将clk和AN传输的data编码进一簇一簇的脉冲里,脉冲簇与簇的间隔等于NLP的间隔,簇内的pulse间隔则为62.5us ± 7us。

FLP burst encoding

一个FLP由clock和data交互出现,共33个脉冲(也有扩展FLP,共97个脉冲,不清楚用在哪)。

脉冲间隔,簇间隔,脉宽等都有限制,据此可以在接收时提取需要的信息@sec28.2.2.1。

Link codeword encoding

将FLP中的的data提取出来共16bit,组成base page,@sec28.2.1.2

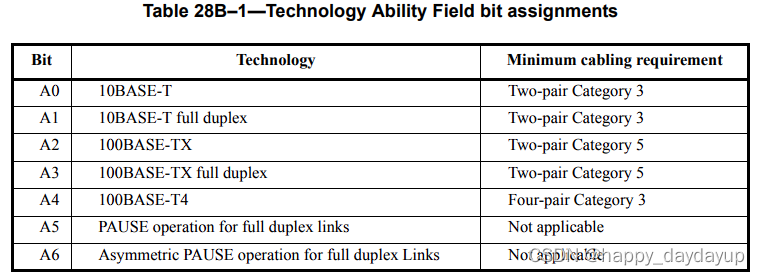

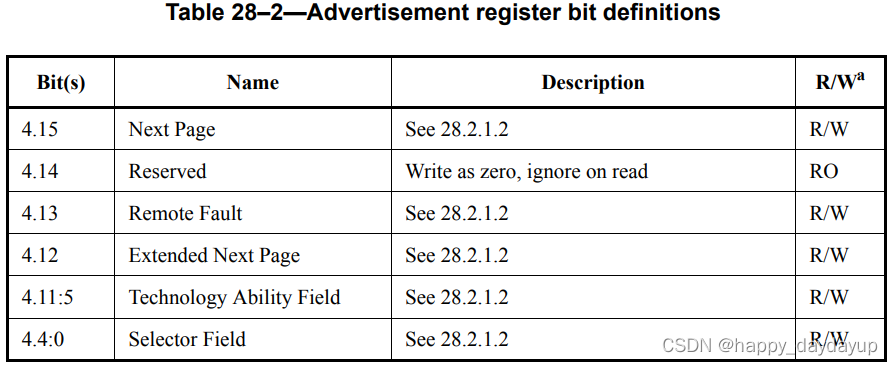

其中,selector field在此为802.3,XNP是extended next page,RF是remote fault,Technology Ability Field,为支持的ability,@Annex 28B.2 & Annex 28D.5

这些发送的ability来源于Auto-Negotiation advertisement register (Register 4) @sec28.2.4.1.3,接收到的对端的ability则存储在Auto-Negotiation Link Partner ability register (Register 5)。

信息交换可能需要额外的page,这就涉及到XNP和NP了,@sec28.2.3.4。

ACK则用于信息传输的握手:

If no Next Page information is to be sent, this bit shall be set to logic one in the link codeword after the reception of at least three consecutive and consistent FLP Bursts (ignoring the Acknowledge bit value). If Next Page information is to be sent, this bit shall be set to logic one after the device has successfully received at least three consecutive and matching FLP Bursts (ignoring the Acknowledge bit value), and will remain set until the Next Page information has been loaded into the Auto-Negotiation Next Page transmit register (Register 7).这个matching的意思是?

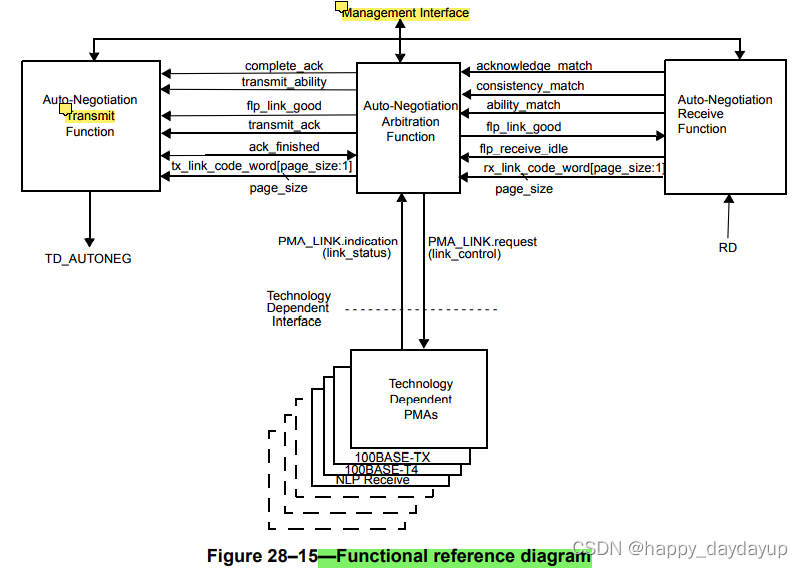

整个AN的state diagram见sec28.3,简单总结:

- 不断的向对端设备发送FLP_burst,包含base_page信息,同时不断接收对端的FLP脉冲。

- 在收到一定次数的base_page并确认连续性后拉高对应的ACK bit位,向对端回复ACK。

- 在完成双方的ACK握手后,对接收到的base_page乃至next_page进行解析,确定最高的共同优先级。

parallel detection function:此功能用于对接不支持AN的phy,通过NLP Receive Link Integrity Test来检测10BASE-T的PMA,或者通过检测100BASE-T的idle来识别。由于对端phy不发送ability信息,所以对接不支持AN的phy时,local phy只能开启half deplux模式。

next page function: optional, 在base page之后,共4种:Message Pages, Unformatted Pages, extended Message Pages, and extended Unformatted Pages.是否支持next page是由mac配置的reg5 ability reg决定的:

next page开始于base page交换完成之后,结束于两端都不再有next page时(如果一端有,另一端无,则无next page的一端发null message的page)。

If the Selector Field values do not match, then each series of Unformatted Pages shall be preceded by a Message Page containing a message code that defines how the following Unformatted Pages will be interpreted. If the Selector Field values match, then the convention governing the use of Message Pages shall be as defined by the Selector Field value definition.

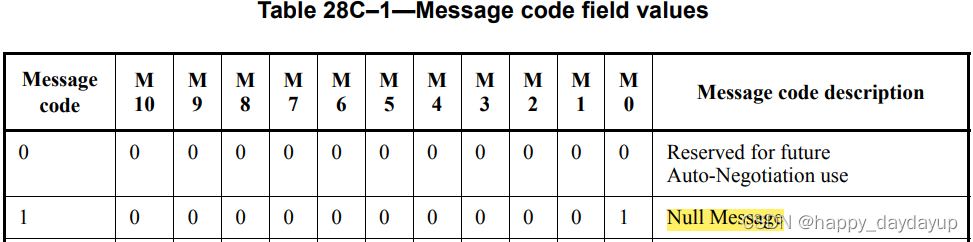

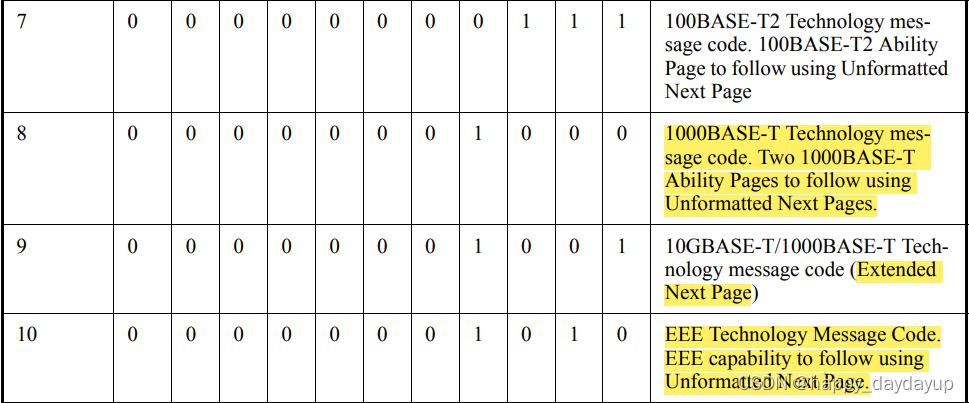

Annex 28C给出了message page里字段含义,此字段指定了后续的unformatted page如何解析:

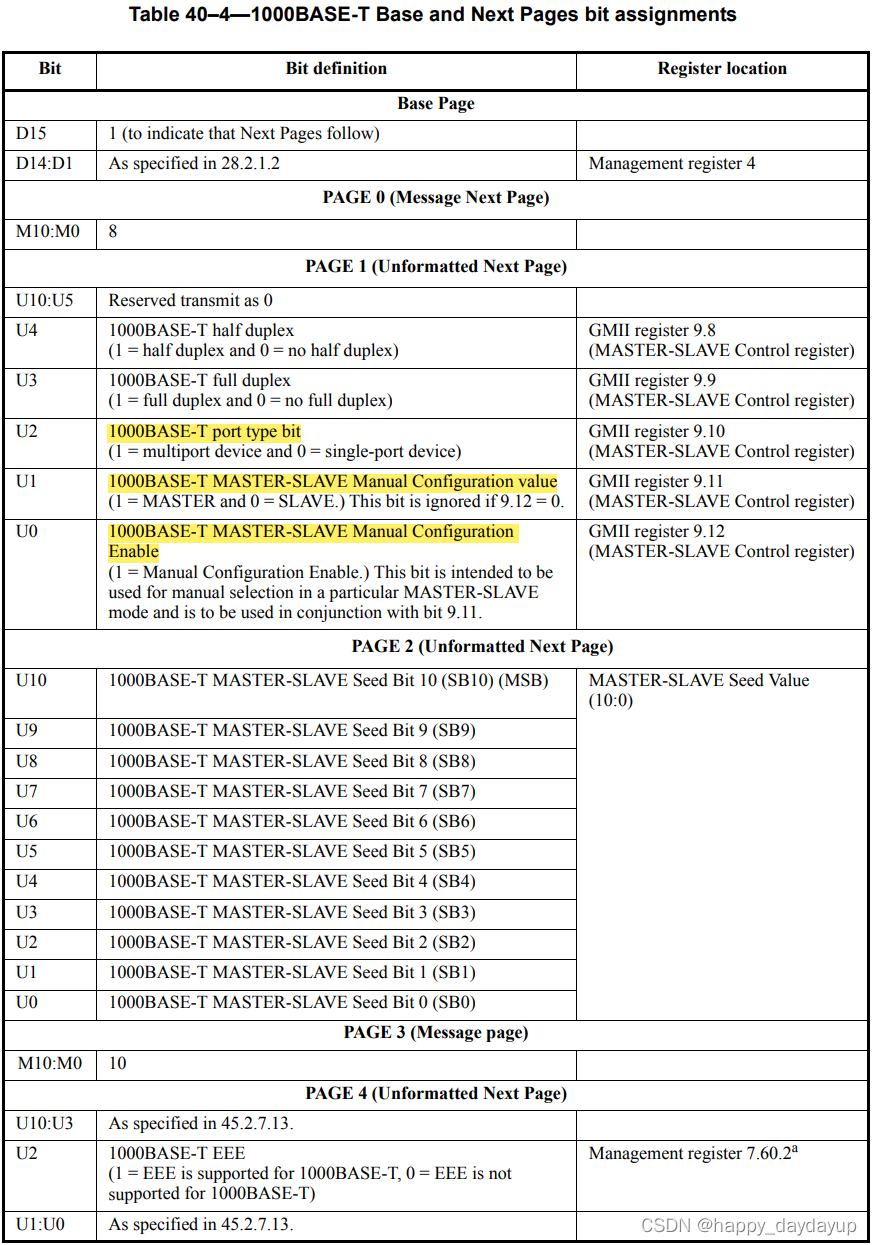

比如AN支持1000BASE-T时,会发送message code=8的mp和后续的up,支持EEE时,会发送mc=10的mp和后续的up @sec40.5.1.3:

比如AN支持1000BASE-T时,会发送message code=8的mp和后续的up,支持EEE时,会发送mc=10的mp和后续的up @sec40.5.1.3:

extented next page: 目前还没看到在哪用。

AN相关的reg @sec28.2.4.1。

LPI

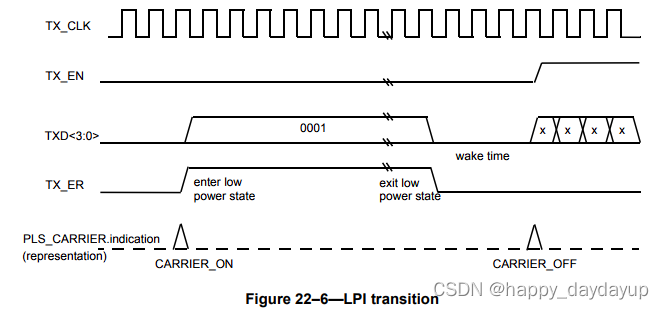

LPI: low power idle,低功耗模式,支持Energy-Efficient Ethernet (EEF)的phy可以由mac发起进入LPI模式,mac通过xMII信号控制phy。

支持EEE的phy在pcs的state diagram中会有不同,100BASE-T@sec24.2.4.4,1000BASE-T@sec40.3.4,在pma的link monitor中也会有所不同,100BASE-T@sec24.3.4.4,1000BASE-T@sec40.4.6。10BASE-T不支持EEE。

下文开始介绍不同速度的phy的pcs和pma,包括10M,100M,1000M的,数字表示速度Mbps,BASE表示Baseband(基带信号),1根线缆只传输1个信号,T是传输媒介,twisted pair。

| 类型 | 编码 | 时钟 |

| 10BASE-T | Manchester | 2.5MHz |

| 100BASE-T | 4B/5B+MLT3 | 25MHz |

| 1000BASE-T | 4D-PAM5 | 125MHz |

10BASE-T

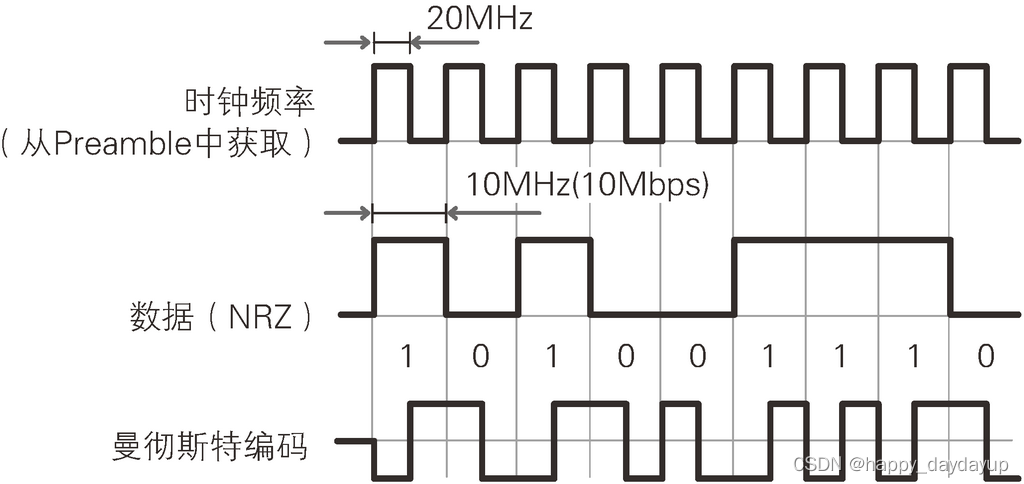

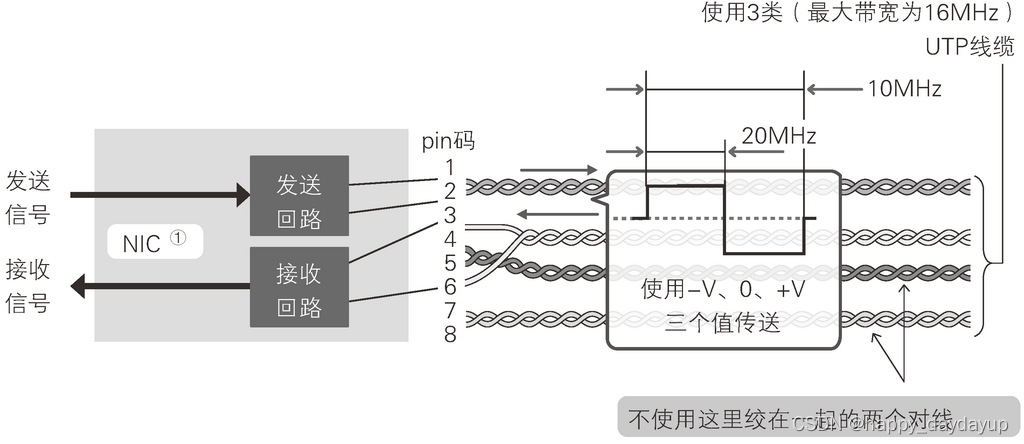

在 10BASE-T 中使用曼彻斯特编码的方式让转换的电气信号在双绞线上传输。从 Ethernet frame的Preamble 字段 中得到 20MHz 的时钟频率与 10Mbit/s 的 NRZ数据进行逻辑异或运算,得到在 20MHz 下采用 -V、0、+V 三个电平数值发送信号(V 表示电压)。该运算过程如下图所示,“0”表示“10”,“1”表示“01”。通过曼彻斯特编码后,直流信号部分将不复存在,从而抑制了信号衰减带来的干扰。

在 10BASE-T 中,使用 4 对双绞线中的 1 对(1 号与 2 号)信号线作为 10Mbit/s 信号的发送源,1 对(3 号与 6 号)信号线用于 10Mbit/s 信号的接收,剩余两组空闲不用。

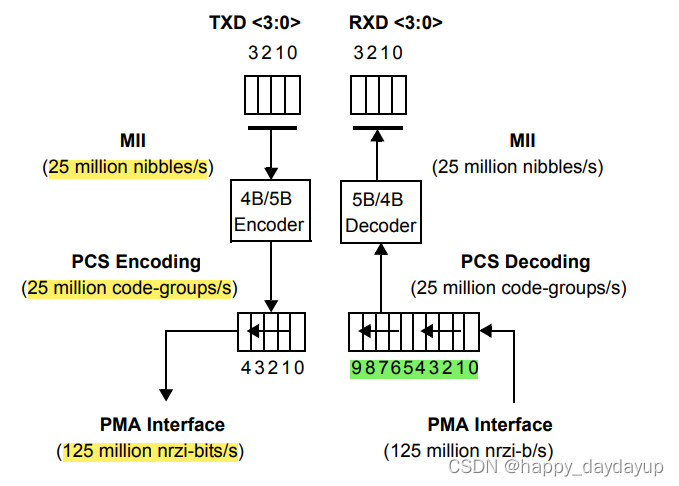

100BASE-T

100BASE-T主要指100BASE-TX,其余T类型非主流。

在 100BASE-TX 的标准中不再使用曼彻斯特编码,而是使用了一种叫做 MLT-3(Multi-Level Transition)的编码方式。该编码方式使用 -、0、+ 三个电平,当下一个数据为 0 时,保持信号电平不变;当下一个数据为 1 时,信号电平跳转。这样使信号电压变化平稳,能够减少信号传递中的谐波数量。

在使用 MLT-3 编码时,数据如果连续为 0,信号电平将不会发生任何变化,这将导致接收方无法检测出每一个时钟频率。为了避免这一问题,标准中采取了将 4bit 数据转换为 5bit 的方法,既能保证在发送的 5bit 数据中有两个以上的“1”,也能够在数据连续为“0”时,找得到同步的位置。另外,还能加入特殊的控制码。4B/5B 转换表@sec24.2.2.1:

由于将原来 4bit 的数据以 5bit 的方式发送,就使得发送速率为 100Mbit/s 的数据实际需要发送速率为 125Mbit/s 的电平信号。

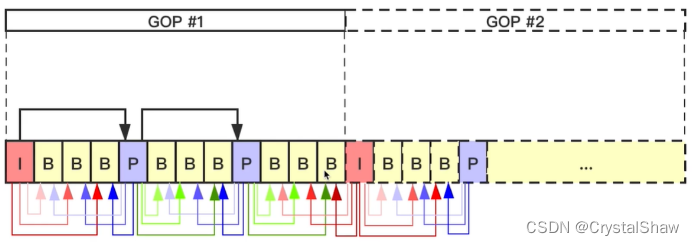

1000BASE-T

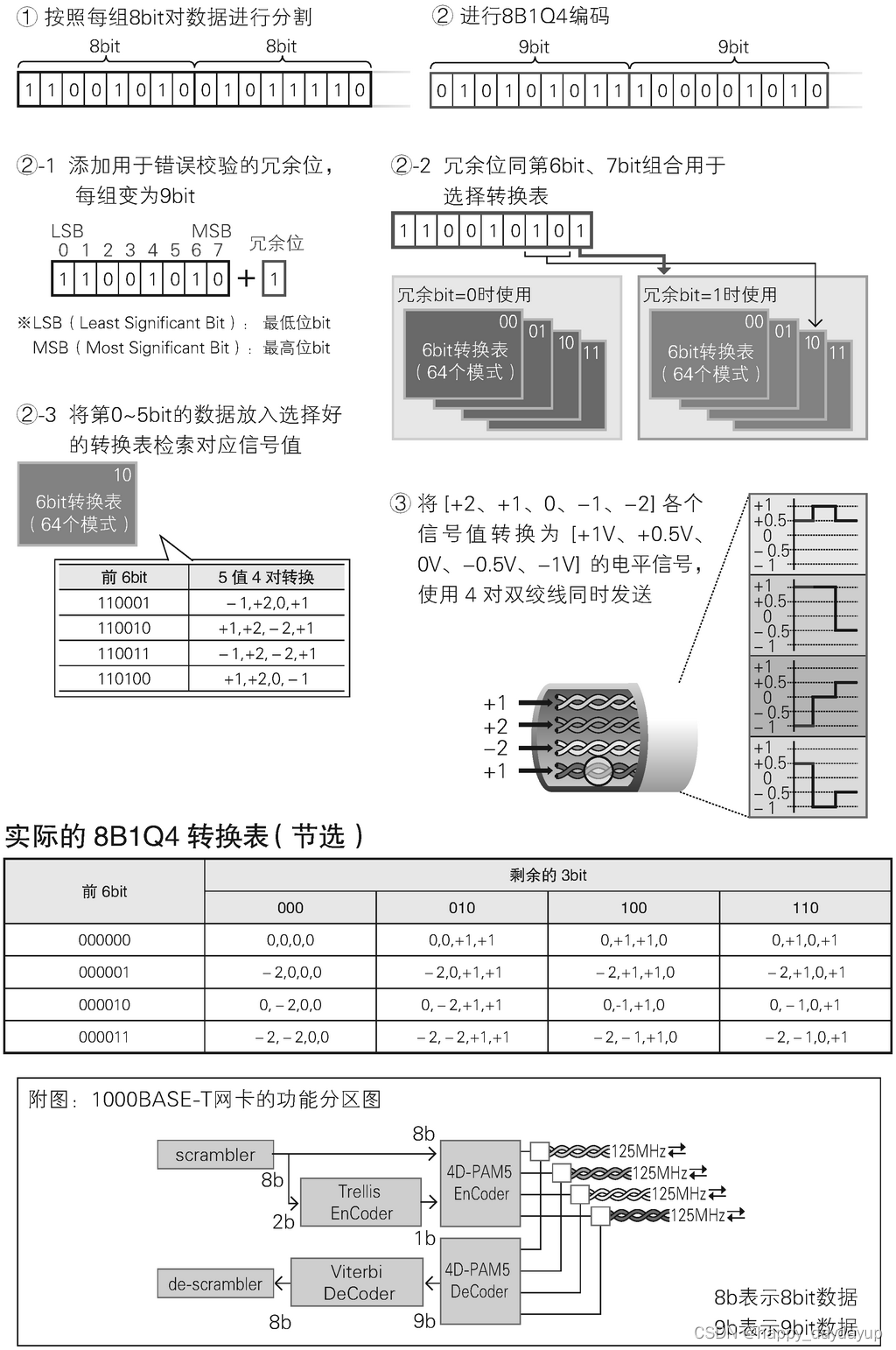

在 1000BASE-T 中使用了 8B1Q4(8 binary to 1 quinary 4,将8个2值数据 (GMII的data数据)转换成5值4组数据)的编码方式与 4D-PAM5(4-dimensional,5-level Pulse Amplitude Modulation,将从 8B1Q4 数据编码接收到的 4 维五进制符号用五个电压级别传送出去)的调制方式传输数据。8B1Q4 按照每组 8bit 对传输数据进行分割,每组再加上 1bit 的冗余位作为错误校验,一共为 9bit 数据。在 9bit 的数据中,根据冗余 bit 和前两个 bit 数据选择转换表,再根据转换表得到余下 6bit 所对应的 4 个信号值。信号值可以是 -2、-1、0、+1、+2 这 5 个值中的任意一个。例如,10010111 这 个 8bit 的数据,按照 8B1Q4 转换为 +1、-2、0、-1 这 4 个 信号值 后,就可以同时在双绞线上进行传输。将这一系列的数据调制发送就被称为 4D-PAM5 方式。具体编码过程见sec40.3.1.3。

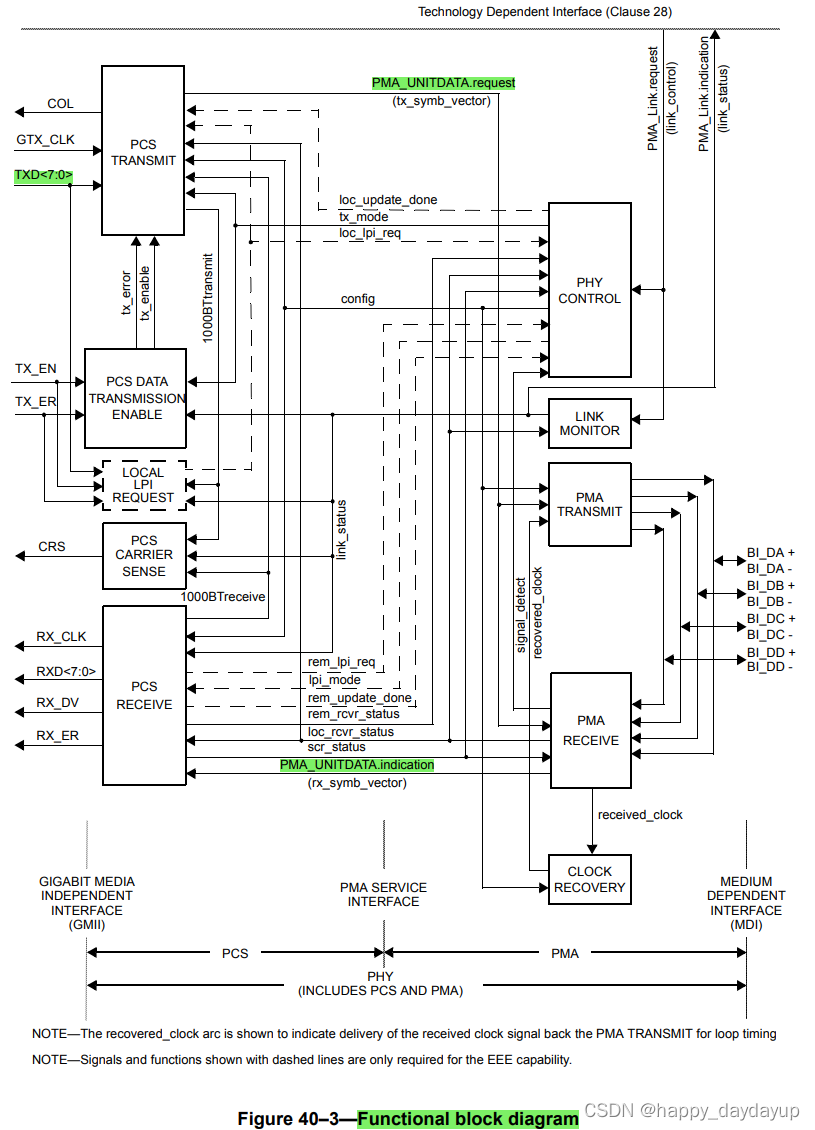

functional block:

pma clock recovery: 负责从接收数据中恢复出clock。

pma link monitor: 用于产生Link_status.

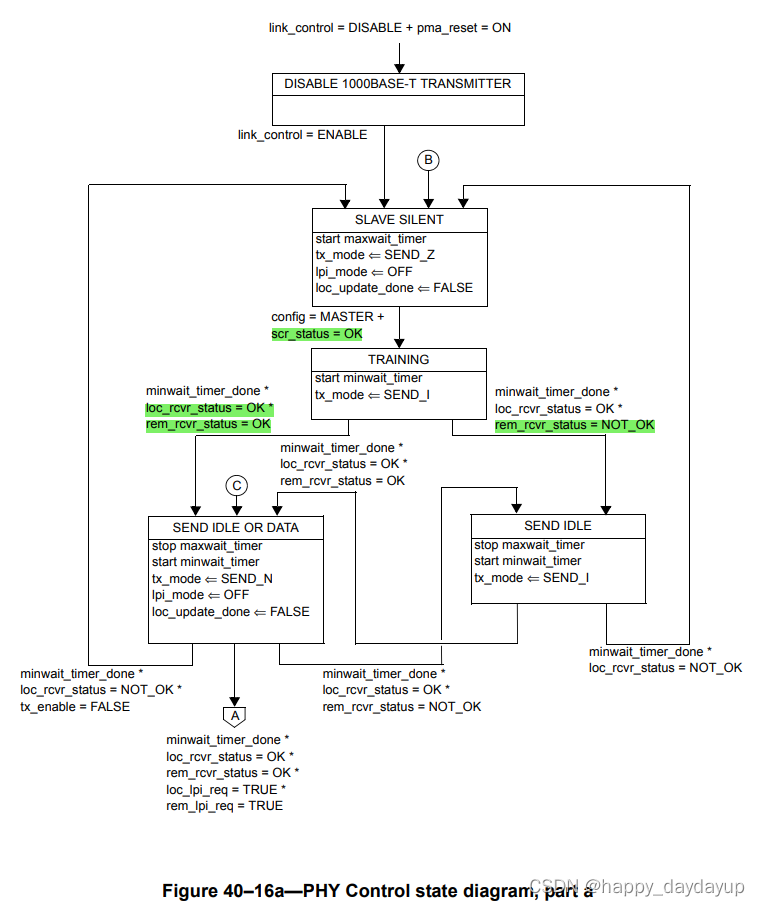

pma phy control @sec40.4.2.4: PHY Control generates the control actions that are needed to bring the PHY into a mode of operation during which frames can be exchanged with the link partner.

slave phy进入training的条件是scr_status=ok:the SLAVE PHY converges its decision feedback equalizer (DFE), acquires timing, and acquires its descrambler state. 可以理解为descrambler已经和master同步。

For the SLAVE PHY, the final convergence of the adaptive filter parameters is completed in the TRAINING state. The MASTER PHY performs all its receiver convergence functions in the TRAINING state. loc_rcvr_status的条件是:the PHY completes successful training and establishes proper receiver operations。具体的算法是implementation dependent, It can be based, for example, on observing the mean-square error at the decision point of the receiver and detecting errors during reception of symbol stream.

EEE时见Sec40.4.6.1 Figure 40–16b。