网卡(Network Interface Card,简称NIC),也称网络适配器,是电脑与局域网相互连接的设备。无论是普通电脑还是高端服务器,只要连接到局域网,就都需要安装一块网卡。如果有必要,一台电脑也可以同时安装两块或多块网卡。

电脑之间在进行相互通讯时,数据不是以流而是以帧的方式进行传输的。我们可以把帧看做是一种数据包,在数据包中不仅包含有数据信息,而且还包含有数据的发送地、接收地信息和数据的校验信息。

一个网卡主要包括OSI的最下面的两层,物理层和数据链路层

- 物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY

- 数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。数据链路层的芯片称之为MAC控制器

本文针对这两层进行相关的学习,总结整个系统的框架和物理上硬件组成原理,学习数据包的发送和接收的处理过程。

1. 系统概述

从硬件的角度来分析,以太网的电路接口一般由CPU、MAC(Media Access Control)控制器和物理层接口(physical Layer PHY)组成,如下图所示

对于上述三部分,并不一定都是独立的芯片,主要有以下几种情况

- CPU内部集成了MAC和PHY,难度较高

- CPU内部集成MAC,PHY采用独立芯片(主流方案)

- CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片(高端采用)

PHY整合了大量模拟硬件,而MAC是典型的全数字器件,芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合

以常用的CPU内部集成MAC,PHY采用独立的芯片方案,虚线内表示CPU和MAC集成在一起,PHY芯片通过MII接口与CPU上的MAC互联。

对于这种方案,其硬件方案比独立的相对于更简单,PHY与MAC之间有以下两个重要的硬件接口

- MDIO总线接口,主要是完成CPU对于PHY芯片的寄存器配置

- MII总线接口,主要是完成数据收发相关的业务

当我们的PHY芯片发送数据,接受到MAC层发送过来的数字信号,然后转换成模拟信号,通过MDI接口传输出去。但是我们的网线传输的距离又很长,有时候需要送到100米甚至更远的地址,那么就会导致信号的流失。而且外网线与芯片直接相连的话,电磁感应和静电,也很容易导致芯片的损坏,所以就要使用网络变压器,其主要作用是

- 传输数据,它把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到不同电平的连接网线的另外一端

- 隔离网线连接的不同网络设备间的不同电平,以防止不同电压通过网线传输损坏设备

- 还能使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用,保护PHY免遭由于电气失误而引起的损坏(如雷击)

2. MAC控制器

MAC(Media Access Control),即媒体访问控制子层协议,该部分有两个概念:MAC可以是一个硬件控制器以及MAC通讯协议。该协议位于OSI七层协议中数据链路层的下半部分,主要是负责控制与连接物理层的物理介质。

- 发送数据:MAC协议可以事先判断是否可以发送数据,如果可以发送将数据加上一些控制信息,最后将数据以及控制信息以规定的格式发送到物理层

- 接收数据:MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息后发送至LLC(逻辑链路控制)层。

2.2 MAC与PHY接口

MAC与PHY之间通过两个接口连接,分别为SMI接口和MII接口。

- MII叫做介质独立接口,以太网MAC通过该接口发出数据帧经过PHY后传输到其他网络节点上,同时其他网络节点的数据先经过PHY后再由MAC接收;

- SMI叫做是串行管理接口,以太网MAC通过该接口可以访问PHY的寄存器,通过对这些寄存器操作可对PHY进行控制和管理。

2.1.1 MII接口

MII(Media Independent Interface)即媒体独立接口,MII接口是MAC与PHY连接的标准接口。它是IEEE-802.3定义的以太网行业标准。MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术。媒体独立表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作.它包括一个数据接口,以及一个MAC和PHY之间的管理接口。MII接口有MII、RMII、SMII、SSMII、SSSMII、GMII、SGMII、RGMII等。这里简要介绍其中的MII和RGMII。

MII接口主要包括以下三个部分:

- 从MAC层到PHY层的发送数据接口

- 从PHY层到MAC层的接收数据接口

- 从MAC层和PHY层之间寄存器控制和信息获取的MDIO接口

首先来看看MII的MAC层定义接口

MII 数据接口总共需要 16 个信号,包括 TX_ER,TXD[3:0],TX_EN,TX_CLK,COL,RXD[3:0],RX_ER,RX_CLK,CRS,RX_DV 等。MII的时钟为25MHz,传输速率为10/100Mbps。所以MII的特性如下:

- 支持10Mb/s和100Mb/s的数据速率

- 100M工作模式下,参考时钟是25MHz;10M工作模式下,信号参考时钟是2.5MHz

- 支持全双工、半双工两种工作模式

- 发送和接收数据时采用,4bit方式

RMII的用途:

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线(2数据位),所以它一般要求是50MHz的总线时钟。RMII一般用在多端口的交换机,所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目.RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口.和MII一样,RMII支持10Mbps和100Mbps的总线接口速度.

后来为了支持千兆网口,也就开始有了千兆网的MII接口,也就是GMII接口。现在比较常用的是RGMII,减小了MAC和PHY之间的引脚数量。数据信号和控制信号混合在一起,并且在工作时钟的上升沿和下降沿同时采样,其对应关系图如下:

- 10M带宽对应的是2.5MHz,因为4bit*2.5M=10Mbps

- 100M带宽对应的是25MHz,因为4bit*25M=100Mbps

- 1000M带宽对应的是125MHz,因为250MHz频率太高,所以采用双边沿采样技术(会带来设计复杂度)。4bit125M2=1000Mbps

| 接口 | 引脚 | 速度支持(Mbps) | 利 | 弊 |

|---|---|---|---|---|

| MII | RX_D[3:0] RX_CLK, RX_DV, CRS, COL TX_D[3:0], TX_CLK, TX_EN (14) | 10, 100 | 普通引脚分配、低速、便于布线、最低延迟 | 无1-Gbps支持,高引脚计数 |

| MII减少(RMII) | RX_D[1:0], CRS_DV, TX_D[1:0], TX_EN (6) | 10, 100 | 引脚计数减少 | 确定性延迟低 (由于先进、先出),无1-Gbps支持 |

| 千兆位MII(GMII) | RX_D[7:0], GRX_CLK, RX_CTRL, TX_D[7:0], GTX_CLK, TX_CTRL (20) | 10, 100, 1000 | 1-Gbps支持,低延迟 | 高引脚计数,一般不支持 |

| 千兆位MII减少(RGMII) | RX_D[3:0], RX_CLK, RX_CTRL, TX_D[3:0], TX_CLK, TX_CTRL (12) | 10, 100, 1000 | 1-Gbps支持,普通引脚分配 | 脚分配 布线困难,电磁兼容性(EMC)差 |

| 串行千兆位MII(SGMII) | SO_P, SO_M, SI_P, SI_M (4) | 10, 100, 1000 | 1-Gbps支持,普通引脚分配,电磁兼容性优良,易于布线 | 集成电路更昂贵 |

2.1.2 SMI接口

SMI是MAC内核访问PHY寄存器接口,它由两根线组成,双工,MDC为时钟,MDIO为双向数据通信,原理上跟I2C总线很类似,也可以通过总线访问多个不同的phy。

MDC/MDIO基本特性:

- 两线制:MDC(时钟线)和MDIO(数据线)。

- 时钟频率:2.5MHz

- 通信方式:总线制,可同时接入的PHY数量为32个

- 通过SMI接口,MAC芯片主动的轮询PHY层芯片,获得状态信息,并发出命令信息。

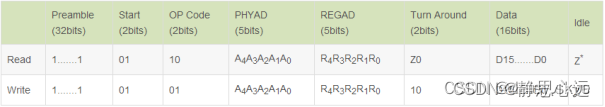

管理帧格式:

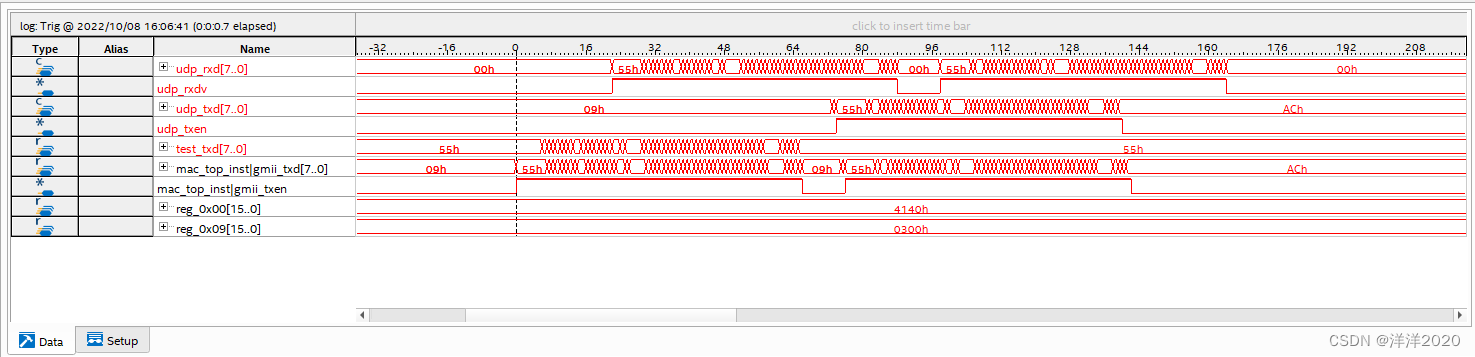

读操作时序

写操作时序

- 报头: 每个读写均可通过报头字段启动,报头字段对应于MDIO线上32个连续的逻辑“1”位以及MDC的32个周期,该字段用于与PHY设备建立同步

- 起始: 起始由<01>模式定义

- 操作: 定义读写类型

- PADDR: PHY地址由5位,可构成32个唯一PHY地址

- RADDR: 寄存器地址有5位

- TA:

- 数据: 数据字段为16位

- 空间: MDIO线驱动为高阻态,三态驱动器必须禁止,PHY的上拉电阻使线路保持高阻态

3.PHY

物理层位于OSI最底层,物理层协议定义电气信号、线的状态、时钟要求、数据编码和数据传输用的连接器。 物理层的器件称为PHY。

PHY是物理接口收发器,它实现OSI模型的物理层。IEEE-802.3标准定义了以太网PHY包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

3.1 什么是PHY

- 发送数据:对于PHY来说,并没有帧的概念,对它来说,不管是地址、数据还是CRC,都会将并行数据转换为串行数据流,在按照物理层的编码规则把数据编码,最终转换成模拟信号发送出去

- 接收数据:从外部接收数据时,模拟信号先转成数字信号,再经过解码得到数据, 经过MII送到MAC

- CSMA/CD:可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突。这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据

3.2 MDI

MDI口是快速以太网100BASE-T定义的与介质有关接口(Media Dependent Interface)。MDI是指通过收发器发送的100BASE-T信号,即100BASE-TX、FX、T4或T2信号。将集线器连接网络接口卡时,其发送和接收对通常是相互连接的。集线器之间连接时,通常需要一条跨接电缆,其中的发送和接收对是反接的。MDI是正常的UTP或STP连接,而MDI-X连接器的发送和接收对是在内部反接的,这就使得不同的设备(如集线器-集线器或集电器-交换机),可以利用常规的UTP或STP电缆实现背靠背的级联。”

3.3 PHY基础知识简介

PHY是IEEE 802.3规定的一个标准模块,SOC可以通过MDIO对PHY进行配置或者读取phy相关状态,PHY内部寄存器必须满足

- PHY芯片的寄存器地址空间是5位,一般由外部硬件连接决定。

- 地址空间031共32个寄存器,IEEE定义了015这16个寄存器的功能,16-31这16个寄存器由厂商自行实现。也就是说不管哪个厂商的PHY芯片,其中0~15这16个寄存器是一模一样的。

仅靠这 16个寄存器完全可以驱动起PHY芯片,至少能保证基本的网络数据通信。因此 Linux 内核有通用 PHY 驱动,按道理来讲,不管你使用的哪个厂家的 PHY 芯片,都可以使用 Linux 的这个通用 PHY 驱动来验证网络工作是否正常。事实上在实际开发中可能会遇到一些其他的问题导致 Linux 内核的通用 PHY 驱动工作不正常,这个时候就需要驱动开发人员去调试了。

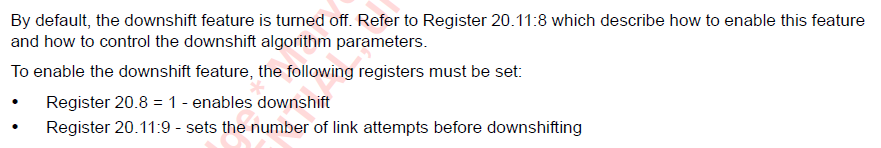

随着现在PHY芯片性能越来越强大,32个寄存器已经无法满足厂商的需求,因此很多厂商采用了分页机制来开展寄存器地址空间,以求定义更多的寄存器。这些多出来的几次器可以实现厂商特有的一些技术,因此在Linux内核里面可以看到很多具体的PHY芯片驱动源码。

| Register Address | Register Name |

|---|---|

| 0 | Control |

| 1 | Status |

| 2,3 | PHY Identifier |

| 4 | Auto-Negotiation Advertisement |

| 5 | Auto-Negotiation Link Partner Base Page Ability |

| 6 | Auto-Negotiation Expansion |

| 7 | Auto-Negotiation Next Page Transmit |

| 8 | Auto-Negotiation Link Partner Received Next Page |

| 9 | MASTER-SLAVER Control Register |

| 10 | MASTER-SLAVE Status Regsiter |

| 11 | PSE Control Register |

| 12 | PSE status Register |

| 13 | MMD Access Control Register |

| 14 | MMD Access Adderss Data Register |

| 15 | Extended Status |

| 16~31 | Vendor Specific |

4. 总结

MAC 就是以太网控制器,属于OSI的数字链路层。 phy 属于OSI的物理层(Physical layer),所以叫phy。

-

MAC主要处理的数字信号

-

PHY负责把MAC的数字信号进行编码,串行化等操作后,转化为模拟信号进行发送。PHY在数据接受时, 进行如上所述的逆操作,将模拟信号转化为数字信号,解码,并行化后,传给MAC。

基础以太网物理层非常简单:它是一种物理层收发器(发射器和接收器),能将一个设备物理地连接到另一个设备。这种物理连接可以是铜线(例如CAT5电缆——一种家庭使用的蓝色插线电缆)或光纤电缆。