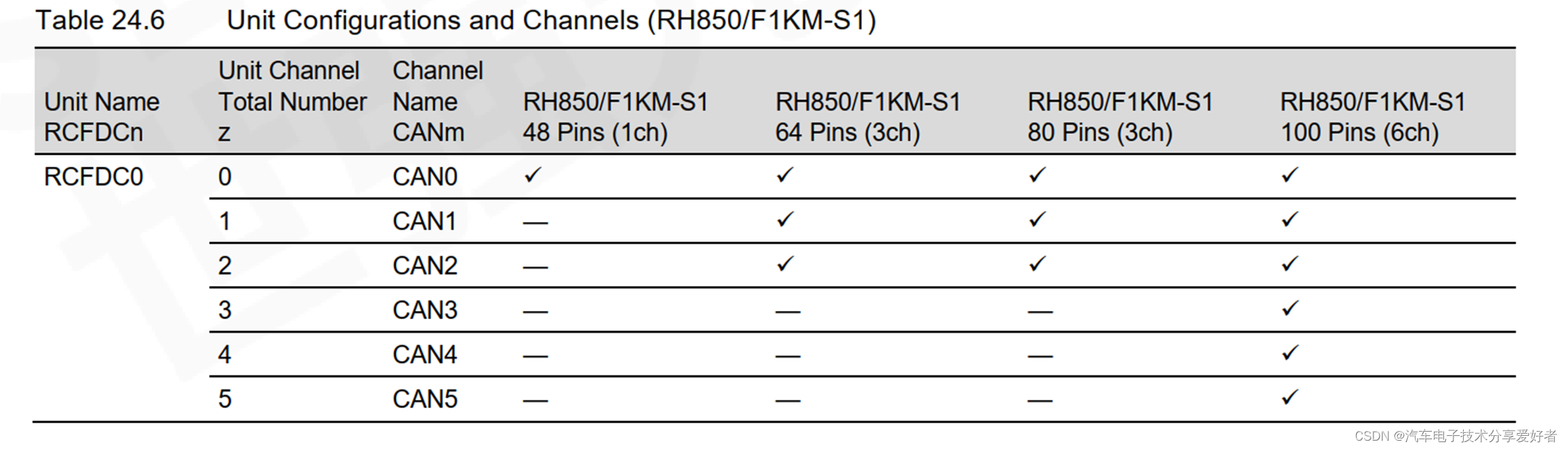

芯片型号:RH850/F1KM-S1

不同PIN封装形式所支持的CAN通道数量不同,RS-CAN通道数量最多可支持6路。

目录

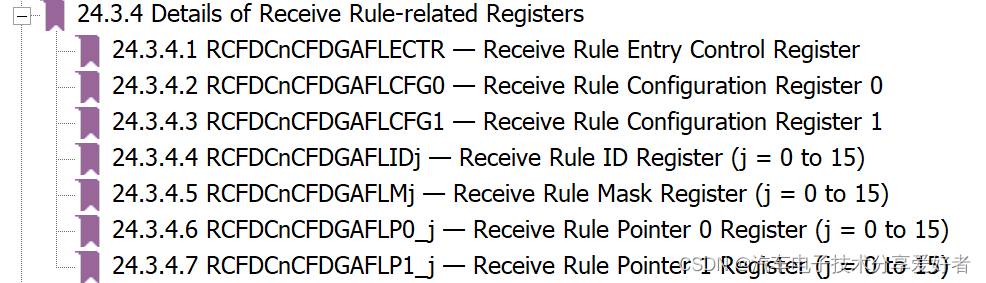

一、FLECCTR(接收规则Entry控制寄存器)

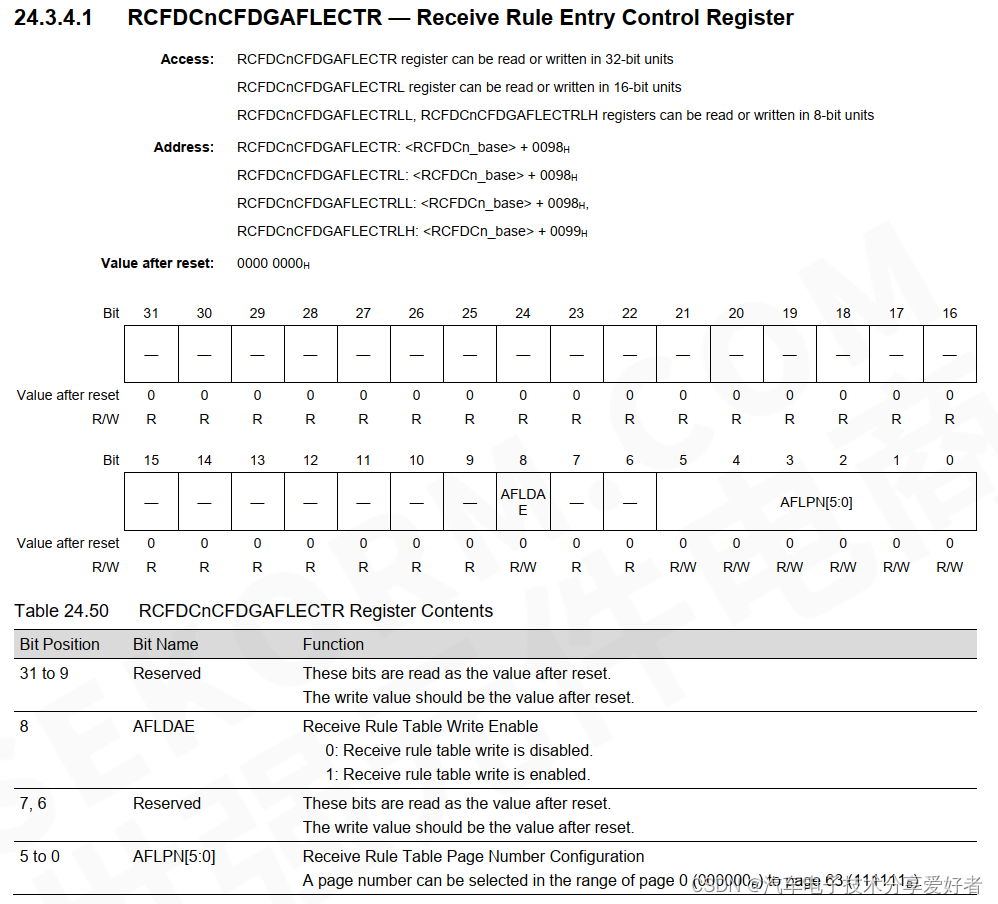

二、FLCFG0(接收规则配置寄存器0)

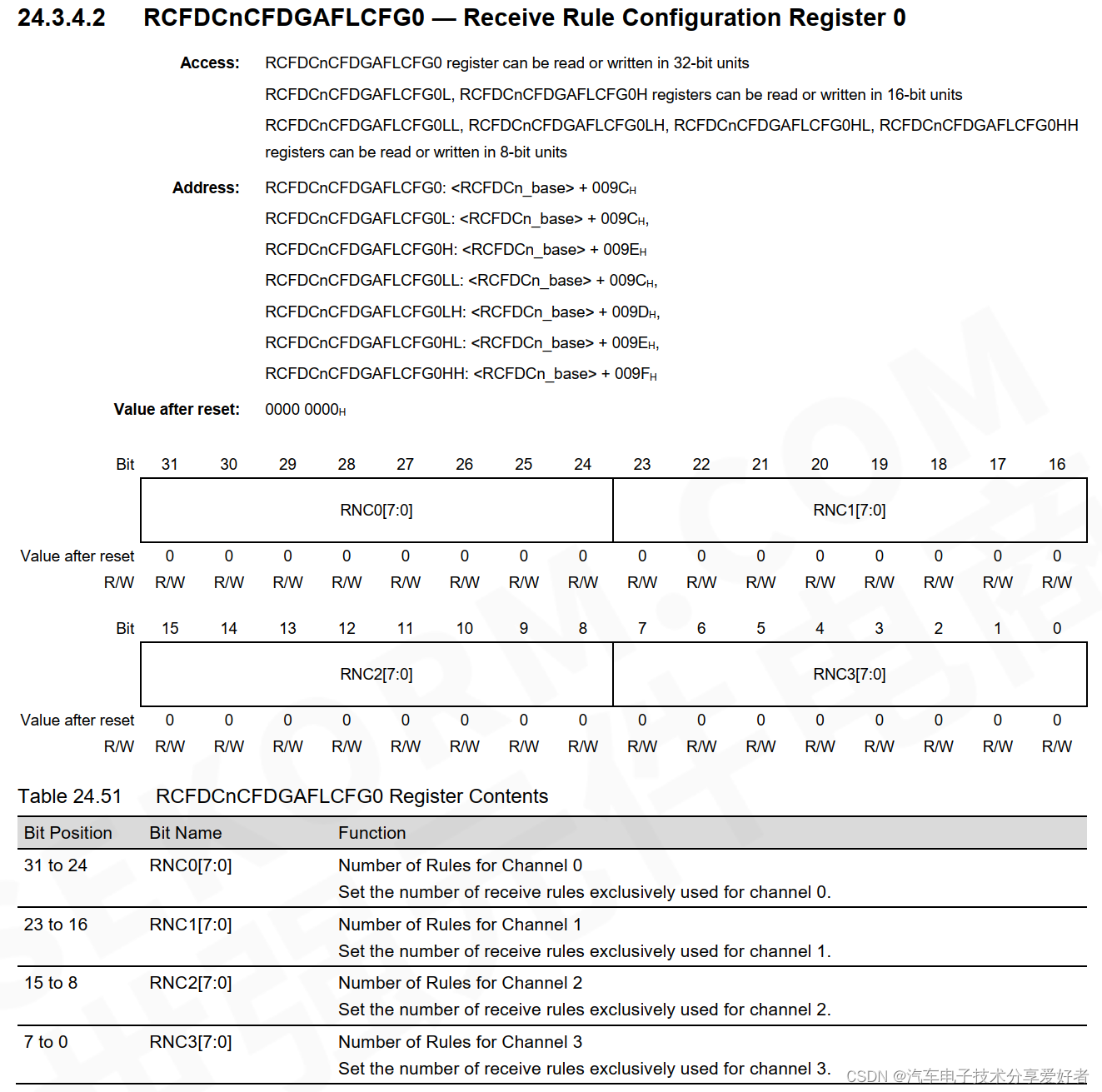

三、FLCFG1(接收规则配置寄存器1)

四、FDGAFLIDj(接收规则ID寄存器)

五、FDGAFLMj(接收规则掩码寄存器)

六、FDGAFLP0_j(接收规则指针寄存器0)

七、FDGAFLP1_j(接收规则指针寄存器1)

接收规则配置流程

接收规则配置示例代码

接收规则设置示例代码

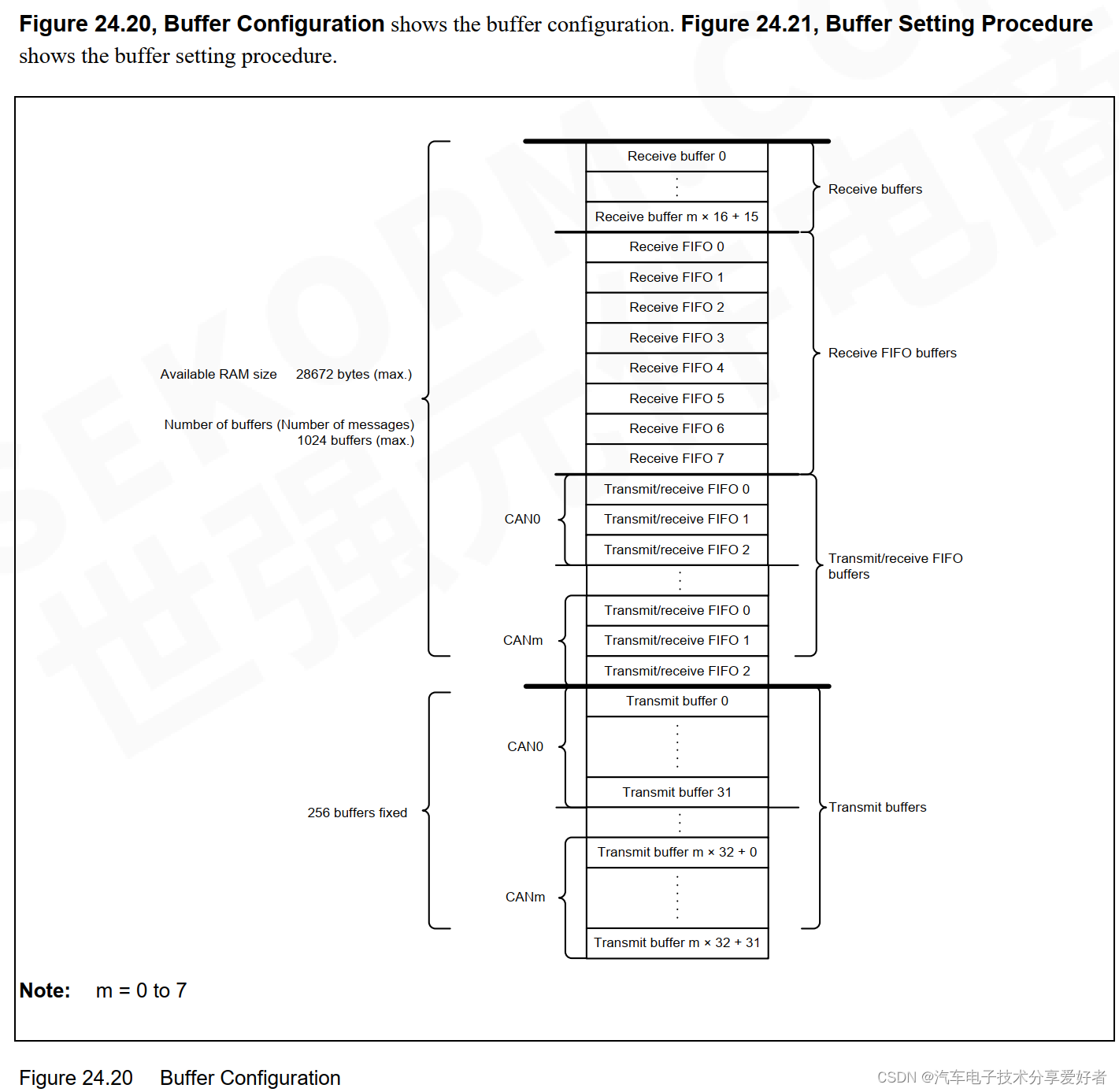

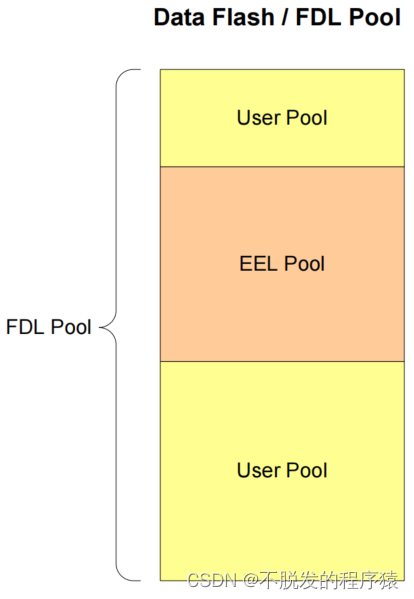

接收缓存RAM区

RS-CANFD接收滤波基于接收规则表,控制和配置功能主要涉及7类寄存器:

一、FLECCTR(接收规则Entry控制寄存器)

【重要*】BitAFLDAE=1,使能Rule Table(接收规则列表)写权限;

(1)写操作前,置位;

(2)写操作完成后,清零;

BitAFLPN指定Rule Table所属的Page号。

(1)Page可选值为0~63,Page总数共计64个。

(2)每个Page包含16个Rule,Rule可选值为0~15。

二、FLCFG0(接收规则配置寄存器0)

FLCFG0和FLCFG1寄存器指定CAN通道包含的Rule数量;8个通道(channel0-channel7)由这两个寄存器完成数量设置。

例如:

BitRNC0[7:0]=0x3,意味着CAN通道0包含的Rule数量为3个;

BitRNC2[7:0]=0x5,意味着CAN通道2包含的Rule数量为5个;

BitRNC7[7:0]=0x6,意味着CAN通道7包含的Rule数量为6个。

三、FLCFG1(接收规则配置寄存器1)

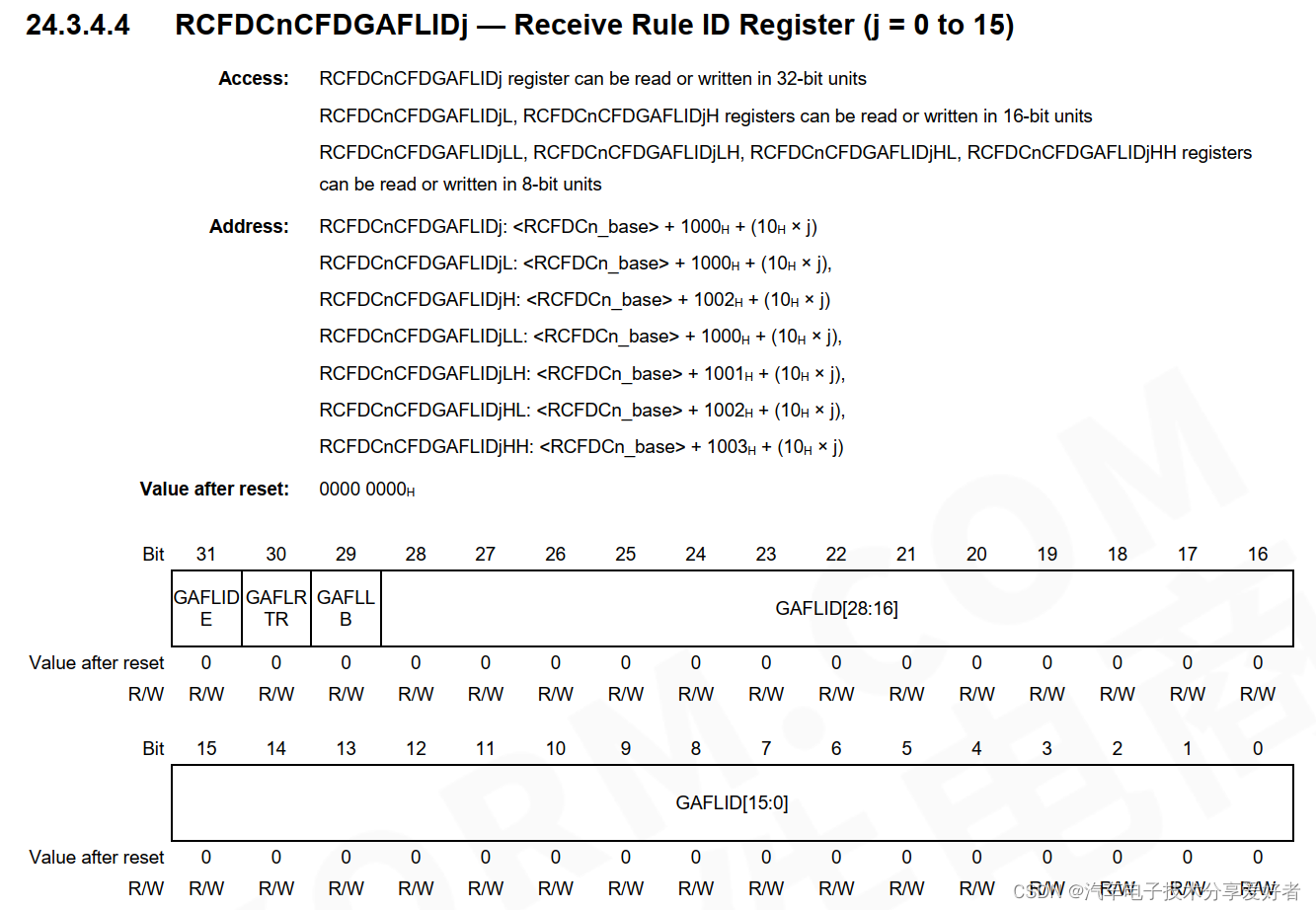

四、FDGAFLIDj(接收规则ID寄存器)

接收规则的最大条目数量为16,该类型寄存器共计16个,使用“j”来索引。

【重要*】该寄存器存入预接收的CAN(FD) 报文ID及类型(扩展帧标识IDE、远程帧标识RTR、CAN通道来源)。

注意:CAN(FD) 标准帧ID所占位置为bit0~bit10,不需要移位;扩展帧ID所占位置为bit0~bit28。

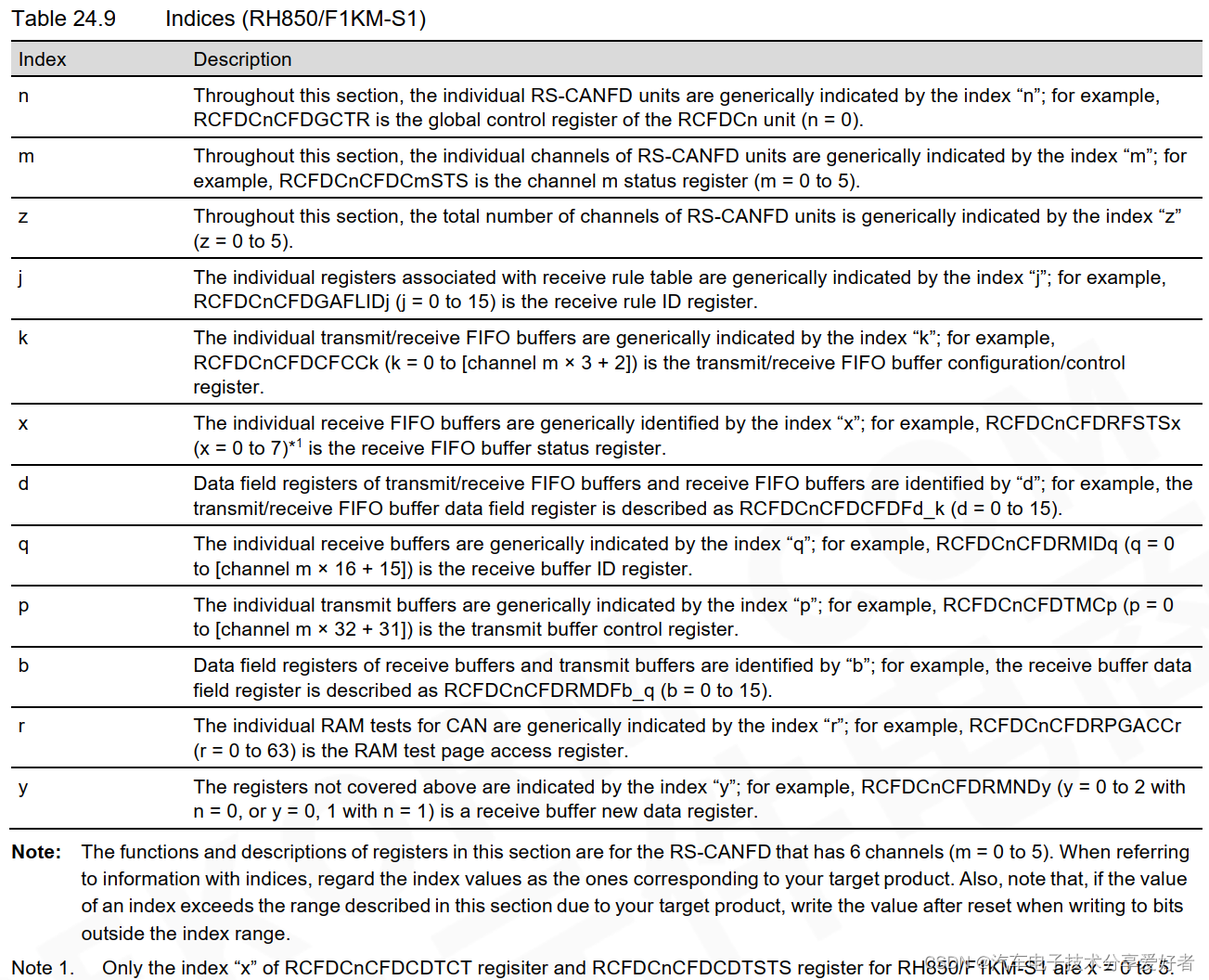

索引“j”的详细描述:

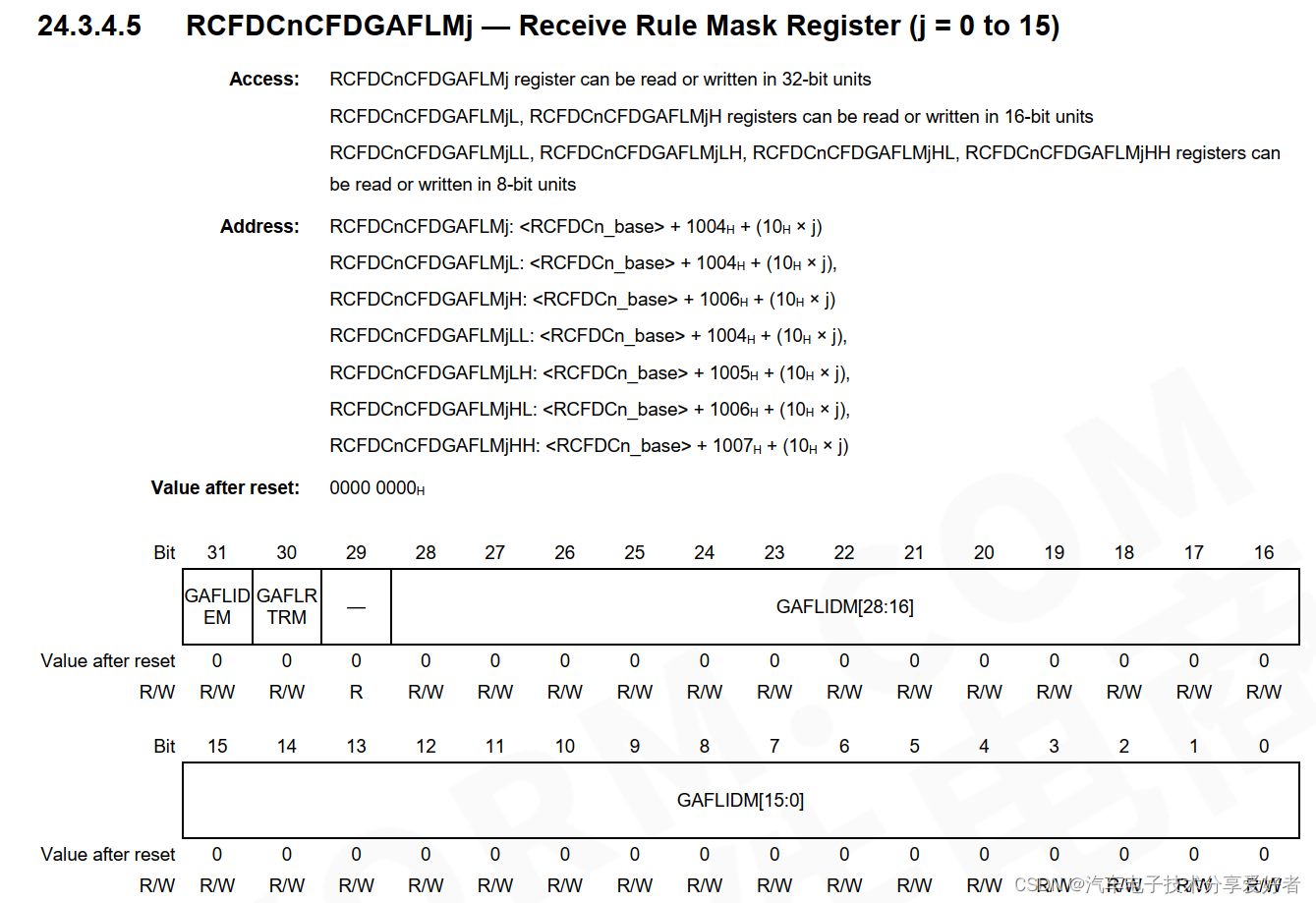

五、FDGAFLMj(接收规则掩码寄存器)

【重要*】该寄存器与FDGAFLIDj相对应,为掩码寄存器。

0x0:‘关心’,相关位需要比较;

0x1:‘不关心’,相关位不需要比较。

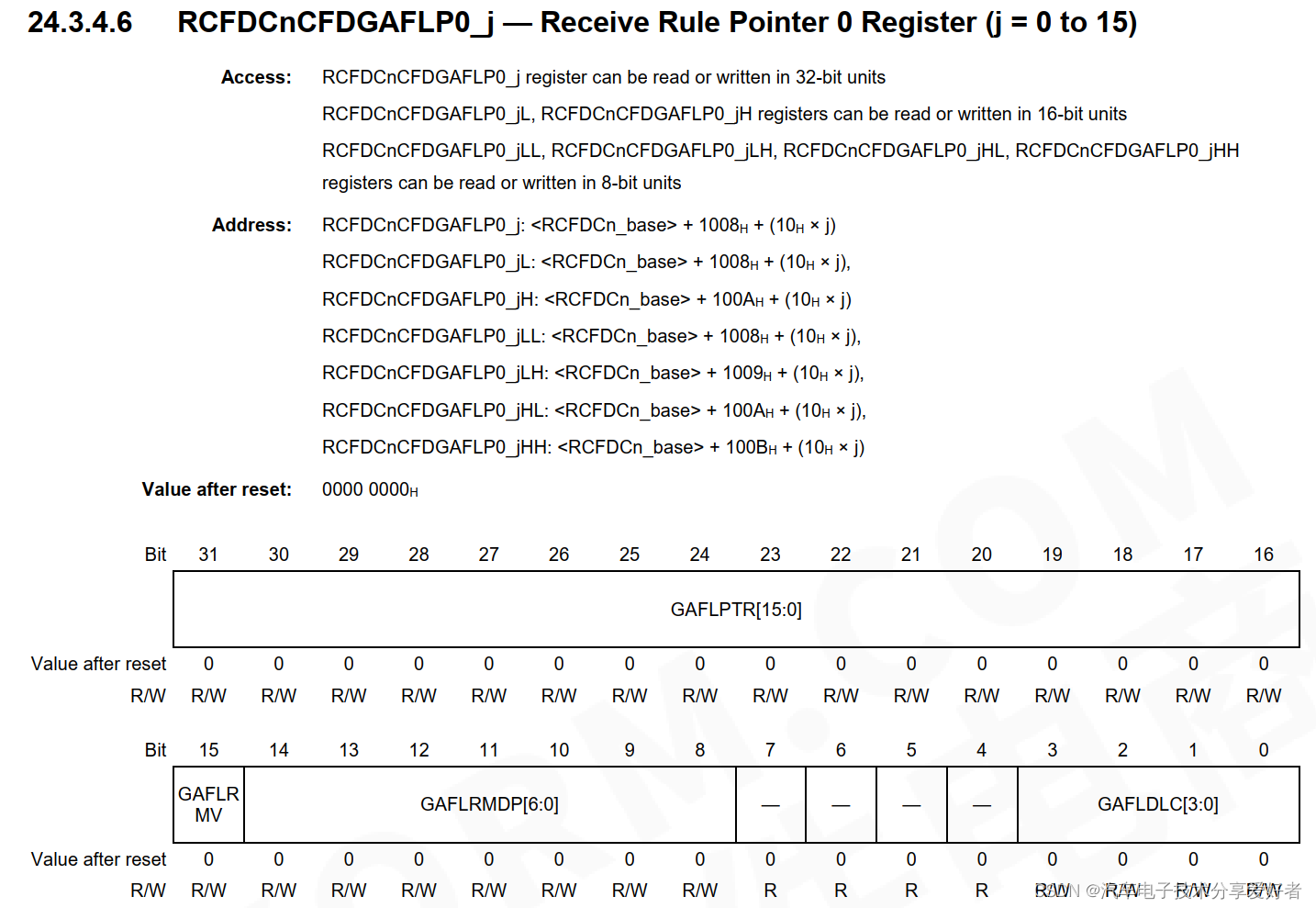

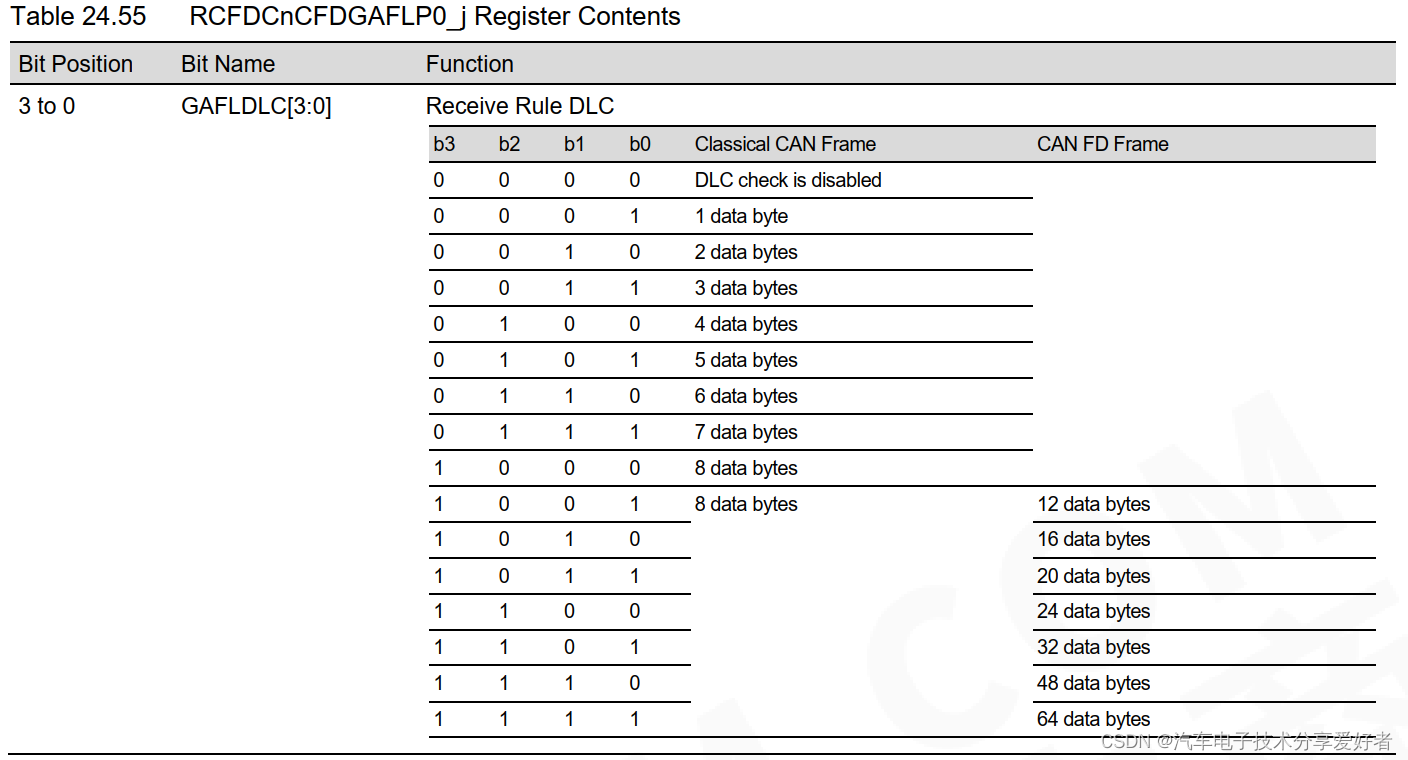

六、FDGAFLP0_j(接收规则指针寄存器0)

BitGAFLPTR[15:0]:接收规则标签信息;

【重要*】BitGAFLRMV:是否使能接收Buffer;

——接收如果采用FIFO接收缓存机制,需要设置FDGAFLP1_j相关寄存器。

【重要*】BitGFLRMDP[6:0]:指定接收Buffer号;

【重要*】BitGAFLDLCA[3:0]:是否使能DLC检查,即RSCAN提供了报文DLC检查机制,如下图。如果采用软件DLC滤波,该4位设置为0。

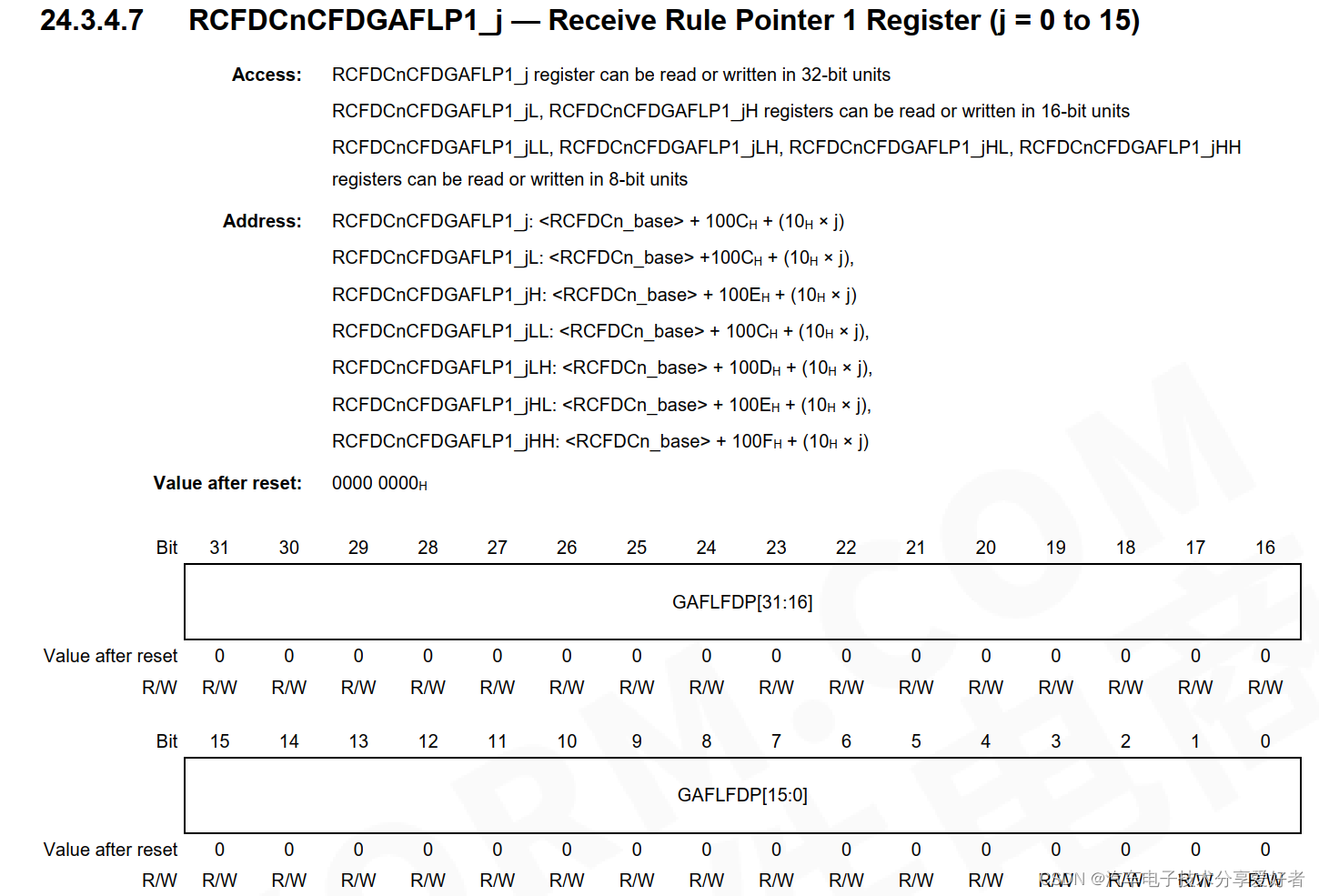

七、FDGAFLP1_j(接收规则指针寄存器1)

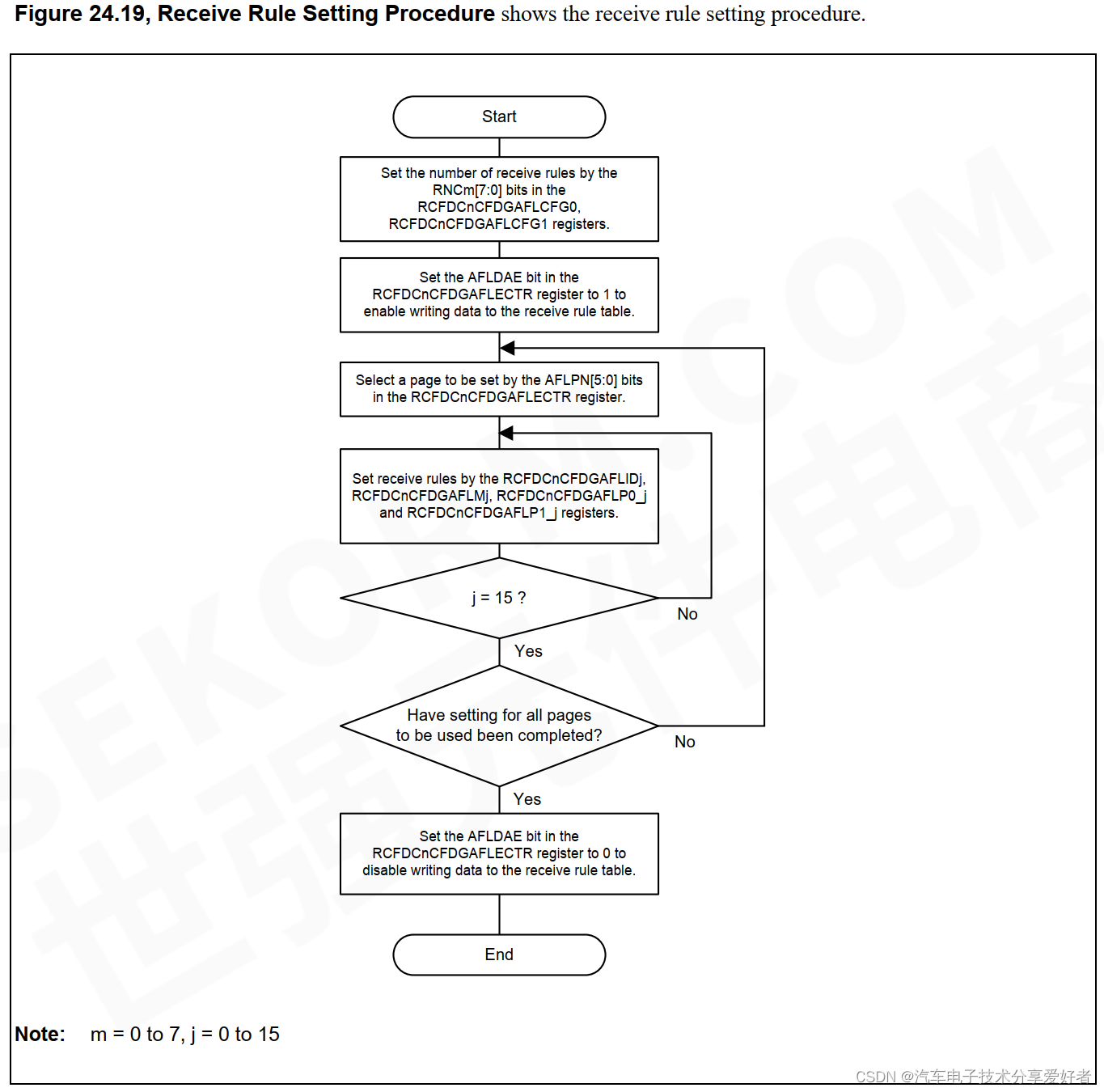

接收规则配置流程

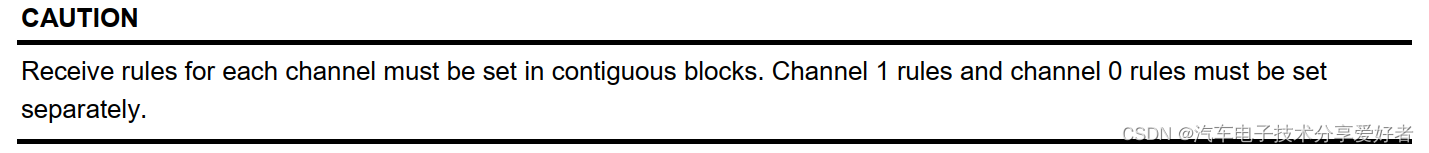

【重要*】每个通道具体的接收规则必须通过连续写地址方式完成,关联所在的Page页。

Each receive rule consists of 16 bytes in the RCFDCnCFDGAFLIDj, RCFDCnCFDGAFLMj,

RCFDCnCFDGAFLP0_j, and RCFDCnCFDGAFLP1_j registers (j = 0 to 15).

即FDGAFLIDj, FDGAFLMj,FDGAFLP0_j, FDGAFLP1_j四个寄存器连续写入配置数据,由一个结构体数组实现。

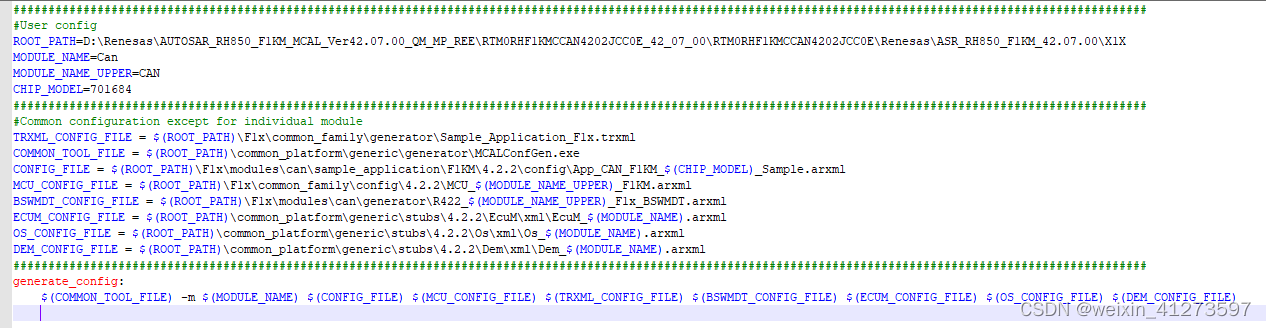

接收规则配置示例代码

canfd_cre_type CANFD_RX_RULE_TABLE[16] = {

/* CAN 0 reception rules */{0x00000010UL, 0xDFFFFFF0UL, 0x00008000UL, 0x00000000UL}, /* NO.000 : std data frm ID = H'10~1F will be accepted, 20 data length, destination Rx Buffer0 */{0x00000020UL, 0xDFFFFFF0UL, 0x00008100UL, 0x00000000UL}, /* NO.001 : std data frm ID = H'20~2F will be accepted, destination Rx Buffer1 */{0x00000030UL, 0xDFFFFFF0UL, 0x00008200UL, 0x00000000UL}, /* NO.002 : std data frm ID = H'30~3F will be accepted, destination Rx Buffer2 */{0x00000040UL, 0xDFFFFFF0UL, 0x00008300UL, 0x00000000UL}, /* NO.003 : std data frm ID = H'40~4F will be accepted, destination Rx Buffer3 */{0x00000050UL, 0xDFFFFFFFUL, 0x00008400UL, 0x00000000UL}, /* NO.004 : std data frm ID = H'50 will be accepted, destination Rx Buffer4 */{0x00000060UL, 0xDFFFFFFFUL, 0x00008500UL, 0x00000000UL}, /* NO.005 : std data frm ID = H'60 will be accepted, destination Rx Buffer5 */{0x00000070UL, 0xDFFFFFFFUL, 0x00008600UL, 0x00000000UL}, /* NO.006 : std data frm ID = H'70 will be accepted, destination Rx Buffer6 */{0x00000080UL, 0xDFFFFFFFUL, 0x00008700UL, 0x00000000UL}, /* NO.007 : std data frm ID = H'80 will be accepted, destination Rx Buffer7 */

};解释CAN0第一个接收规则:

0x00000010UL, 0xDFFFFFF0UL, 0xB0008000UL, 0x00000000UL

FDGAFLID0=0x00000001:ID=0x10

FDGAFLM0=0xDFFFFFF0:接收掩码bit0~bit3为0,bit0~bit3为'不关心',可接收ID范围为0x10~0x1F

FDGAFLP0_0=0x00008000:使能接收Buffer,接收BufferNum=0

FDGAFLP1_0=0x00000000:无

接收规则设置示例代码

uint16 RxRuleIdx; /* Set Rx rule number per channel */RCFDC0CFDGAFLCFG0 |= 0x20ul; /*Channel 2 has 2 rx rules *//* Get access base address of Rx rule */pCRE = (volatile can_cre_type*)&(RCFDC0CFDGAFLID0);/* Receive Rule Table Write Enable */RCFDC0CFDGAFLECTR |= 0x00000100; /*set bit8 to 1, Receive rule table write is enabled*//* Copy Rx rule one by one */for (RxRuleIdx = 0U; RxRuleIdx < 16; RxRuleIdx++){PageRxRuleIdx = (uint8) (RxRuleIdx & 0x0F); /*RxRuleIdx=0, page=0; RxRuleIdx=16, page=1; RxRuleIdx=32,page=2;...*//* Update target Rx rule page if necessary. */if (PageRxRuleIdx == 0U) {RCFDC0CFDGAFLECTR |= RxRuleIdx >> 4U; /*CAN_RX_RULE_PAGE_IDX_BIT_POS= 4U*/}/* Set a single Rx rule.*/pCRE[PageRxRuleIdx] = RX_RULE_TABLE_LIST1[RxRuleIdx];}/* Receive Rx rule write Disable */RCFDC0CFDGAFLECTR &= 0xfffffeff;

Notes:

● The acceptance filter processing checks receive rules sequentially in ascending order from the smallest rule number.

If the same ID, IDE bit, or RTR bit value is set for multiple receive rules, the smallest number of receive rule is used for the acceptance filter processing.

If the message does not pass through the subsequent DLC filter processing, the data processing is terminated without returning to the acceptance filter processing and the message is not stored in the buffer.【重要*】优先经过DLC检查,建议禁能。

接收缓存RAM区