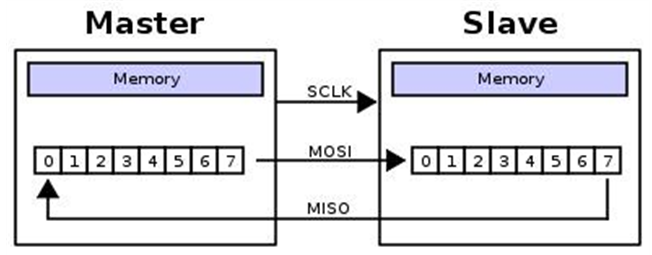

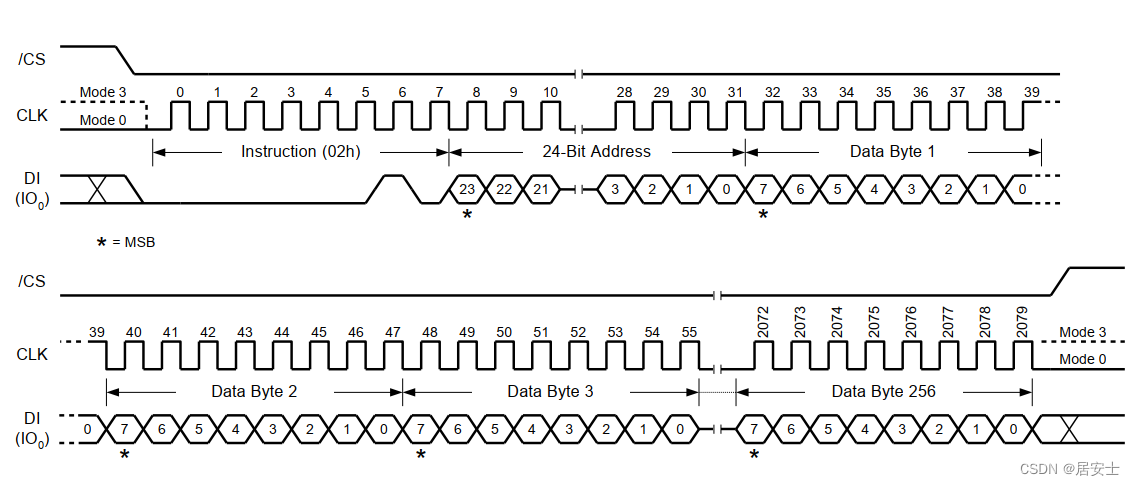

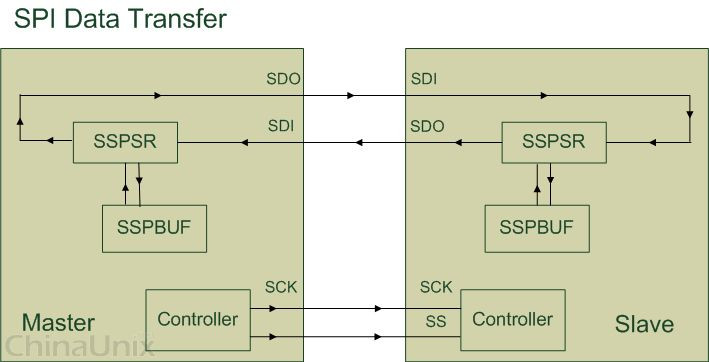

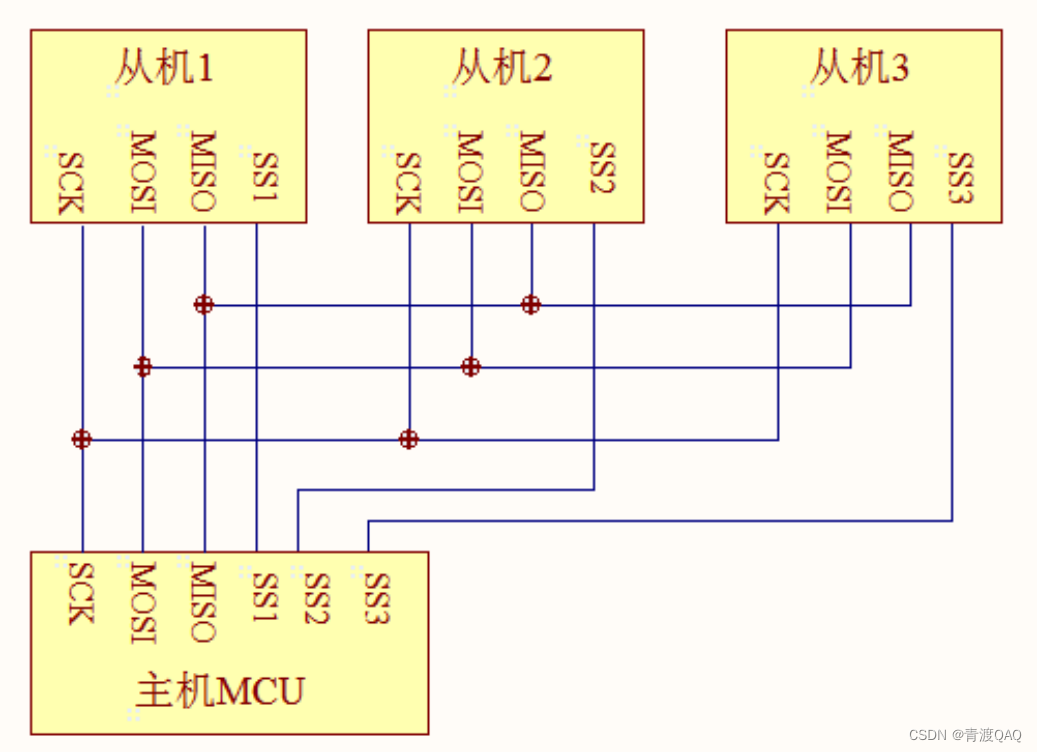

SPI(serial peripheral interface,串行外围设备接口)总线技术是Motorola公司推出的一种同步串行接口。它用于CPU与各种外围器件进行全双工、同步串行通讯。它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。即完成一个字节数据传输的实质是两个器件寄存器内容的交换。主SPI的时钟信号(SCK)使传输同步。其典型系统框图如下图所示。

图1 典型系统框图

2.SPI总线的主要特点

· 全双工;

· 可以当作主机或从机工作;

· 提供频率可编程时钟;

· 发送结束中断标志;

· 写冲突保护;

.总线竞争保护等。

3.SPI总线工作方式

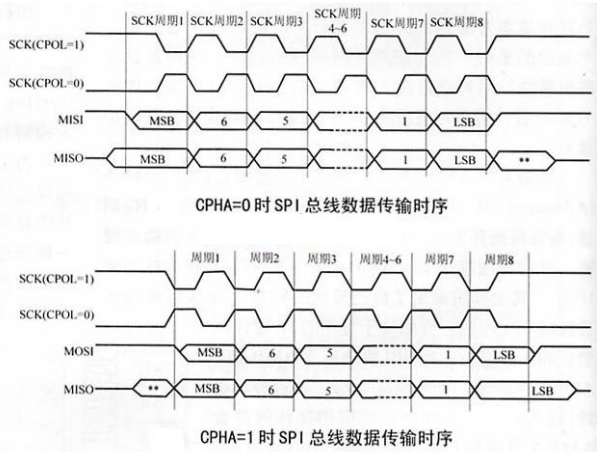

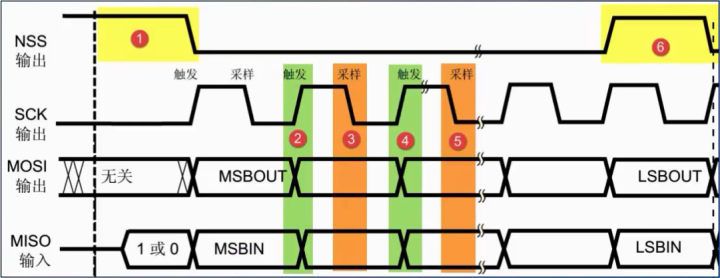

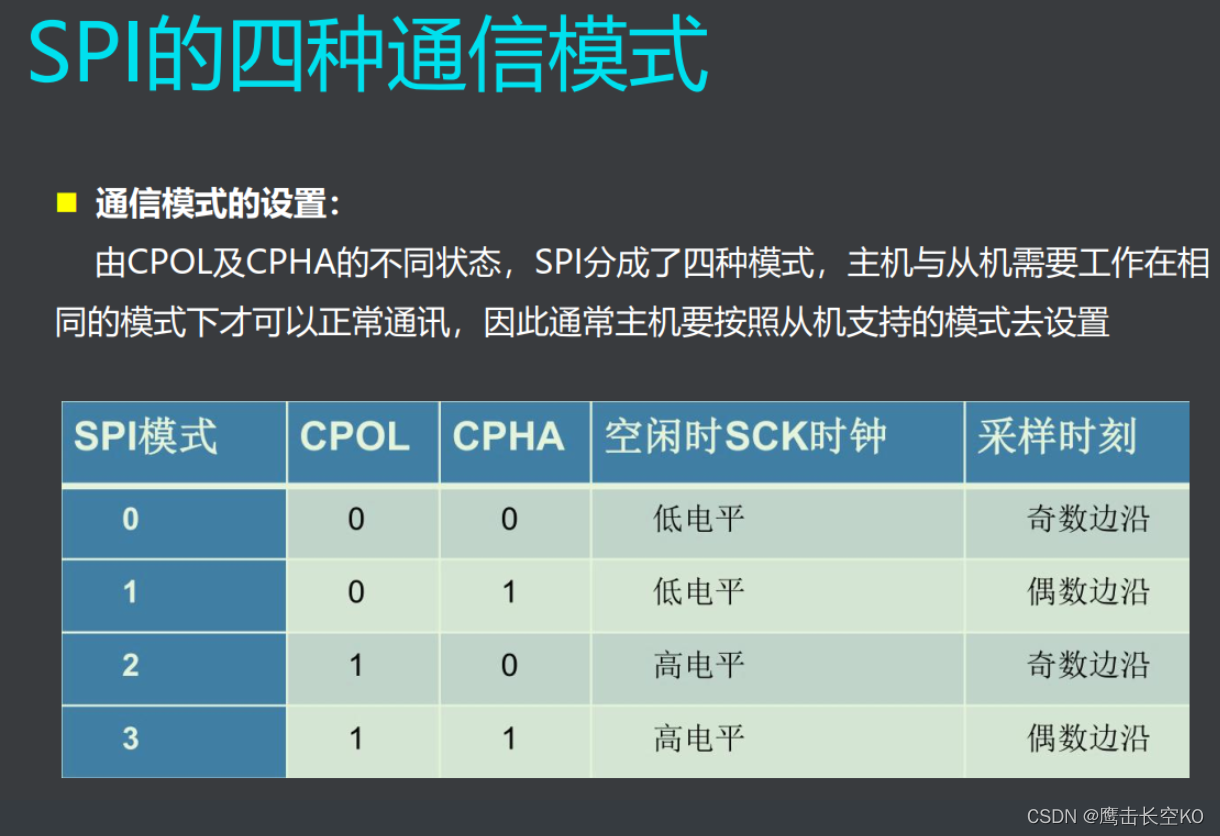

SPI总线有四种工作方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):

图2 SPI0和SPI3方式(实线表示)

四种工作方式时序分别为:

图3 四种工作方式时序

时序详解:

CPOL:时钟极性选择,为0时SPI总线空闲为低电平,为1时SPI总线空闲为高电平

CPHA:时钟相位选择,为0时在SCK第一个跳变沿采样,为1时在SCK第二个跳变沿采样

工作方式1:

当CPHA=0、CPOL=0时SPI总线工作在方式1。MISO引脚上的数据在第一个SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中,首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式2:

当CPHA=0、CPOL=1时SPI总线工作在方式2。与前者唯一不同之处只是在同步时钟信号的下降沿时捕捉位信号,上升沿时下一位数据上线。

工作方式3:

当CPHA=1、CPOL=0时SPI总线工作在方式3。MISO引脚和MOSI引脚上的数据的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中,在同步时钟信号周期开始时(上升沿)数据上线,然后在同步时钟信号的下降沿时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束时(上升沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式4:

当CPHA=1、CPOL=1时SPI总线工作在方式4。与前者唯一不同之处只是在同步时钟信号的上升沿时捕捉位信号,下降沿时下一位数据上线。

4.SPI总线常见错误

4.1 SPR设定错误

在从器件时钟频率小于主器件时钟频率时,如果SCK的速率设得太快,将导致接收到的数据不正确(SPI接口本身难以判断收到的数据是否正确,要在软件中处理)。

整个系统的速度受三个因素影响:主器件时钟CLK主、从器件时钟CLK从和同步串行时钟SCK,其中SCK是对CLK主的分频,CLK从和CLK主是异步的。要使SCK无差错无遗漏地被从器件所检测到,从器件的时钟CLK从必须要足够快。下面以SCK设置为CLK主的4分频的波形为例,分析同步串行时钟、主时钟和从时钟之间的关系。

图4主从时钟和SCK的关系

如图4所示,当T<tsck/2,即t从<2t主时,无论主时钟和从时钟之间的相位关系如何,在从器件clk从的上升沿必然能够检测到sck的低电平,即sck=0的范围内至少包含一个clk从的上升沿。<="" p="">从<tsck 2,即t从<2t主时,无论主时钟和从时钟之间的相位关系如何,在从器件clk从的上升沿必然能够检测到sck的低电平,即sck=0的范围内至少包含一个clk从的上升沿。=""

图5中,当T从≥TSCK/2=2T主时,在clk_s的两个上升沿都检测不到SCK的低电平,这样从器件就会漏掉一个SCK。在某些相位条件下,即使CLK从侥幸能检测到SCK的低电平,也不能保证可以继续检测到下一个SCK。只要遗漏了一个SCK,就相当于串行数据漏掉了一个位,后面继续接收/发送的数据就都是错误的了。

图5主从时钟和SCK的关系

根据以上的分析,SPR和主从时钟比的关系如表1所列。

表1 SPR的设置和主从时钟周期比值之间的关系

在发送数据之前按照表1对SPR进行设置,SPR设定错误可以完全避免。

4.2 模式错误(MODF)

模式错误表示的是主从模式选择的设置和引脚SS的连接不一致。

器件工作在主模式的时候(MSTR=1),它的片选信号SS引脚必须接高电平。在发送数据的过程中,如果它的SS从高电平跳至低电平,在SS的下降沿,SPI模块将检测到模式错误,对MODF位置1,强制器件从主模式转入从模式(即令MSTR=0),清空内部计数器counter,并结束正在进行的数据传输,如图6(a)所示。

对从模式(MSTR=0),在没有数据传送的时候,SS高电平表示从器件未被选中,从器件不工作,MISO输出高阻;在数据传输过程中,片选信号SS必须接低电平,且SS不允许跳变。如果SS从低电平跳到高电平,在SS的上跳沿,SPI模块也将检测到模式错误,清空内部计数器counter,并结束正在进行的数据传输。直到SS恢复为低电平,重新使SPEN=1时,才重新开始工作,如图6(b)所示。

图6模式错误的检测

4.3 溢出错误(OVR)

溢出错误表示连续传输多个数据时,后一个数据覆盖了前一个数据而产生的错误。

状态标志SPIF表示的是数据传输正在进行中,它对数据的传输有较大的影响。主器件的SPIF有效由数据寄存器的空标志SPTE=0产生,而从器件的SPIF有效则只能由收到的第一个SCK的跳变产生,且又由于从器件的SPIF和主器件发出的SCK是异步的,因此从器件的传输标志SPIF从相对于主器件的传输标志SPIF主有一定的滞后。如图7所示,在主器件连续发送两个数据的时候将有可能导致从器件的传输标志和主器件下一个数据的传输标志相重叠(图7中虚线和阴影部分),第一个收到的数据必然被覆盖,第二个数据的收/发也必然出错,产生溢出错误。

图7溢出错误

通过对从器件的波形分析发现,counter=8后的第一个时钟周期,数据最后一位的传输已经完成。在数据已经收/发完毕的情况下,counter=8状态的长短对数据的正确性没有影响,因此可以缩短counter=8的状态,以避免前一个SPIF和后一个SPIF相重叠。这样,从硬件上避免了这一阶段的溢出错误。

但是,如果从器件工作速度不够快或者软件正在处理其他事情,在SPI接口接收到的数据尚未被读取的情况下,又接收到一个新的数据,溢出错误还是会发生的。此时,SPI接口保护前一个数据不被覆盖,舍弃新收到的数据,置溢出标志OVR=1;另外发出中断信号(如果该中断允许),通知从器件及时读取数据。

4.4 偏移错误(OFST)

SPI接口一般要求从器件先工作,然后主器件才开始发送数据。有时在主器件往外发送数据的过程中,从器件才开始工作,或者SCK受到外界干扰,从器件未能准确地接收到8个SCK。如图8所示,从器件接收到的8个SCK其实是属于主器件发送相邻的两个数据的SCK主。这时,主器件的SPIF和从器件的SPIF会发生重叠,数据发生了错位,从器件如果不对此进行纠正的话,数据的接收/发送便一直地错下去。

图8偏移错误

在一个数据的传输过程中,SPR是不允许改变的,即SCK是均匀的,而从图5可以看出,从器件接收到的8个SCK并不均匀,它们是分别属于两个数据的,因此可以计算SCK的占空时间来判断是否发生了偏移错误。经分析,正常时候SCK=1时的时钟周期数n的取值满足如下关系:

但由于主从时钟之间是异步的,并且经过了取整,所以正常时候SCK=1时的时钟周期计数值COUNT应满足:

比如在图5中,COUNT的最大值COUNT(max)=2或者1,都可认为是正常的。但当出现COUNT(max)=8时,可以判定出现了偏移错误。在实际设计中,先记录下第一个COUNT(max)的值,如果后面又出现与记录值相差1以上的COUNT(max)出现,可知有偏移错误OFST发生。SPI接口在“不均匀”的地方令SPIF=1,然后准备等待下一个数据的第一个SCK。其中COUNT的位数固定为8位,为了避免溢出时重新从00H开始计数,当计数达到ffH时停止计数。

4.5 其他错误

设定不当,或者受到外界干扰,数据传输难免会发生错误,或者有时软件对错误的种类判断不清,必须要有一种方法强制SPI接口从错误状态中恢复过来。在SPI不工作,即SPEN=0的时候,清除SPI模块内部几乎所有的状态(专用寄存器除外)。如果软件在接收数据的时候,能够发现数据有错误,无论是什么错误,都可以强制停止SPI的工作,重新进行数据传输。例如,在偏移错误(OFST)中,如果SPR2、SPR1和SPR0的设置适当,也可以使SCK显得比较“均匀”。SPI接口硬件本身不可能检测到有错误,若用户软件能够发现错误,这时就可以强制停止SPI的传输工作,这样就可以避免错误一直持续下去。

在应用中,如果对数据的正确性要求较高,除了要在软件上满足SPI接口的时序要求外,还需要在软件上作适当的处理。

5.设计SPI总线控制器

目前的项目中使用了SPI总线接口的FLASH存储器存储图像数据。FLASH的SPI总线频率高达66M,但MCU的频率较低,晶振频率7.3728M,SPI最大频率为主频1/2。对于320*240*16的图像读取时间为333ms,而且还忽略了等待SPI传输完成、写显存、地址坐标设定等时间。实际测试约为1s。成为GUI设计的极大瓶颈。由于TFT驱动是自己FPGA设计的,资源尚有余量,决定把SPI控制器(主)及写图像部分逻辑放入FPGA中用硬件完成。

首先接触到的是SPI的SCK时钟频率问题。FPGA的频率是48M,未使用PLL。能否以此频率作为SCK频率呢?要知道所有的MCU提供的SPI频率最大为主频的1/2!为什么呢?查过一些资料后发现,SPI从机接收数据并不是以SCK为时钟的,而是以主频为时钟对SCK和MISO进行采样,由采样原理得知SCK不能大于1/2主频,也就有了MCU提供最大master频率是1/2主频,最大slaver频率是1/4主频。FPGA在只作为主机时能否实现同主频一样频率的SCK呢??答案貌似是肯定的!但我还是有点担心,用组合逻辑控制SCK会不会出现较大毛刺影响系统稳定性呢?

图6模式错误的检测

4.3 溢出错误(OVR)

溢出错误表示连续传输多个数据时,后一个数据覆盖了前一个数据而产生的错误。

状态标志SPIF表示的是数据传输正在进行中,它对数据的传输有较大的影响。主器件的SPIF有效由数据寄存器的空标志SPTE=0产生,而从器件的SPIF有效则只能由收到的第一个SCK的跳变产生,且又由于从器件的SPIF和主器件发出的SCK是异步的,因此从器件的传输标志SPIF从相对于主器件的传输标志SPIF主有一定的滞后。如图7所示,在主器件连续发送两个数据的时候将有可能导致从器件的传输标志和主器件下一个数据的传输标志相重叠(图7中虚线和阴影部分),第一个收到的数据必然被覆盖,第二个数据的收/发也必然出错,产生溢出错误。

图7溢出错误

通过对从器件的波形分析发现,counter=8后的第一个时钟周期,数据最后一位的传输已经完成。在数据已经收/发完毕的情况下,counter=8状态的长短对数据的正确性没有影响,因此可以缩短counter=8的状态,以避免前一个SPIF和后一个SPIF相