【1】SPI总线相关的概念

1》SPI接口是Motorola 首先提出的全双工同步串行外围接口,采用主从模式(Master Slave)架构; 2》支持多slave模式应用,一般仅支持单Master。 3》时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first); 4》SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。 5》SPI总线被广泛地使用在FLASH、 ADC、 LCD等设备与MCU间,要求通讯速率较高的场合。

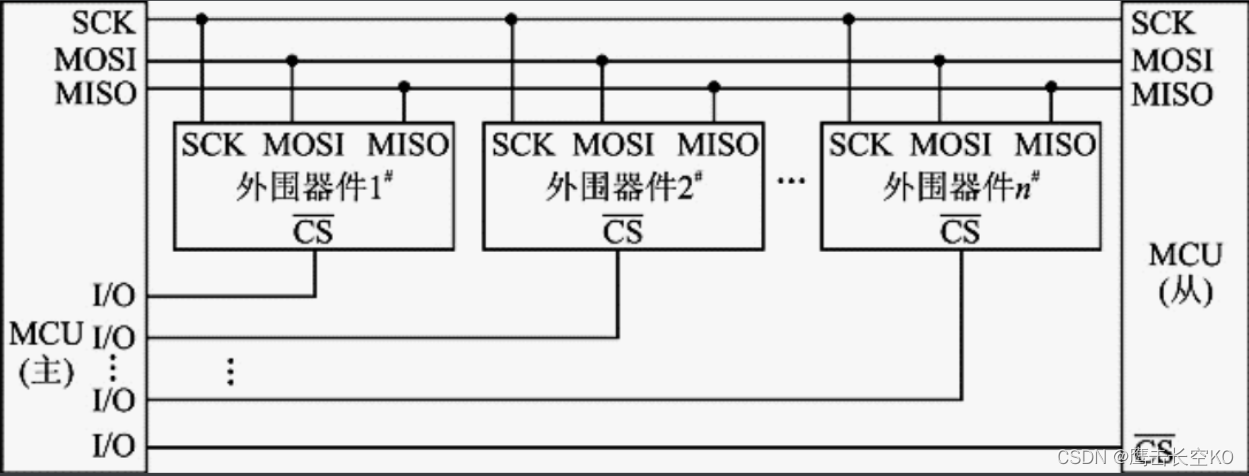

【2】SPI总线的硬件连接

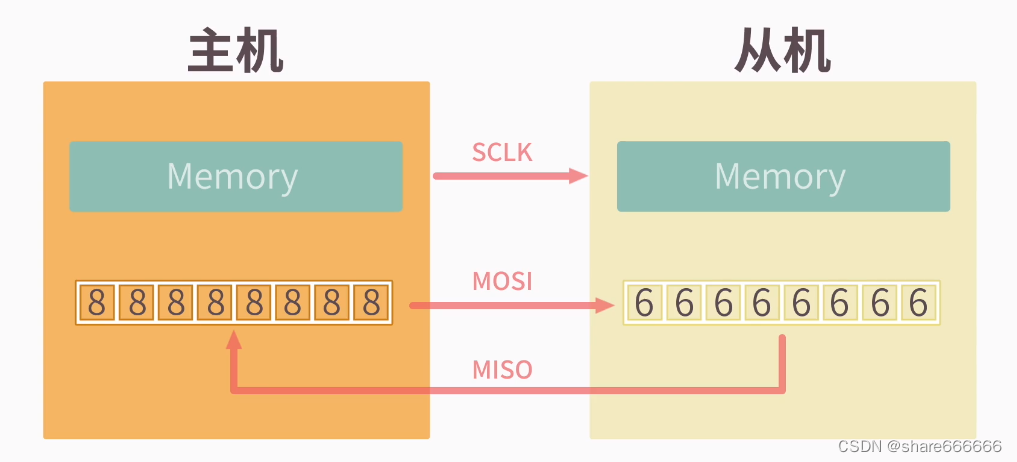

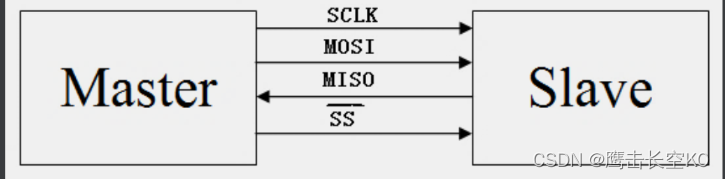

SPI接口共有4根信号线,分别是:设备选择线/片选线:用于选择主机和那个从机通信__ __cs ss nss ncs : 低电平有效时钟线 : 主机给从机提供同步时钟信号 CLK SCL SCLK SCK 串行输出数据线(单向数据线) : 输出数据MOSI : Master Output Slave Input (主机输出,从机输入)串行输入数据线(单向数据线) :输入数据MISO : Master Input Slave Output (主机输入,从机输出)

SPI总线的三线制:单主机,单从机

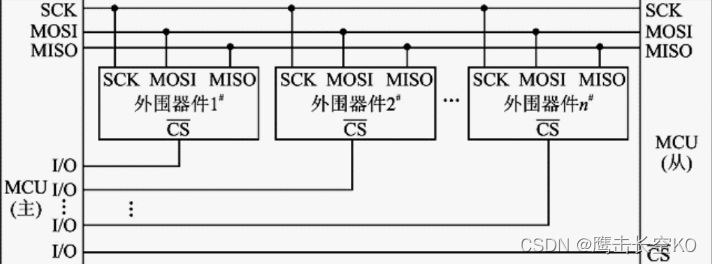

SPI总线的四线制:单主机,多从机

【3】SPI总线的通信协议

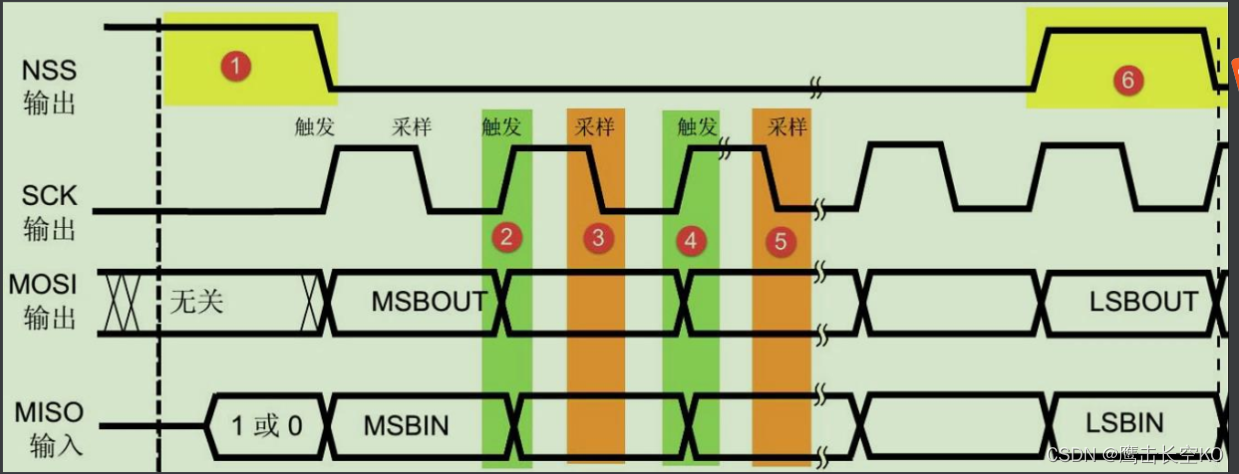

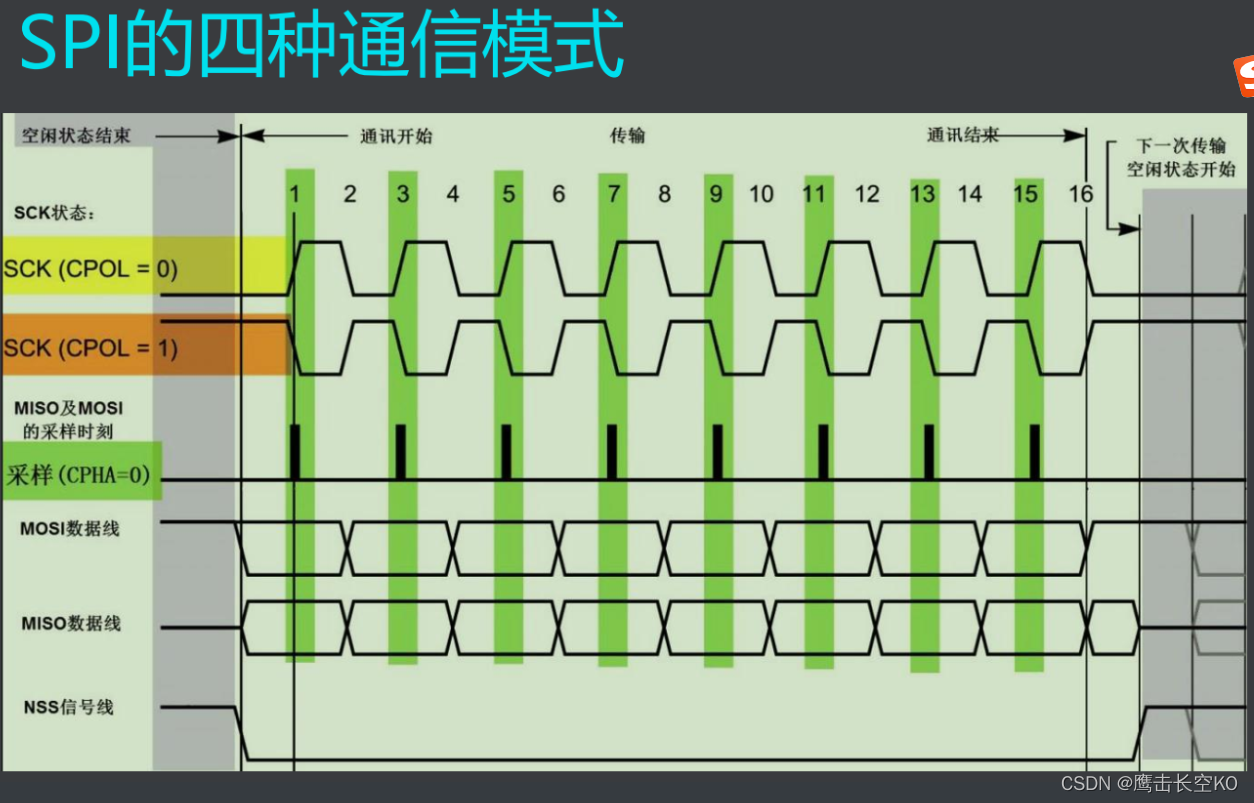

1》起始信号: NSS信号线由高变低,是SPI通讯的起始信号 2》结束信号: NSS信号由低变高,是SPI通讯的停止信号 3》 数据传输: SPI使用MOSI及MISO信号线来传输数据,使用SCK信号线进行数据同步。 MOSI及MISO数据线在SCK的每个时钟周期传输一位数据,且数据输入输出是同时进行 的。 SPI每次数据传输可以 8 位或 16 位为单位,每次传输的单位数不受限制。

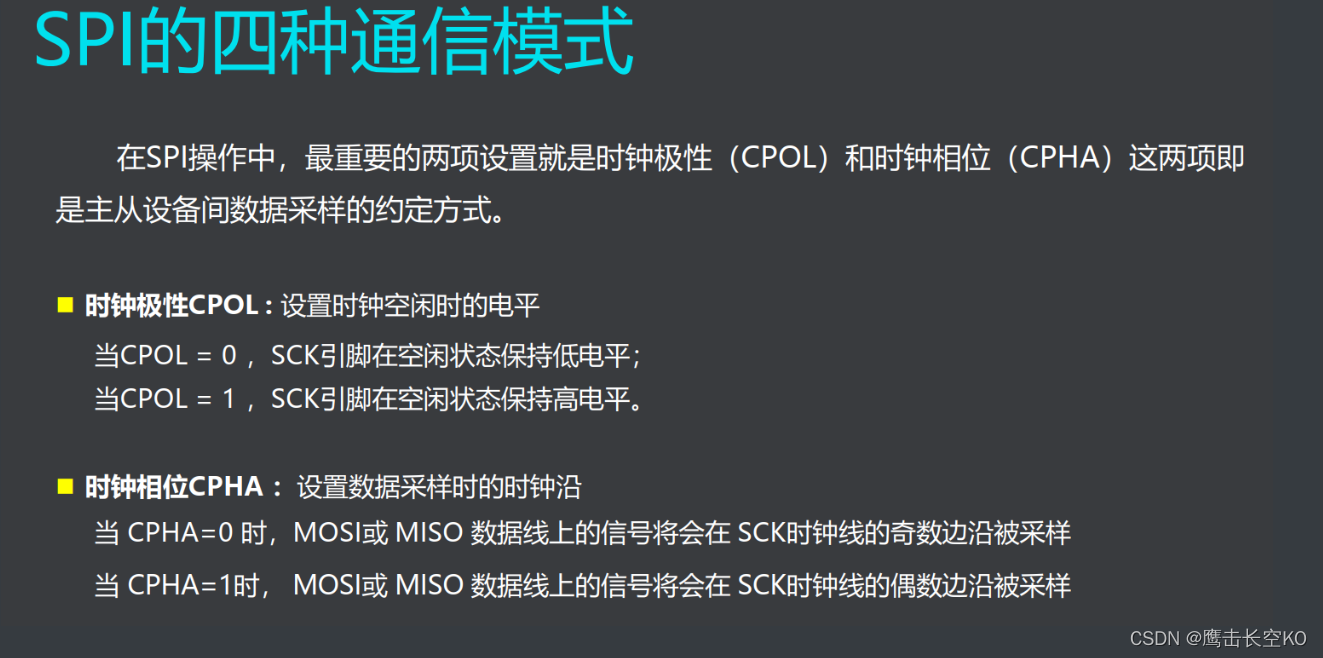

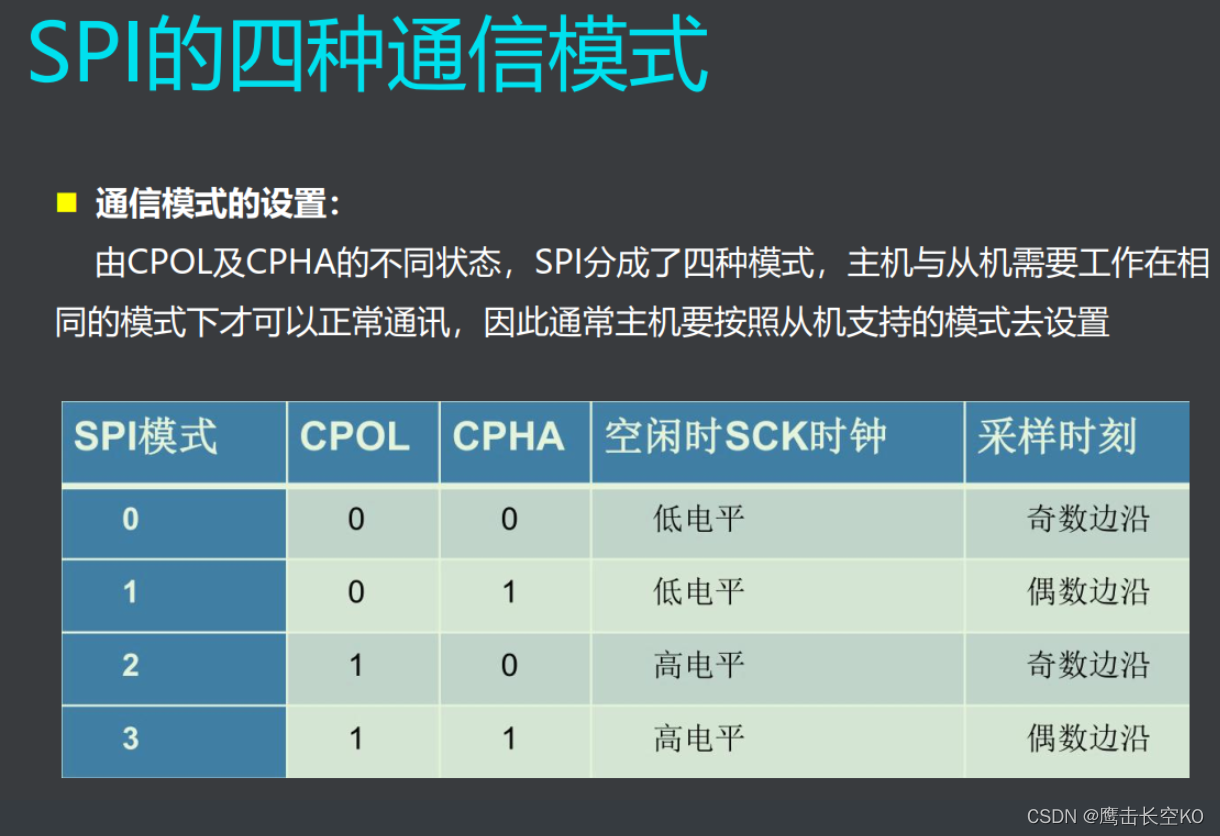

面试重点: 不需要记SPI总线的时序图。 需要掌握SPI总线有4种通信模式,跟时钟的极性和相位有关 时钟极性(CPOL):时钟信号在空闲态的电平状态 时钟相位(CPOA):在时钟的奇数边沿还是偶数边沿进行采样。