目录

SPI简介

SPI4种模式:

SPI时序

使用SPI总线实现对flash的控制

flash芯片管脚:

flash芯片存储

写使能模块

读状态模块

擦除模块

页读模块

页写模块

SPI简介

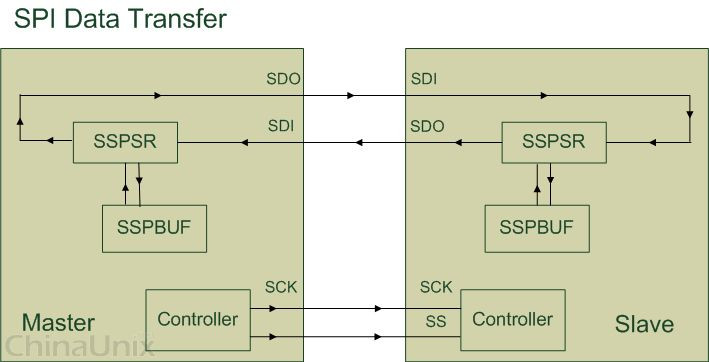

SPI, Serial Perripheral Interface, 串行外围设备接口, 是 Motorola 公司推出的一种同步串行接口技术. SPI 总线在物理上是通过接在外围设备微控制器(PICmicro) 上面的微处理控制单元 (MCU) 上叫作同步串行端口(Synchronous Serial Port) 的模块(Module)来实现的, 它允许 MCU 以全双工的同步串行方式, 与各种外围设备进行高速数据通信。

SPI 主要应用在 EEPROM, Flash, 实时时钟(RTC), 数模转换器(ADC), 数字信号处理器(DSP) 以及数字信号解码器之间. 它在芯片中只占用四根管脚 (Pin) 用来控制以及数据传输, 节约了芯片的 pin 数目, 同时为 PCB 在布局上节省了空间. 正是出于这种简单易用的特性, 现在越来越多的芯片上都集成了 SPI技术。

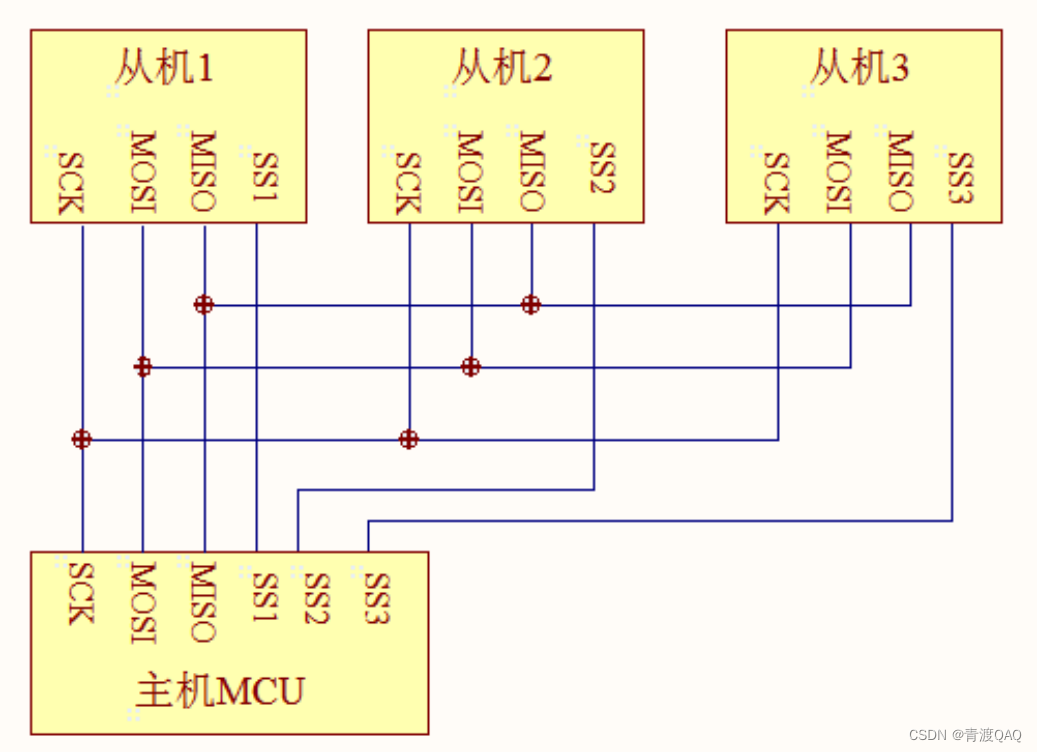

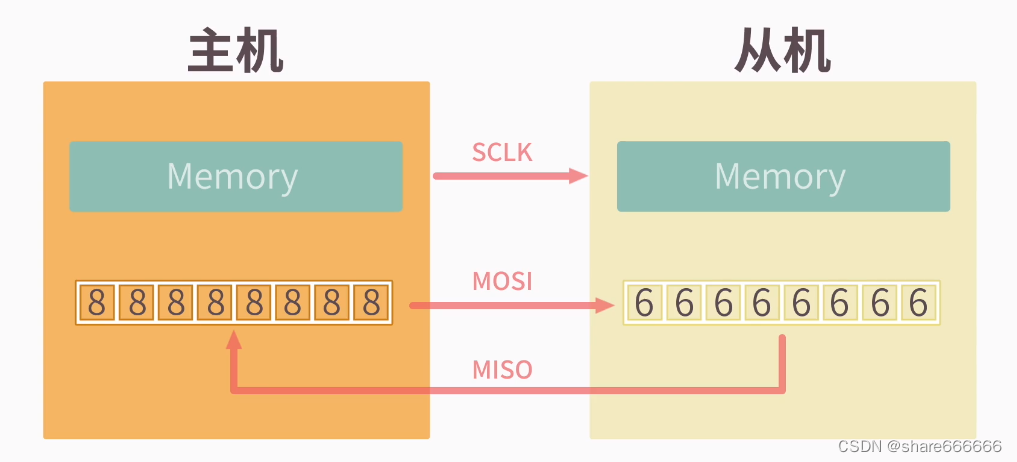

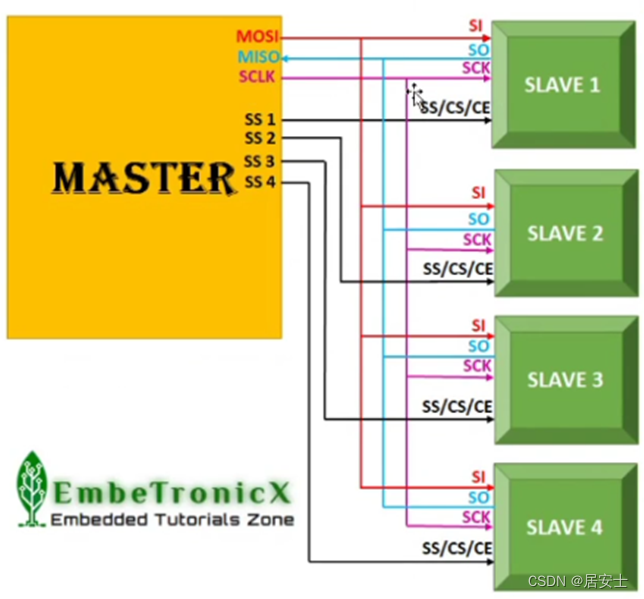

SPI就是串行外围设备接口,它是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,这四根线的定义分别是:

MISO:(master input slave output)主设备数据输入,从设备数据输出;

MOSI:(master output slave input)主设备数据输出,从设备数据输入;

SCLK:(时钟是master给的)时钟信号,由主设备产生;(所以只有mater可以通信ru)

CS :从设备片选信号,由主设备控制。

如上图,可以挂很多个slave,但是一个时刻,只有一个slave跟master进行通信

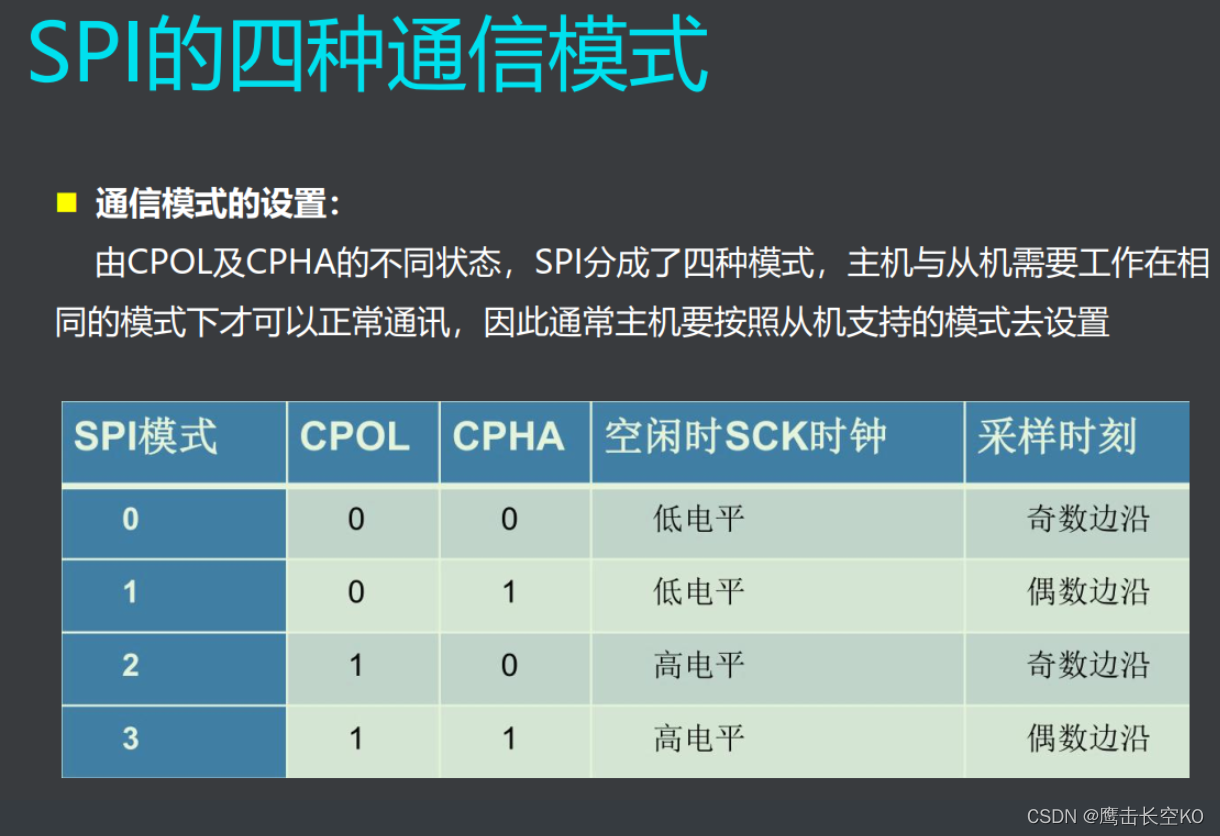

SPI4种模式:

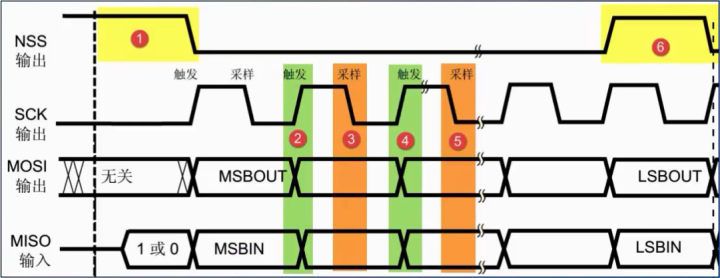

第一个沿接收数据CPHA(clock phase)=0

第二个沿接收数据CPHA(clock phase)=1

空闲时钟为高CPOL(clock polarity)=1

空闲时钟为低CPOL=0

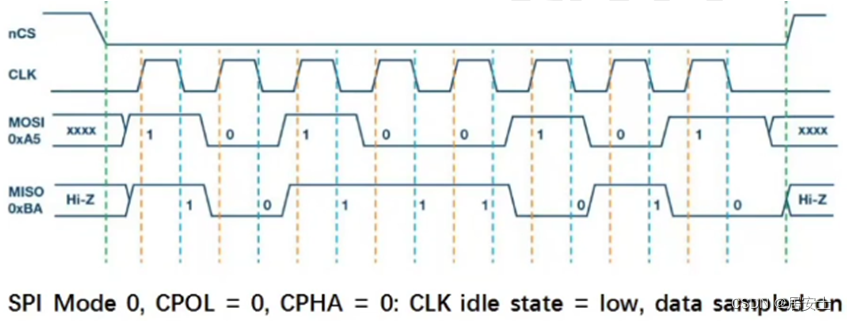

一般使用0模式:时钟空闲为低,第一个时钟沿接收数据

SPI时序

SPI总线处于空闲状态时,片选信号CS要维持高电平,CLK信号为低电平;

当SPI总想开始工作时,首先是片选CS拉低,然后是CLK时钟按照规定的时钟频率输出,传输的数据通过DI数据进行发送;当数据发送完成后,片选CS要拉高代表结束,同时CLK信号输出为低电平。

一个时钟只发送一个bit,一般先发送高位,再发送低位。

使用SPI总线实现对flash的控制

主要实现了对W25Q64FV-Flash芯片的控制功能,该芯片的主要功能有Wr_ebnable(写使能操作)、page_program(页写操作)、erase(擦除操作)、read_status(读状态操作)、read_data(读数据操作)。

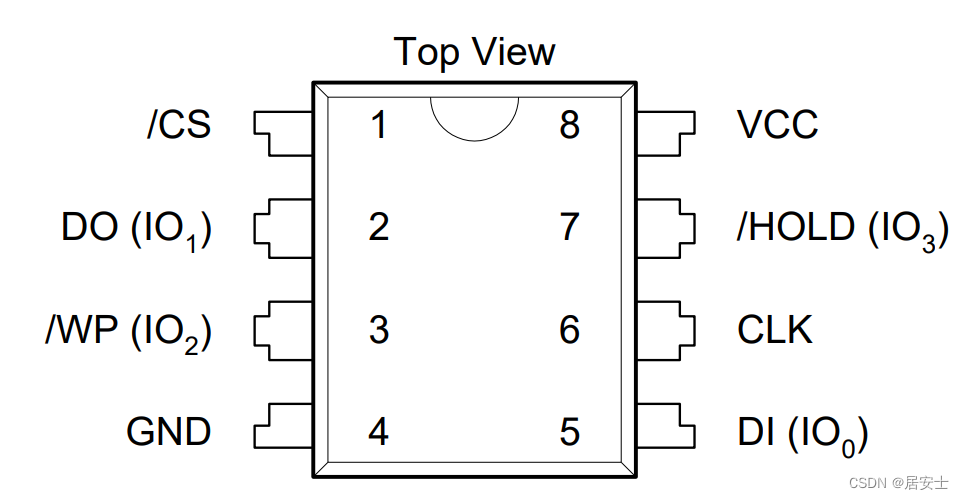

flash芯片管脚:

包括片选信号,数据输入输出信号,时钟和地,输入保持信号,写保护信号

flash芯片存储

W25Q64FV-Flash芯片有128个块,每个块里面有16个扇区,每个扇区有16页,一页256个字节

所以总的存储空间为:一共的字节(128*16*168*256)÷1024(K)÷1024(M)=8MB=64Mbit

写使能模块

写使能时序图:

当片选线拉低了,开始向总线输出DI(06h/04h),输出clk采集数据

读状态模块

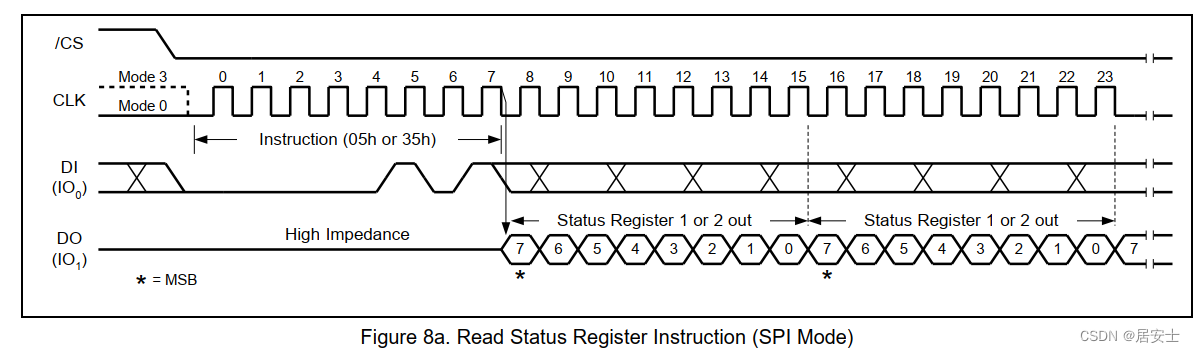

读取状态寄存器指令允许读取 8 位状态寄存器。

通过将 /CS 驱动为低电平并将状态寄存器 1 的指令代码“05h”或状态寄存器 2 的指令代码“35h”在 CLK 的上升沿移入 DI 引脚来输入指令。 然后,状态寄存器位在 CLK 的下降沿在 DO 引脚上移出,最高有效位 (MSB) 在前,如图所示。

读状态发送指令05h或者35h,发送完成后总线向读状态发送8位读状态寄存器数据,由此可以知道总线的状态。状态寄存器可以连续读取,如图所示。指令通过驱动/CS为高电平完成。

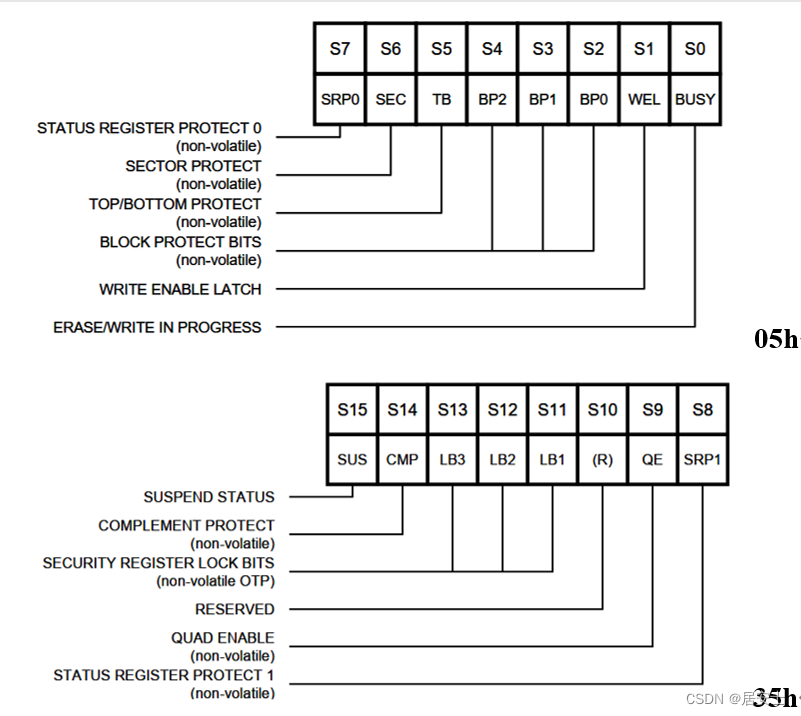

状态寄存器位如图 :

读取状态寄存器指令可随时使用,即使在编程、擦除或写入状态寄存器周期正在进行时。 这允许检查 BUSY 状态位以确定循环何时完成以及设备是否可以接受另一条指令。

擦除模块

擦除分为扇区擦除;32KB擦除;64KB擦除;整片擦除

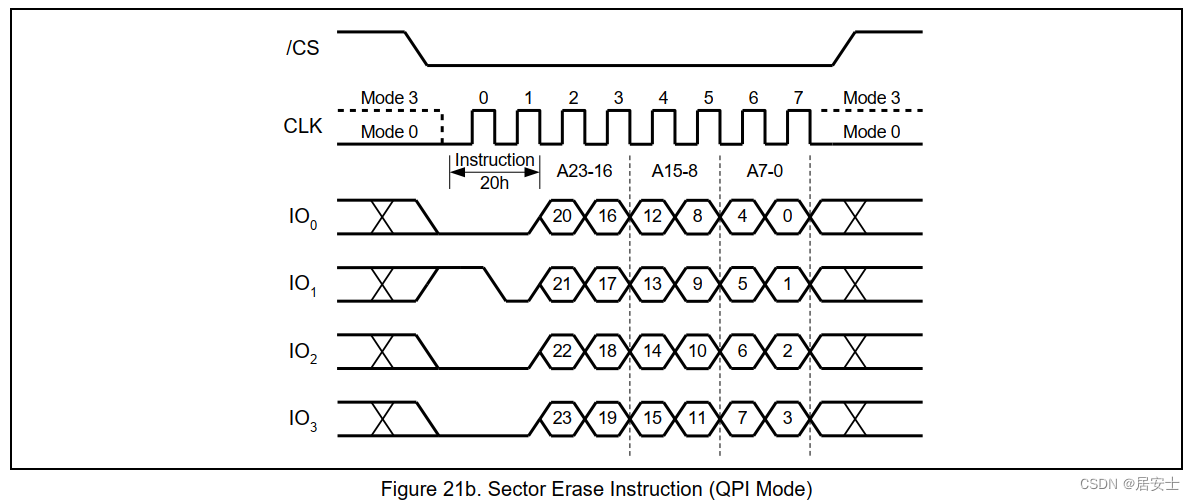

(1)扇区擦除(20h)

除 Sector Erase 指令将指定扇区(4K 字节)内的所有内存设置为全 1(FFh)擦除状态。 在器件接受扇区擦除指令(状态寄存器位 WEL 必须等于 1)之前,必须执行写使能指令。 该指令通过将 /CS 引脚驱动为低电平并将指令代码“20h”移位到 24 位扇区地址 (A23-A0) 来启动(见图 2)。 扇区擦除指令序列如图 21a 和 21b 所示。

在最后一个字节的第八位被锁存后,/CS 引脚必须被驱动为高电平。 如果不这样做,将不会执行扇区擦除指令。 在 /CS 被驱动为高电平后,自定时扇区擦除指令将在 tSE 的持续时间内开始(参见交流特性)。 在扇区擦除周期进行时,仍可访问读取状态寄存器指令以检查 BUSY 位的状态。 BUSY 位在扇区擦除周期中为 1,当周期结束且器件准备好再次接受其他指令时变为 0。 扇区擦除周期完成后,状态寄存器中的写使能锁存 (WEL) 位被清除为 0。如果寻址页面受块保护(CMP、SEC、TB、BP2 、BP1 和 BP0) 位(参见状态寄存器存储器保护表)

(2)擦除32KB(52h)

块擦除指令将指定块(32K 字节)内的所有存储器设置为全 1 (FFh) 的擦除状态。 在器件接受块擦除指令(状态寄存器位 WEL 必须等于 1)之前,必须执行写使能指令。 该指令通过将 /CS 引脚驱动为低电平并将指令代码“52h”移位到 24 位块地址 (A23-A0) 来启动。 块擦除指令序列如图 22a 和 22b 所示。

在最后一个字节的第八位被锁存后,/CS 引脚必须被驱动为高电平。 如果不这样做,将不会执行块擦除指令。 在 /CS 被驱动为高电平后,自定时块擦除指令将在 tBE1 的持续时间内开始(参见交流特性)。 在块擦除周期进行时,仍可访问读取状态寄存器指令以检查 BUSY 位的状态。 BUSY 位在块擦除周期中为 1,当周期结束且器件准备好再次接受其他指令时变为 0。 在块擦除周期完成后,状态寄存器中的写使能锁存 (WEL) 位被清除为 0。

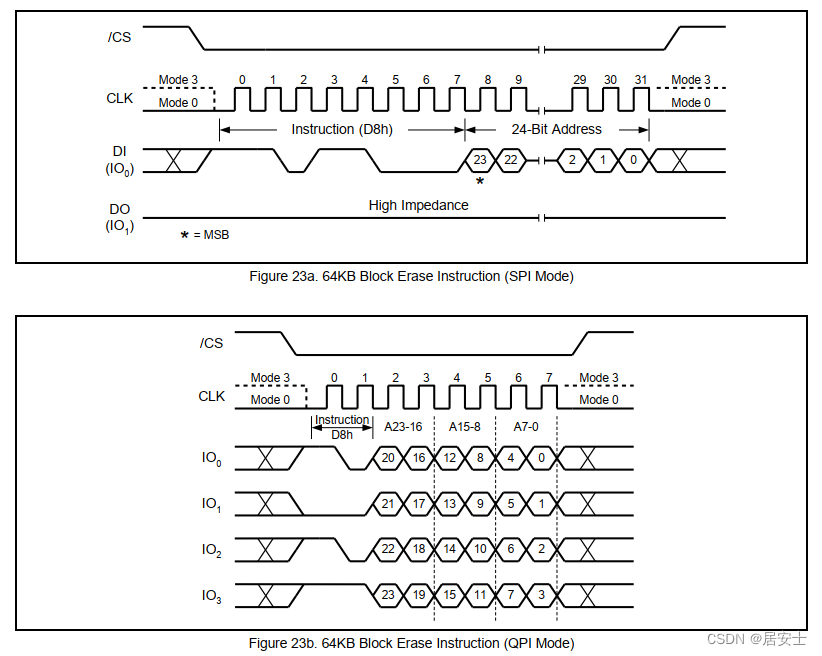

(3)擦除64KB(D8h)

块擦除指令将指定块(64K 字节)内的所有存储器设置为全 1 (FFh) 的擦除状态。 在器件接受块擦除指令(状态寄存器位 WEL 必须等于 1)之前,必须执行写使能指令。 该指令通过将 /CS 引脚驱动为低电平并将指令代码“D8h”移位到 24 位块地址 (A23-A0) 来启动。 块擦除指令序列如图 23a 和 23b 所示。

在最后一个字节的第八位被锁存后,/CS 引脚必须被驱动为高电平。 如果不这样做,将不会执行块擦除指令。

(4)擦除整片(C7h或者06h)

Chip Erase 指令将器件内的所有存储器设置为全 1 (FFh) 的擦除状态。 在器件接受芯片擦除指令(状态寄存器位 WEL 必须等于 1)之前,必须执行写使能指令。 该指令通过将 /CS 引脚驱动为低电平并移位指令代码“C7h”或“60h”来启动。 芯片擦除指令序列如图所示。

页读模块

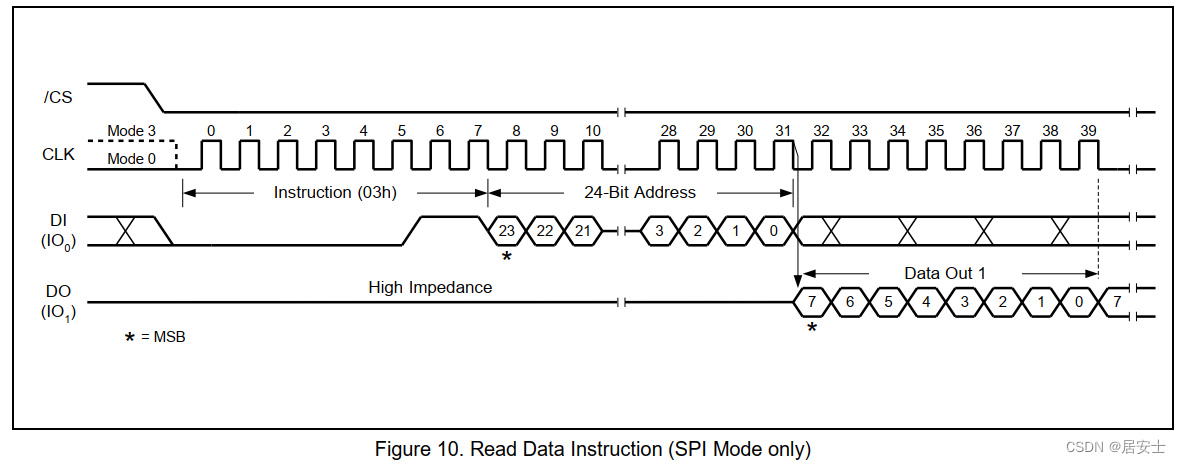

页读指令(03h)

Read Data 指令允许从存储器中顺序读取一个或多个数据字节。 该指令通过将 /CS 引脚驱动为低电平,然后将指令代码“03h”后跟一个 24 位地址(A23-A0)移入 DI 引脚来启动。 代码和地址位在 CLK 引脚的上升沿被锁存。 接收到地址后,寻址存储器位置的数据字节将在 CLK 的下降沿以最高有效位 (MSB) 为先在 DO 引脚上移出。 在每个数据字节移出后,地址会自动递增到下一个更高的地址,从而允许连续的数据流。 这意味着只要时钟继续,就可以通过一条指令访问整个存储器。 该指令通过将 /CS 驱动为高电平来完成。

读取数据指令序列如图 10 所示。如果在擦除、编程或写入周期进行中 (BUSY=1) 时发出读取数据指令,则该指令将被忽略,并且不会对当前周期产生任何影响。 读取数据指令允许从直流到最大 fR 的时钟速率(参见交流电气特性)。

读取数据 (03h) 指令仅在标准 SPI 模式下受支持。

页写模块

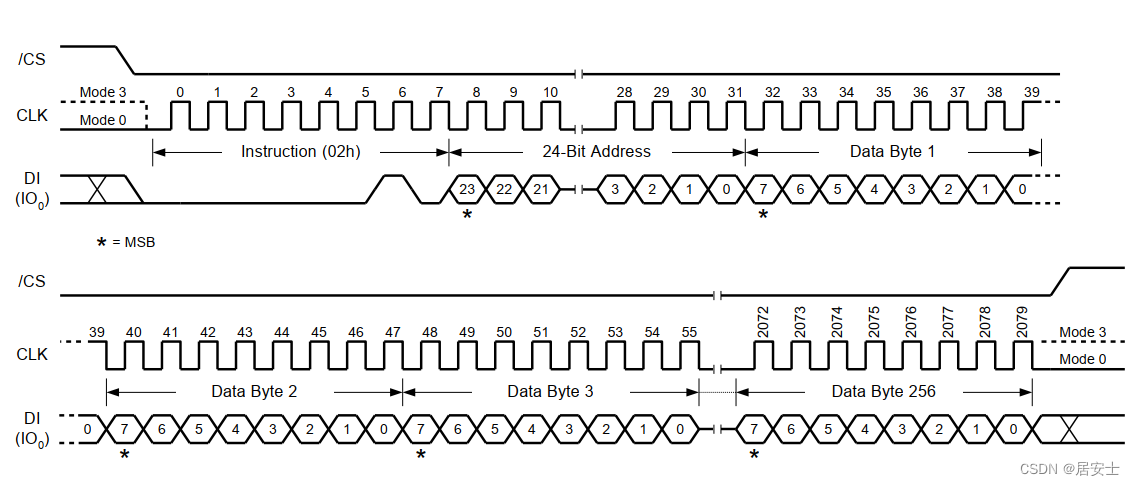

首先发送02H的指令,后面是24位数据首地址,后面至多可以跟256个字节(256*8位)的数据

页写指令只能从一个字节到 256个字节(一页)的数据。如果这一页已经被写了,虽然没写满也不能再写这页了。

在器件接受页写指令(状态寄存器位 WEL=1)之前,必须执行写使能指令。 该指令通过将 /CS 引脚驱动为低电平,然后将指令代码“02h”后跟一个 24 位地址 (A23-A0) 和至少一个数据字节移入 DI 引脚来启动。 当数据被发送到设备时,/CS 引脚必须在指令的整个长度内保持低电平。Page Program 指令序列如图下所示。

如果要对整个 256 字节页面进行编程,则最后一个地址字节(8个最低有效地址位)应设置为 0。如果最后一个地址字节不为零,并且时钟数超过剩余页面长度,则寻址将换行到页面的开头。 在某些情况下,可以编程少于 256个字节(部分页面),而不会对同一页面内的其他字节产生任何影响。 如果发送到设备的字节数超过 256 字节,则寻址将返回到页面的开头并覆盖先前发送的数据。

与写入和擦除指令一样,/CS 引脚必须在最后一个字节的第 8 位被锁存后驱动为高电平。 如果不这样做,将不会执行页面编程指令。在页面编程周期进行时,仍可访问读取状态寄存器指令以检查 BUSY 位的状态。 BUSY 位在页写周期中为 1,当周期结束且器件准备好再次接受其他指令时变为 0。 页写周期完成后,状态寄存器中的写使能锁存 (WEL) 位被清除为 0。