文章目录

- 1. 简介

- 1.1 总线特点

- 1.2 总线接口

- 1.3 拓扑模式

- 2. 传输协议

- 2.1 传输模式

- 2.2 时序图

- 2.3 PCI-X总线基本概念

- 2.4 PCI传输速率

- 3. 小结

1. 简介

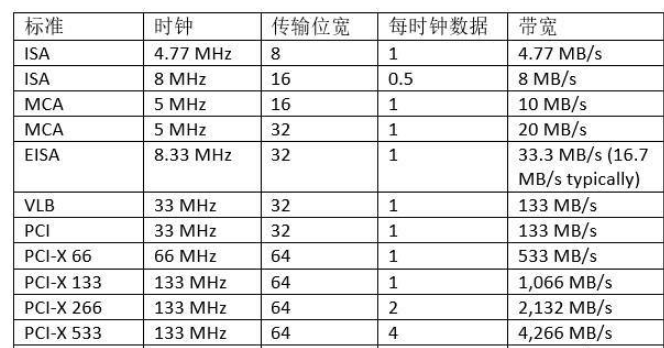

PCI(Peripheral Component Interconnect)总线协议由Intel在1992年提出,是一种局部并行总线,PCI常见的时钟频率为33MHz,32bit位宽,速率为133MB/s,作为扩展接口,主要用于外围设备的连接和扩展,是以前将声音,视频和网卡连接到主板的通用功能方法,但由于这些外设的速度越来越快,CPI总线的传输速度已经不能满足需求了,所以目前都是PCIe接口

1.1 总线特点

- 并行总线,地址和数据共用一个总线。

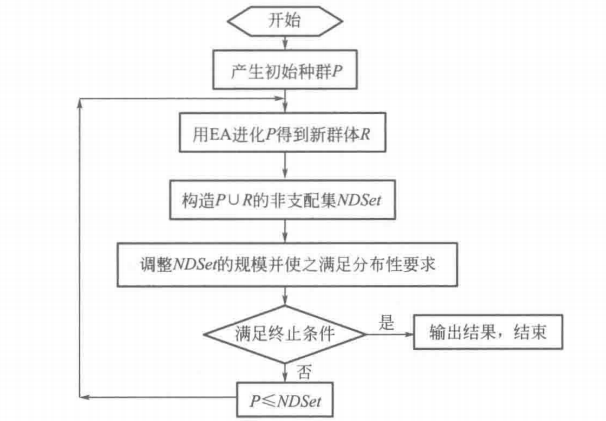

- 由于PCI总线是共享总线,所以需要特定的仲裁器(Arbiter)来决定当前时刻的总线的控制权。一般该仲裁器位于北桥中,而仲裁器(主机)则通过一对引脚,REQ#(request) 和GNT# (grant)来与各个从机连接。如下图所示:

- 最初的PCI总线的时钟频率为33MHz,但是随着版本的更新,时钟频率也逐渐的提高。但是由于PCI采用的是一种Reflected-Wave Signaling信号模型(后面会详细的介绍),导致了时钟频率越高,总线的最大负载越少

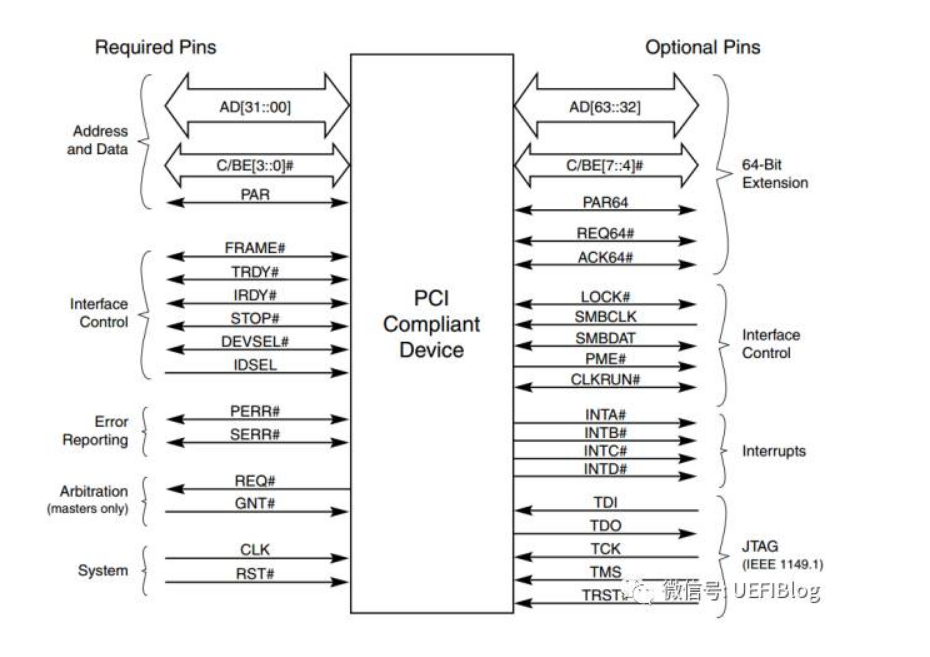

1.2 总线接口

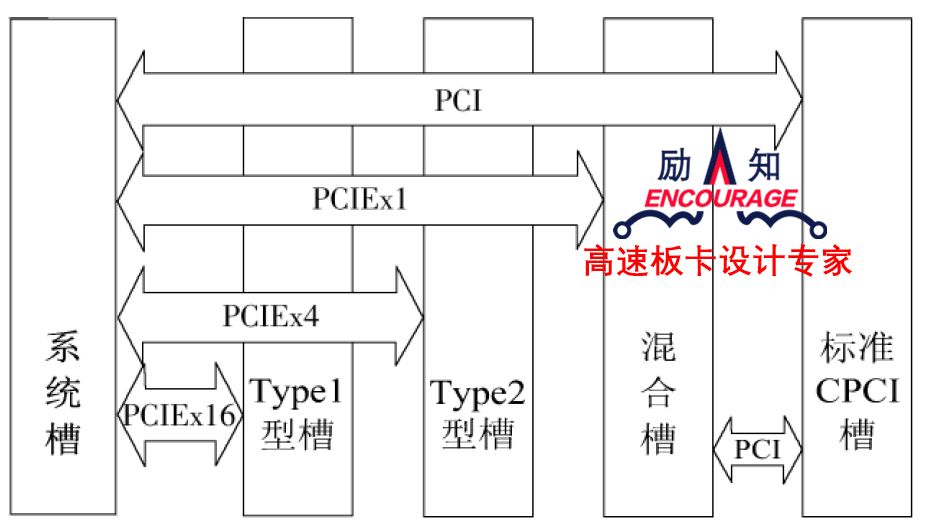

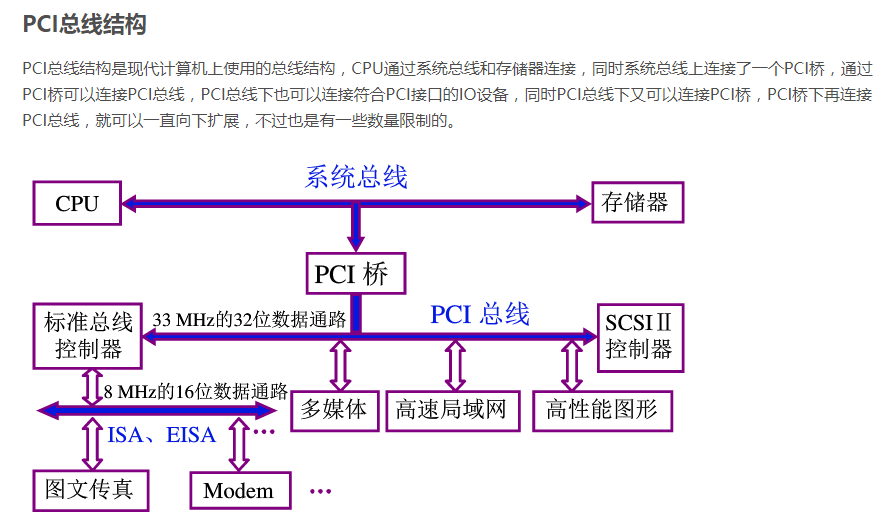

1.3 拓扑模式

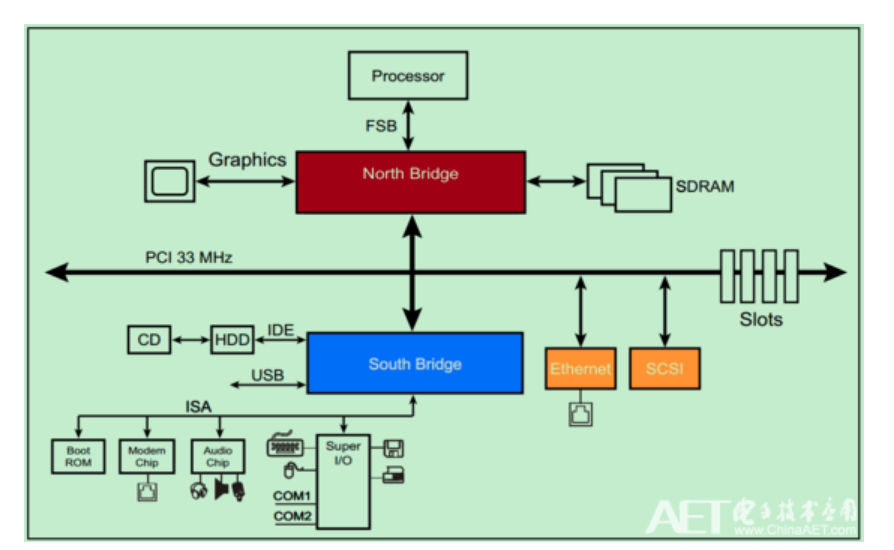

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥,PCI总线上只允许有一个PCI主设备(同一时刻),其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。

注:这并不意味着所有的读写操作都需要通过北桥中转,因为PCI总线上的主设备和从设备属性是可以变化的。

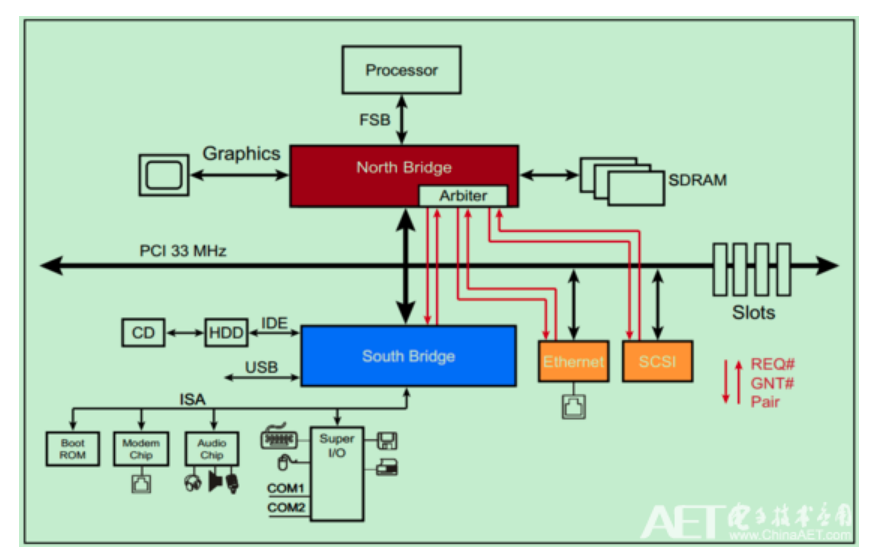

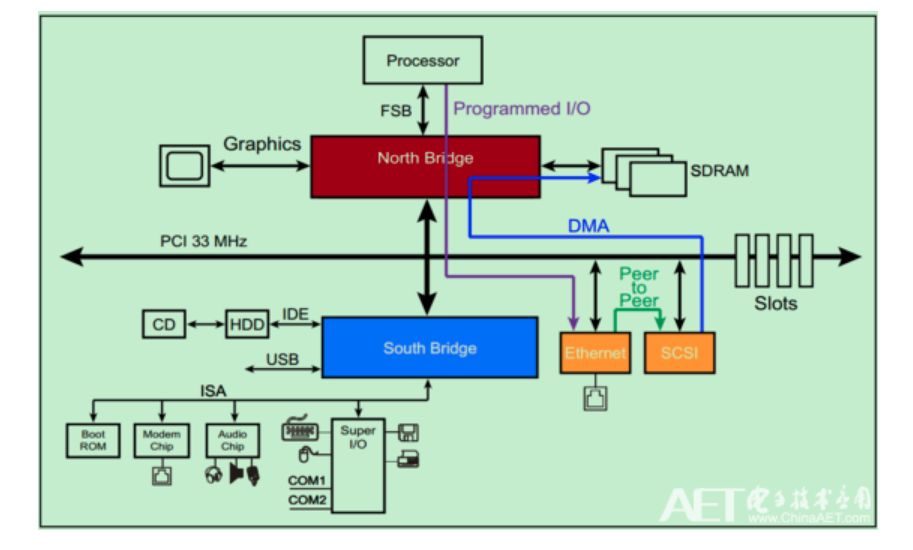

处理器通过FSB与北桥相连接

北桥上挂载着图形加速器(显卡)、SDRAM(内存)和PCI总线

PCI总线上挂载着南桥、北桥、以太网、SCSI总线(一种老式的小型机总线)和若干个PCI插槽

CD和硬盘则通过IDE连接至南桥,音频设备以及打印机、鼠标和键盘等也连接至南桥,此外南桥还提供若干的USB接口

2. 传输协议

2.1 传输模式

PCI Spec规定的三种数据传输模型:Programmed I/O(PIO),Peer-to-Peer和DMA

- Programmed I/O(PIO)

PIO在早期的PC中被广泛使用,因外当时的处理器的速度要远远大于任何其他外设的速度,所以PIO足以胜任所有的任务。比如说某一个PCI设备需要向内存(SDRAM)中写入一些数据,该PCI设备会向CPU请求一个中断,然后CPU首先先通过PCI总线把该PCI设备的数据读取到CPU内部的寄存器中,然后再把数据从内部寄存器写入到内存(SDRAM)中。 - DMA,即Direct Memory Access

DMA是一种在传输过程中,几乎不需要CPU进行干预的数据传输方式。如上面的图片所示,以太网可以直接向内存(SDRAM)中写入数据,而几乎不需要CPU的干预。 - Peer-to-Peer

我们介绍过PCI总线系统中的主机身份并不是固定不变的,而是可以切换的(借助仲裁器),但是同一时刻只能存在一个主机。完成Peer-to-Peer这一传输方式的前提是,PCI总线系统中至少存在一个有能力成为主机的设备。在仲裁器的控制下,完成主机身份的切换,进而获得PCI总线的控制权,然后与总线上的其他PCI设备进行通信。

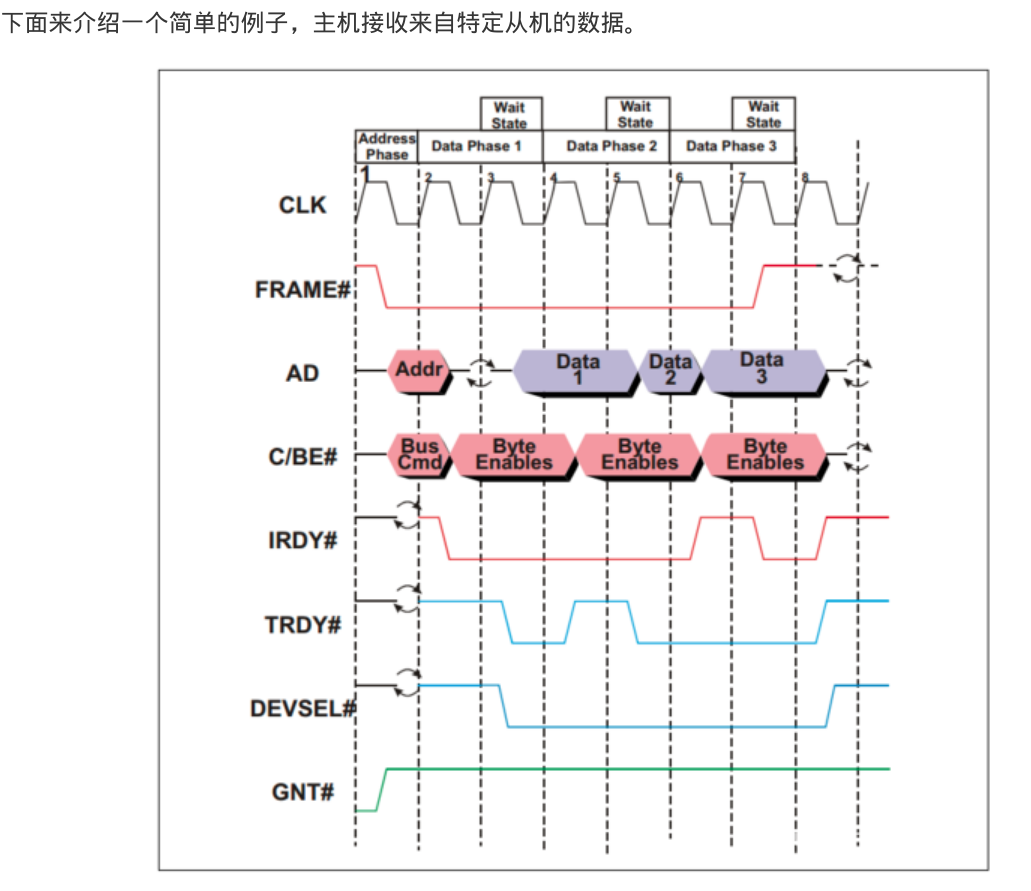

2.2 时序图

- PCI总线是一种地址和数据复用的总线,即地址和数据占用同一组信号线AD。PCI总线的所有信号都与时钟信号同步,及所有的信号的变化都发生在时钟的上升沿,或者在时钟上升沿进行采样。

- 除了时钟信号CLK和数据地址复用信号AD之外,PCI总线至少还应包括FRAME#(用于表示一次数据传输的起始)、C/BE#(Command/Byte Enable)、IRDY#(Initiator Ready for data)、TRDY#(Target ready)、DESEL#(Device Selec,片选信号,用于选择PCI设备)和GNT#(Grant)信号等。

注:完整的信号时序图,请参考PCI Spec。信号名后面的#表示该信号低电平有效。

1、在第一个时钟上升沿,FRAME#和IRDY#都为inactive,表明总线当前处于空闲状态。与此同时,某个设备的GNT#信号处于active,表明总线总裁器已经选定当前设备为下一个initiator(可以理解为主机)。

2、在第二个时钟上升沿,FRAME#被initiator拉低,表明新的事务(Transaction)已经开始。与此同时,地址和命令被依次发送到AD上,总线上面的所有其他设备(从机)都会锁存这些信息,并检查地址和命令是否与自己匹配。

3、在第三个时钟上升沿,IRDY#处于active状态,表明主机准备就绪,可以接收数据了。AD信号上的旋转的箭头表示AD信号目前处于三态状态(处于输出和输入的转换状态),即Turn‐around cycle。需要注意的是,此时的TRDY#应当处于inactive状态,以保证Turn‐around cycle顺利进行。

4、在第四个时钟上升沿,PCI总线上的某个从机确认身份,并依次将DEVSEL#信号和TRDY#拉低,并将相应的数据输出到AD上。此时,FRAME#信号为active状态,表明这并不是最后一个数据。

5、在第五个时钟上升沿,TRDY#处于inactive状态,表明从机尚未就绪,因此所有的操作暂缓一个时钟周期(或者说插入了一个Wait State)。PCI总线最多允许8个这样的Wait State。

6、在第六个时钟上升沿,从机向主机发送第二个数据。此时,FRAME#信号依旧为active状态,表明这并不是最后一个数据。

7、在第七个时钟上升沿,IRDY#处于inactive状态,表明主机尚未就绪,再次插入一个Wait State。但是此时从机依旧可以向AD上发送数据。

8、在第八个时钟上升沿,AD上的第三个数据被发送至主机,由于此时FRAME#信号被拉高,即inactive,表明这是本次事务(Transaction)的最后一个数据。此后,所有的控制信号均被拉高,处于inactive状态,AD、FRAME#和C/BE#处于三态状态。

2.3 PCI-X总线基本概念

从硬件层面上来说,PCI-X继承了PCI总线中的Reflected-Wave Signaling,但是在信号的输入端加入了输入寄存器以增强时序性能,提高了总线的时钟频率。

然而,有意思的是,PCI-X2.0似乎生不逢时,虽然它显著地提高了PCI总线的带宽,但依旧无法掩盖并行总线在高速总线数据传输中劣势。PCI-X2.0总线虽然性能优异,但是却几乎很少得到应用,由于其高功耗高成本,且并行总线的引脚过多,需要极其复杂的PCB设计,导致PCI-X2.0只在极少数高端的市场中得到了应用(如服务器市场等)。导致PCI-X2.0未能达到大规模应用的另一个因素就是PCI Express(PCIe)总线时代的到来,其标志着高速串行总线取代传统的并行总线的时代的开端。

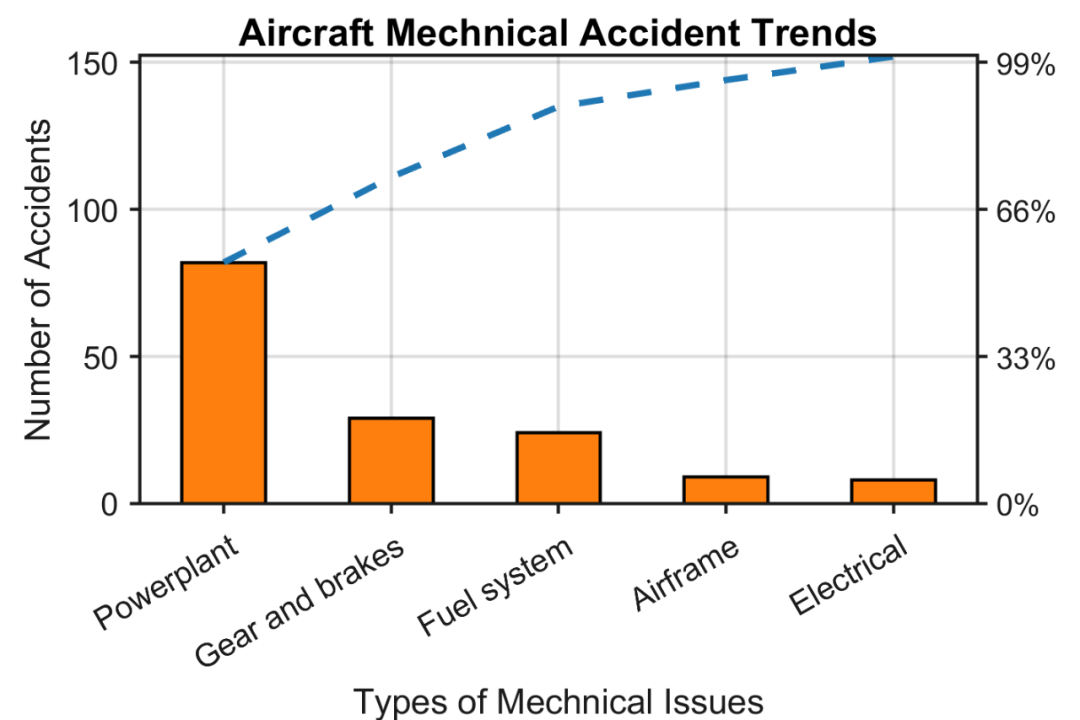

2.4 PCI传输速率

3. 小结

PCI总线是一种并行总线,独立于系统总线,PCI空间与处理器空间隔离,处理器需要通过Host bridge才能访问PCI设备,而PCI设备需要通过Host bridge才能主存储器。并且在Host bridge中含有许多缓冲,这些缓冲使得处理器总线与PCI总线工作在各自的时钟频率中。

参考链接:

https://zhuanlan.zhihu.com/p/26172972