计算机技术发展十分迅速,三十年前,一间房子大小的小型机的算力,到现在还比不上大家手机CPU的算力。令人吃惊的是,有这么一种38年前的技术,现在还在大家的电脑中运用十分广泛,甚至它的控制器在计算机中的个数在过去五年中增长了两倍,这项技术就是I2C (Inter-Integrated Circuit,IIC)总线。

就在某些新入行的同学还在纠结I2C和计算机中另一个相似总线SMBus的区别的时候,另一种替代I2C的新总线I3C已经出现在地平线上。春江水暖鸭先知,跟踪最新技术的朋友也许已经在Intel路线图和DDR5内存规格书中看到了这个名字了。现在是时候最后分清楚I2C和SMBus的区别,为I3C的到来做好准备了。

I2C vs SMBus?

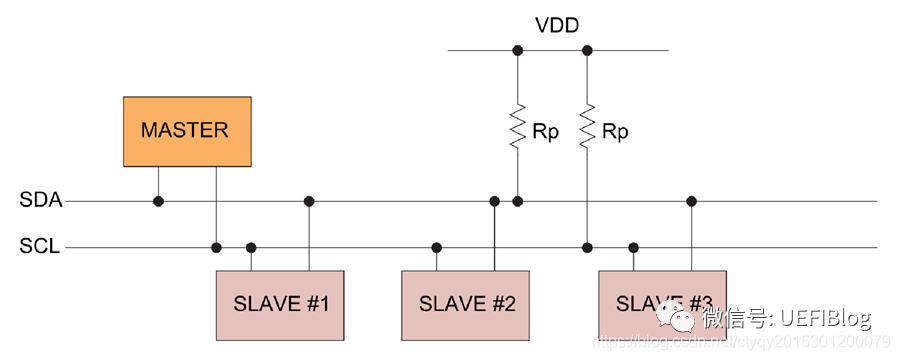

I2C(Inter-Integrated Circuit,IIC) 最初由飞利浦(Philips)半导体(后并入NXP)在1982年提出,主要目的是提供一种简单的、成本低廉的串行总线,用于MCU和电视机原件进行通信。它在最初是由一个Master(可以多Master)和可以多达127个Slave在由两根线(SDA, SCL)组成的总线上进行通讯。

这样MCU就可以不用再单独和各个设备通讯,而仅仅用两根线就可以和所有外围设备愉快的通话了。这两根线分别是数据线(SDA)和时钟线(SCL)。如此这般,大大节约了芯片引脚数目,方便主板布线,节省了整体成本。良好的设计,慢慢让它得到了广泛应用。这些年下来,I2C从省电和提高速度方面进行了三次版本升级,速度从10KHz提高到最高可达5MHz。现在计算机领域,大多数低速设备都是靠I2C通讯:大多数传感器的数据读取界面是I2C;Clock芯片CK404界面是I2C;内存条SPD信息的读取界面是I2C;有些控制器的界面是I2C,等等。随着速度提高,有些中速设备也是I2C:经常遇到的例子是笔记本电脑的触摸板(Touch Pad)和触摸屏(Touch Panel),只不过界面是HS I2C。

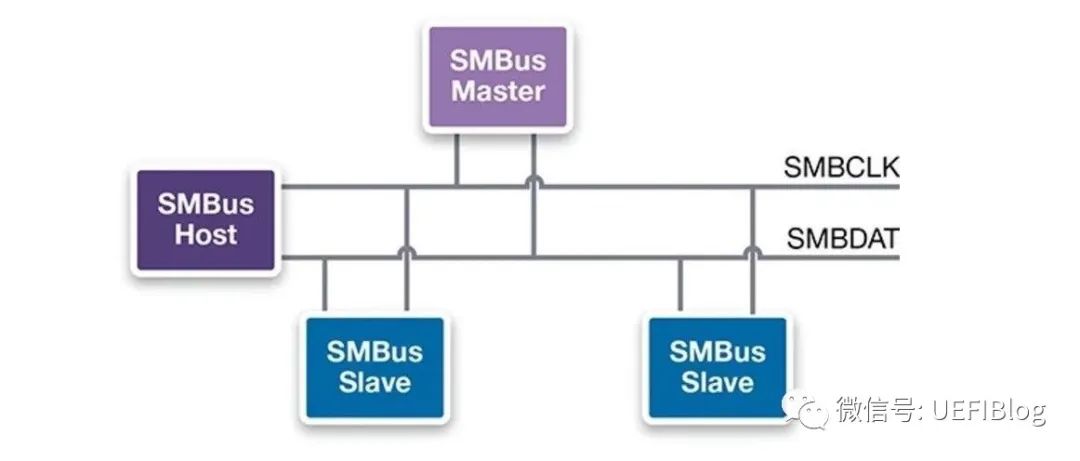

电脑里面常有的一个容易混乱的相似总线是SMBus,它由Intel在1995发布,最早用于和智能电池的通讯,后也经过三次提高,于2000年左右成熟后一直变化不大。SMBus脱胎于I2C,他可以说是I2C的一个子集。它在大部分情况下,也由一个Master(可以多Master)和众多Slave组成,用两根线(SMBDAT和SMBCLK)进行通讯:

I2C和SMBus两者在一般应用下,区别不大,甚至大多数情况下互用也没有问题。更让人迷惑的是,两者可以同时出现在一些设计中,这让一些同学相当疑惑,两者到底有什么区别?在I2C上重新发明一遍轮子有何意义呢?

答案在于I2C偏重速度,而SMBus偏重可靠性和成本。I2C速度从10KHz起步(理论上可以更低至0),最高5MHz;而SMBus最低10KHz,最高100KHz。也就是说在10KHz到100KHz上,两者才通用,这就排除了中速和高速设备。I2C不强制Slave对地址请求发送回应(ACK),而SMBus要求必须ACK。于此对应,SMBus对NACK的要求也严格于I2C。这是因为SMBus面向电脑中很多可拆卸设备,必须确定该设备是否存在,避免误操作。SMBus还加入了WatchDog,在SMBCLK拉低后,不得超过35ms(这就是10KHz的最低频率的由来),否则Slave应该Reset。而I2C并没有该限制。这让SMBus避免了复杂的错误恢复电路。SMBus还提供了单独的SMBSUS来用于Slave向Master报警。

I2C有什么缺陷?

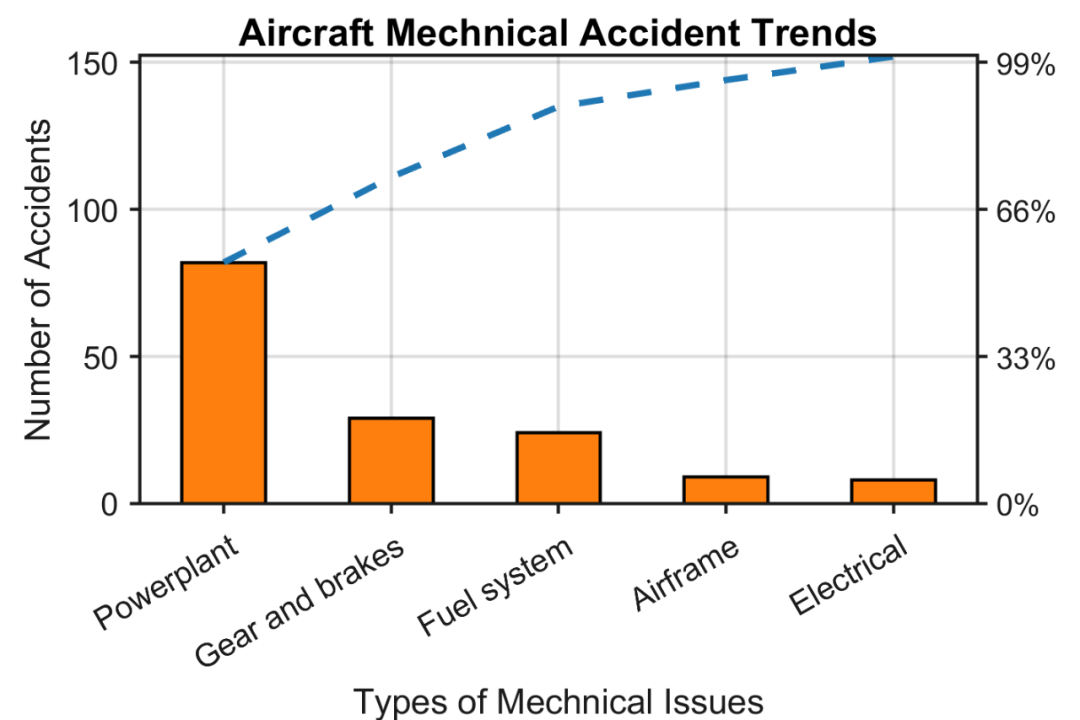

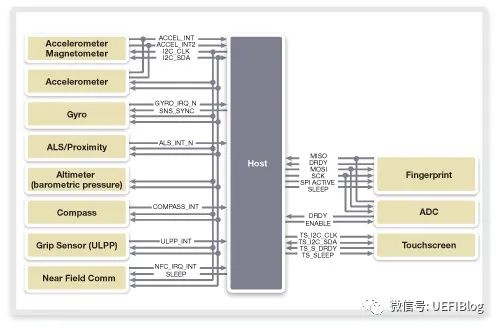

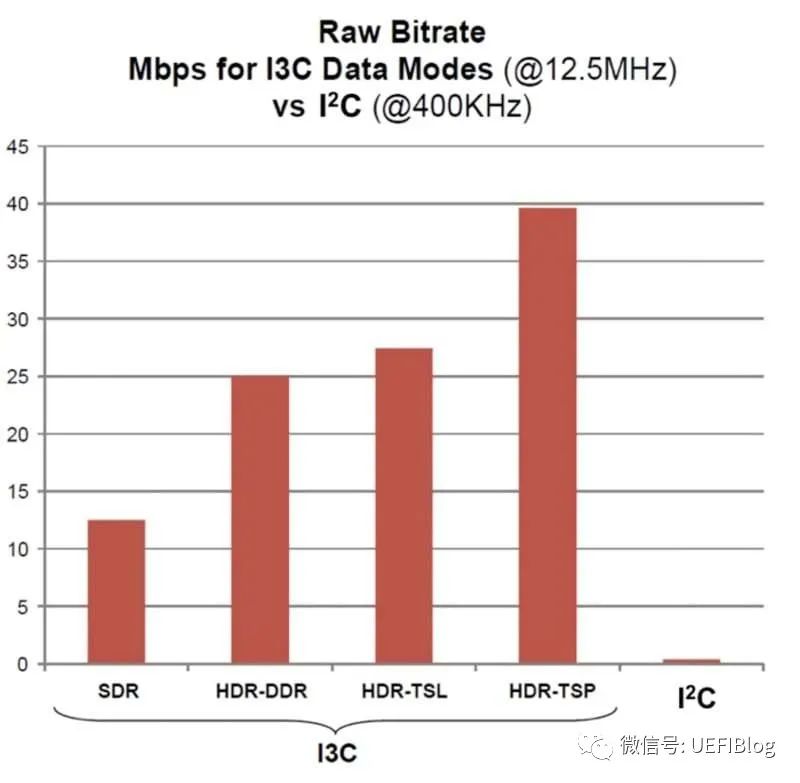

I2C两根线的设计相当简洁而高效,让MCU、PCH或CPU通过两个PIN就可以通讯,节约了成本和简化了设计。但是,所有的通讯都是由Master发起,Slave只是被动相应,这造成很大的麻烦。如果是输出设备还行,但对输入设备,CPU不知道有没有数据,不得不定时Pull I2C总线,看看输入存在与否,这与现代计算机系统设计初衷相反。随着I2C使用越来越广,越来越多的设备加入了更多的带外(sideband)线来补足I2C的缺点,其中最重要的两个线就是中断线INT和一些RESET线,一个经典设计如下:

I2C经典设计

在图中,左边慢速I2C设备虽然共用了一个I2C总线,但每个设备都有自己的INT和Host相连,用于通知Host有事发生,而不是让Host不停来查询,这样才能让Host没事进入省电状态,更加高效。右边的高速设备更是另辟自己的高速I2C总线。如此这般,理想中的简洁设计在现实中越来越被破坏的支离破碎,常常是INT线比I2C线多得多。再加上进一步提高速度的需求,业界呼唤一种新的解决方案。于是I3C应运而生。

I3C来了

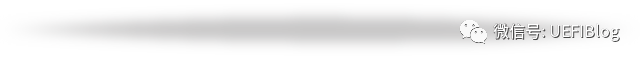

MIPI Alliance发布了I3C标准[1](Basic免费下载)。I3C(Improved Inter Integrated Circuit)另一个名字叫做SenseWire,顾名思义,它的初衷是满足众多物联网设备中的Sensor的,它带来众多的改进,除了常说的12.5MHz速度的提高之外:

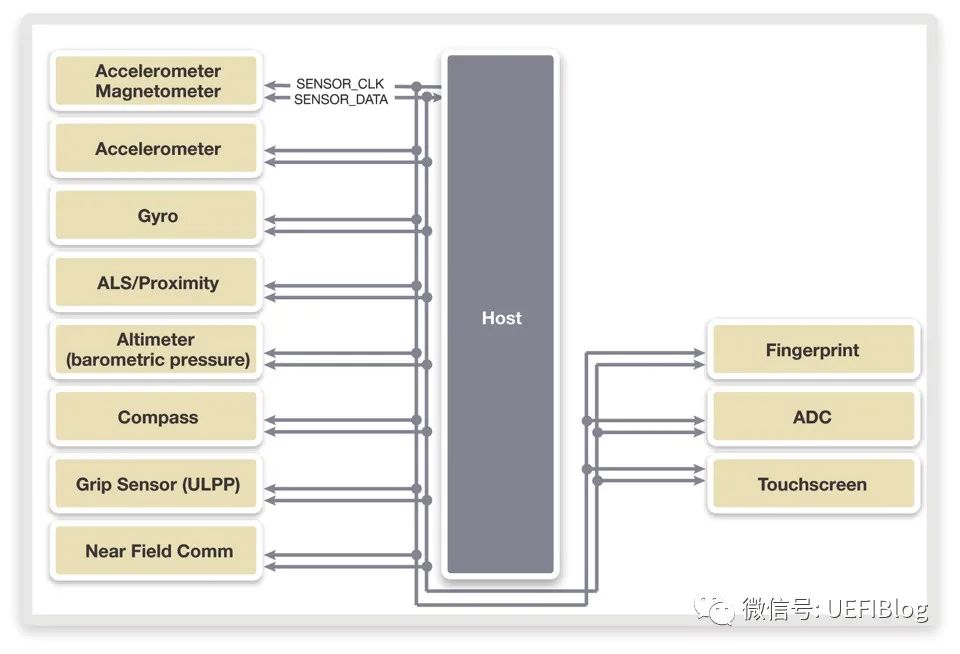

更重要的是嵌入进协议的软中断。如此,就不需要单独的INT连线了:

I3C设计

众多带外连线不见,高速I2C也不需要了,真正实现了高速和简洁。它还向下兼容I2C,以前的设备也还用得上,一个混合系统是这样:

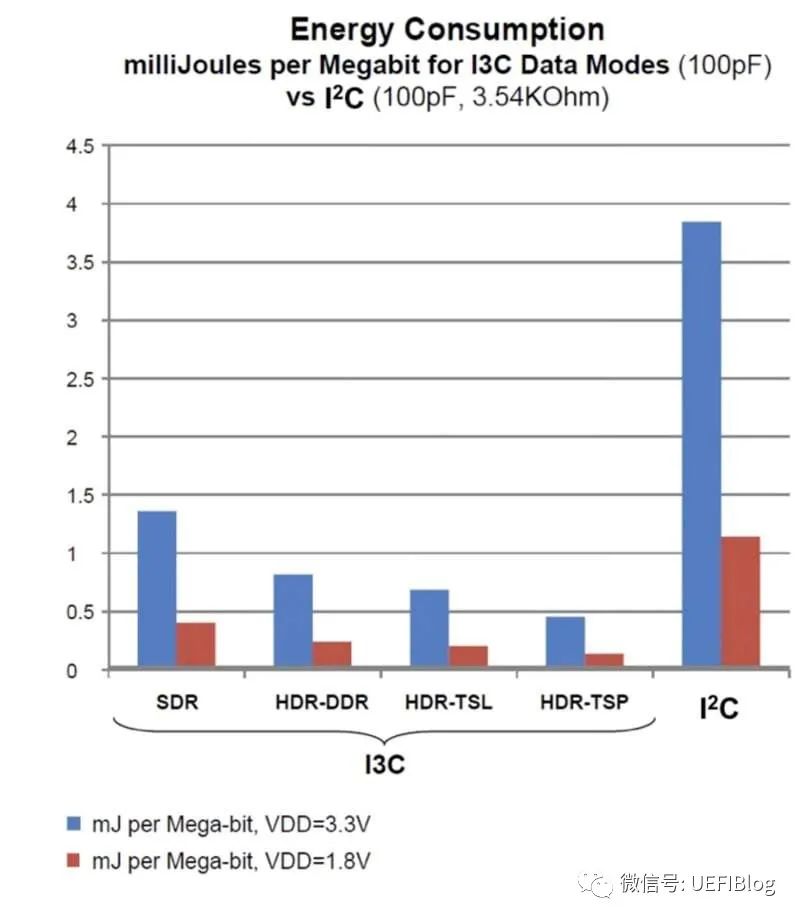

它还节省了电力消耗:

I3C还有其他许多亮度:为了简化设计,提出了I3C Hub;参考内存DDR的概念,提出了DDR加倍数据传输;支持省电模式;In-bound CRC校验;Slave和Slave直接通讯。

结论

曾经有个同学把I2C叫做"I(ai),2(er),C(ci)"而被人狠狠嘲笑了一番,讥笑者一脸傲娇的说“应该叫做I方C!这个“2”是指“平方”!”,更有非要用英文说"I-squared-C"来显示技术niubility和知识渊博的。而实际上,我听美国同事中叫它"I-squared-C"和"I-two-C"差不多一半一半,如此说来中文说法"I(ai),2(er),C(ci)"也并不过分。到了I3C,不知道傲娇的同学如何用中文叫它,难道叫做“I三次方C”?也许可以和英文“I-three-C”一样,叫做“I,3,C”就可以了。