一、状态机原理

(一)有限状态机

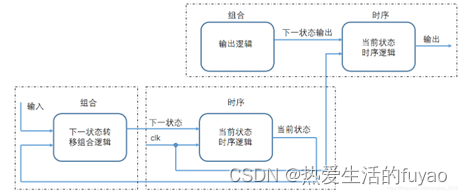

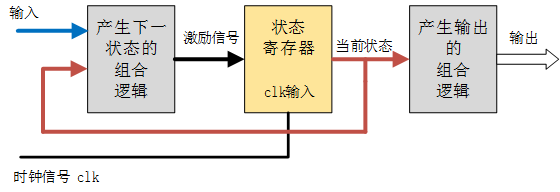

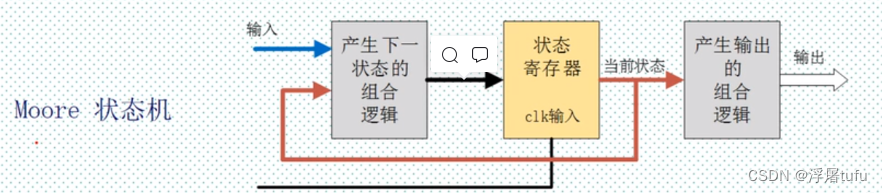

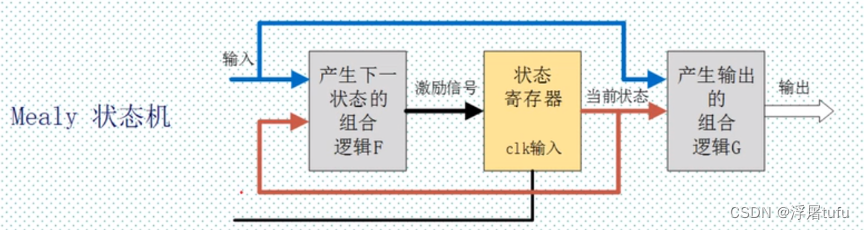

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。有限状态机简写为FSM(Finite State Machine),主要分为2大类:Moore状态机和Mealy状态机

(二)Moore状态机

摩尔状态机:当输出(output)只与当前状态有关时,所描述的状态机称为Moore型状态机。

(三)Mealy状态机

米利状态机:当输出(output)不仅与当前状态有关而且与输入(inputs)有关时,所描述的状态机称为Mealy型状态机。

(四)状态机描述方法

1.一段式

只有一个always块,把所有的逻辑(输入、输出、状态)都在一个always块的时序逻辑中实现。这种写法看起来很简洁,但是不利于维护,如果状态复杂一些容易出错。

2.两段式

有两个always 块,把时序逻辑和组合逻辑分隔开来。时序逻辑里进行当前状态和下一状态的切换,组合逻辑实现各个输入、输出以及状态判断。这种写法不仅便于阅读、理解、维护,而且利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。在两段式描述中,当前状态的输出用组合逻辑实现,可能存在竞争和冒险,产生毛刺。

3.三段式

有三个always块,一个采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件、描述状态转移规律,第三个always使用同步时序的方式描述每个状态的输出。

代码容易维护,时序逻辑的输出解决了两段式组合逻辑的毛刺问题,但是从资源消耗的角度上看,三段式的资源消耗多一些。

(五)状态机标准评判标准

好的状态机的标准很多,最重要的几个方面如下:

第一,状态机要安全,是指FSM不会进入死循环,特别是不会进入非预知的状态,而且由于某些扰动进入非设计状态,也能很快的恢复到正常的状态循环中来。这里面有两层含义:其一要求该FSM的综合实现结果无毛刺等异常扰动;其二要求FSM要完备,即使受到异常扰动进入非设计状态,也能很快恢复到正常状态。

第二,状态机的设计要满足设计的面积和速度的要求。

第三,状态机的设计要清晰易懂、易维护。

二、状态机状态设计

(一)实验要求

根据以下描述功能用verilog编写一段代码,并用状态机来实现该功能。

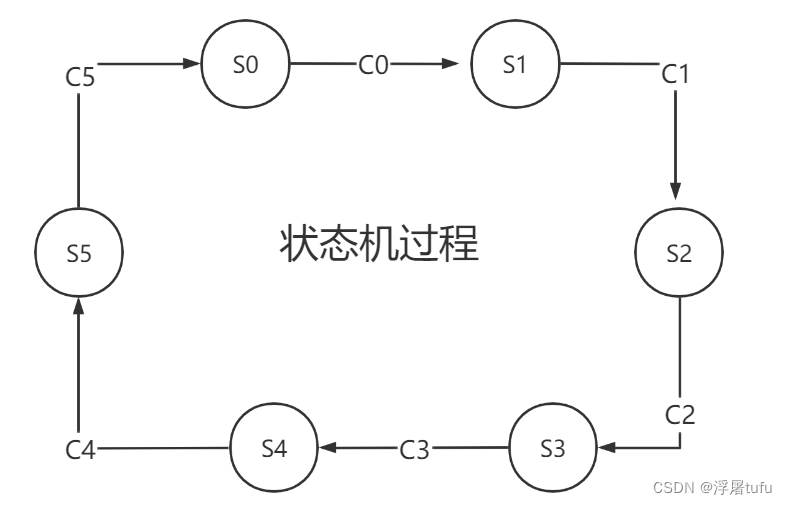

(1)状态机:实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程;

(2)描述状态跳转时间;

(3)编码实现。

(二)设计思路

(三)相关代码

module test(input wire clk,input wire rst_n,output wire [3:0] led

);

parameter MAX_NUM = 26'd49_999_999;//记最大数,时间1s

parameter C0 = 5'd5;//5s

parameter C1 = 5'd20;//20s

parameter C2 = 5'd18;//18s

parameter C3 = 5'd25;//25s

parameter C4 = 5'd14;//14s

parameter C5 = 5'd8;//8s//状态空间

parameter S0 = 3'd0;//初始状态

parameter S1 = 3'd1;//准备状态

parameter S2 = 3'd2;//启动状态

parameter S3 = 3'd3;//停止状态

parameter S4 = 3'd4;//查询状态

parameter S5 = 3'd5;//结果状态reg [4:0] number;//每个模块计数

reg [25:0] cnt;//计数寄存器

reg [4:0] state_time;//每个状态记录时

reg [2:0] flag;//状态标志reg [2:0] cstate;//现态

reg [3:0] led_r;

//1秒钟计数器

always@(posedge clk or negedge rst_n)beginif(!rst_n) begin //按下复位键cnt<=26'd0; //计数器清零endelse if(cnt == MAX_NUM)begincnt <= 26'd0;endelse begincnt <= cnt + 1'd1;end

end//各模块计数器

always@(posedge clk or negedge rst_n)beginif(!rst_n) begin //按下复位键state_time <= 1'd0;endelse if(cnt == MAX_NUM)beginstate_time <= state_time + 1'd1;endelse if(state_time == number)beginstate_time <= 1'd0;endelse beginstate_time <= state_time;end

end//状态切换

always@(posedge clk or negedge rst_n)beginif(!rst_n)begincstate <= S0;number <= C0;flag <= 1'd0;end else begincase(cstate)S0:beginif(state_time == 3'd5&&(!flag))begincstate <= S1;number <= C1;flag <= flag + 1'd1;endelse begincstate <= S0;endendS1:beginif(state_time == 5'd20&&(flag == 1))begincstate <= S2;number <= C2;flag <= flag + 1'd1;endelse begincstate <= S1;endendS2:beginif(state_time == 5'd18&&(flag == 2))begincstate <=S3;number <= C3;flag <= flag + 1'd1;endelse begincstate <= S2;endendS3:beginif(state_time == 5'd25&&(flag == 3))begincstate <=S4;number <= C4;flag <= flag + 1'd1;endelse begincstate <= S3;endendS4:beginif(state_time == 5'd14&&(flag == 4))begincstate <=S5;number <= C5;flag <= flag + 1'd1;endelse begincstate <= S4;endendS5:beginif(state_time == 5'd8 &&(flag == 5))begincstate <=S0;number <= C0;flag <= 1'd0;endelse begincstate <= S5;endenddefault:begin cstate <=S0;number <= C0;flag <= 1'd0;endendcaseend

end

//led灯状态

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginled_r <= 4'b0000;endelse begincase(cstate)S0: led_r <= 4'b0001;S1: led_r <= 4'b0011;S2: led_r <= 4'b0111;S3: led_r <= 4'b1111;S4: beginif(cnt == MAX_NUM)beginled_r <= ~led_r;endelse beginled_r <= led_r ;endendS5: led_r <=4'b0000;default:led_r <= 4'b0000;endcaseend

end

assign led = led_r;

endmodule

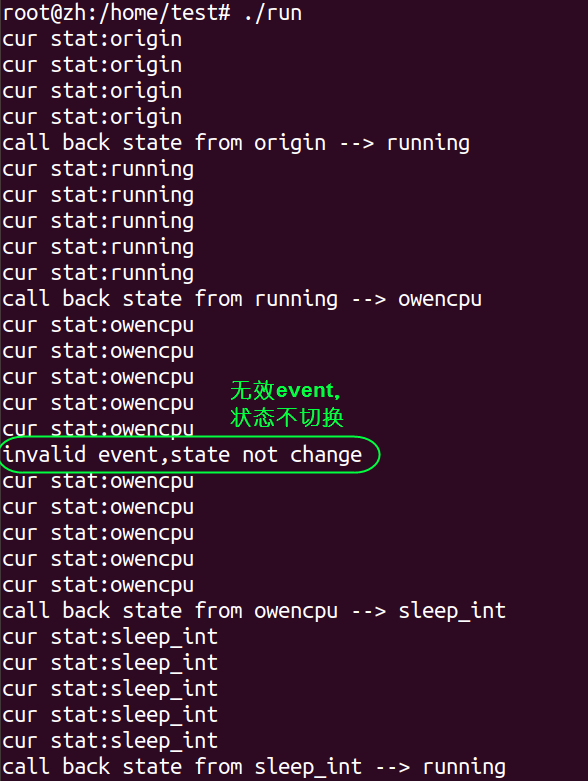

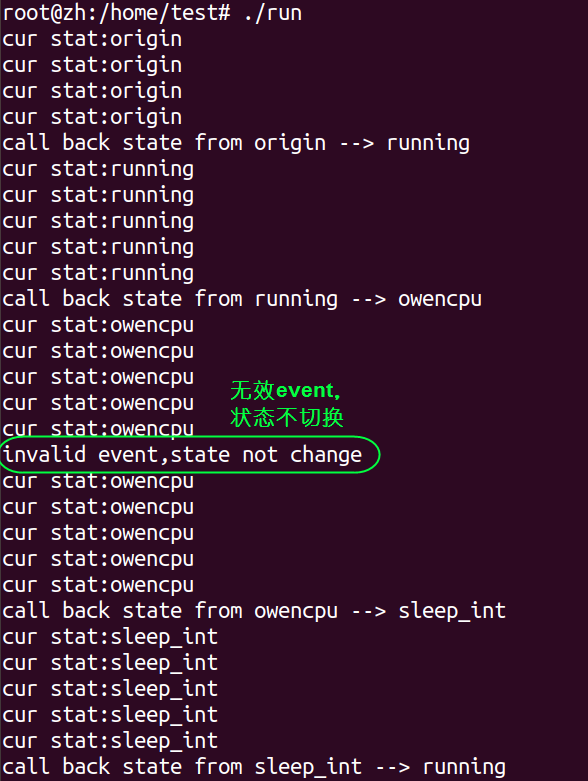

三、检测10010串的状态

(一)实验要求

画出可以检测10010串的状态图, 并用verilog编程实现之。

(二)设计思路

(三)相关代码

(1)状态处理模块 deal.v

//状态识别:10010

module deal(input wire clk, input wire rst_n,input wire [1:0] key,output wire [3:0] led

);

parameter MAX_NUM =26'd49_999_999;

parameter CNT_02 =24'd9_999_999;

//状态空间

parameter S0 = 3'd0;

parameter S1 = 3'd1;

parameter S2 = 3'd2;

parameter S3 = 3'd3;

parameter S4 = 3'd4;

parameter S5 = 3'd5;

reg [2:0] cstate;

reg [25:0] cnt_1s;

reg [23:0] cnt_200ms;

reg [3:0] led_r;//计数器1s

always@(posedge clk or negedge rst_n)beginif(!rst_n)begincnt_1s <= 26'd0;endelse if(cnt_1s == MAX_NUM)begincnt_1s <= 26'd0;endelse begincnt_1s <= cnt_1s + 1'd1;end

end//计数器0.2s

always@(posedge clk or negedge rst_n)beginif(!rst_n)begincnt_200ms <= 24'd0;endelse if(cnt_200ms == CNT_02)begincnt_200ms <= 24'd0;endelse begincnt_200ms <= cnt_200ms + 1'd1;end

end//密码切换

always@(posedge clk or negedge rst_n)beginif(!rst_n)begincstate <= S0;end else begincase(cstate)S0:beginif(key[1])begincstate <=S1;endelse if (key[0])begincstate <= S0;endelse begincstate <= S0;endendS1:beginif(key[0])begincstate <=S2;endelse if (key[1])begincstate <= S0;endelse begincstate <= S1;endendS2:beginif(key[0])begincstate <=S3;endelse if (key[1])begincstate <= S1;endelse begincstate <= S2;endendS3:beginif(key[1])begincstate <=S4;endelse if (key[0])begincstate <= S2;endelse begincstate <= S3;endendS4:beginif(key[0])begincstate <=S5;endelse if (key[1])begincstate <= S3;endelse begincstate <= S4;endendS5:beginif(cnt_1s == MAX_NUM)begincstate <= S0;endelse begincstate <= S5;endenddefault:cstate <= S0;endcaseend

endalways@(posedge clk or negedge rst_n)beginif(!rst_n)beginled_r <= 4'b0000;endelse begincase(cstate)S0: led_r <= 4'b0000;S1: led_r <= 4'b0001;S2: led_r <= 4'b0011;S3: led_r <= 4'b0111;S4: led_r <= 4'b1111;S5: beginif(cnt_200ms == CNT_02)beginled_r <= ~led_r;endelse beginled_r <= led_r ;endenddefault:led_r <= 4'b0000;endcaseend

end

assign led = led_r;

endmodule

(2)按键消抖模块key_debouce.v

module key_debouce(input wire clk,//1s震荡50_000_000次input wire rst_n,input wire key,//当前的按键取值output wire flag,//幻断抖动是否消除的标志信号,0为抖动,1为抖动结束output wire key_value//肖抖后稳定的按键值,给到蜂鸣器模块);parameter MAX_NUM =20'd1_000_000;//定义20ms延迟计数器,0.02s秒,1_000_000c次

reg [19:0] cnt_delay;

//寄存一次key的值,用来判断按键是否消抖成功

reg key_reg;

reg flag_r;

reg key_value_r;

//20ms延时计数器

always@(posedge clk or negedge rst_n)beginif(!rst_n) begin //按下复位键key_reg <= 1'b1; //key变为高电平cnt_delay <= 20'd0; //计数器清零endelse beginkey_reg <= key;if(key_reg == 1'b1 && key == 1'b0 )begin//当这一次的key值和上一次的key值不相等时,证明按键状态在抖动cnt_delay <= MAX_NUM;//延迟计数器设置为20msendelse if(cnt_delay <= 20'd0)begincnt_delay<= 20'd0; endelse begincnt_delay <= cnt_delay - 1'd1;//抖动结束开始递减end end

endalways@(posedge clk or negedge rst_n)

beginif(!rst_n)begin flag_r <= 1'b0; //按键初始值为低电平endelse if(cnt_delay == 20'd1) begin//初始赋值为0,,避免为0,倒计时20到1是20个数,倒计时结束flag_r <= 1'b1;endelse beginflag_r <= 1'b0;end

end always@(posedge clk or negedge rst_n)

beginif(!rst_n)begin key_value_r <= 1'b1; //按键初始值为低电平endelse if(cnt_delay == 20'd1) begin//初始赋值为0,,避免为0,倒计时20到1是20个数,倒计时结束key_value_r <= ~key;endelse beginkey_value_r <= key_value;end

end

assign flag = flag_r;

assign key_value = key_value_r;

endmodule

(3)顶层模块check.v

module check(input wire clk,//1s震荡50_000_000次input wire rst_n,input wire [1:0] key,//当前的按键取值output wire [3:0] led//肖抖后稳定的按键值,给到蜂鸣器模块);

wire [1:0] key_value;

wire [1:0] flag;

key_debouce inst_key_debouce(

.clk (clk),//1s震荡50_000_000次

.rst_n (rst_n),

.key (key[1]),//当前的按键取值.flag (flag[1]),//幻断抖动是否消除的标志信号,0为抖动,1为抖动结束

.key_value (key_value[1])//肖抖后稳定的按键值,给到蜂鸣器模块);

key_debouce inst_key_debouce1(

.clk (clk),//1s震荡50_000_000次

.rst_n (rst_n),

.key (key[0]),//当前的按键取值.flag (flag[0]),//幻断抖动是否消除的标志信号,0为抖动,1为抖动结束

.key_value (key_value[0])//肖抖后稳定的按键值,给到蜂鸣器模块);deal inst_deal(

.clk (clk),

.rst_n (rst_n),

.key ({(flag[1]&&key_value[1]),(flag[0]&&key_value[0])}),

.led (led)

);

endmodule