CDC

CDC(clock domain crossing)

思维导图:

跨时钟域处理方法总结如下:

1、有关系的时钟之间传单bit数据,理论上只需要源数据保持足够长的时间(clk2的两个周期)即可;

2、无关系的时钟之间传单bit数据,必须要使用同步器;

3、不管有无关系的时钟进行单bit传输,脉冲同步器都可以解决这个问题;

4、多bit传输只能使用握手机制或者异步fifo;跨时钟域传输多bit数据,采用握手协议或者异步FIFO,握手信号的缺点在于传输单次数据的延迟比FIFO要大很多。双口RAM搭配格雷码也可以实现。二深度FIFO也可以,此时就不需要使用二进制码/格雷码转换,因为地址位只有一位。

5、低频采高频,为防止数据不丢失,应当让源数据变慢,多保持一些周期;高频采低频则不需要,但是高频采低频得到的结果可能带有很多冗余。

补充:

多个控制信号合并。在可能的情况下,将多个CDC位合并为1位CDC信号。

多周期路径法。使用同步负载信号安全地传递多个CDC位。

使用格雷码传递多个CDC位,格雷码只能解决地址信号这种规律递增信号的异步传输。对于前后值没有确定关系的并行数据来说,格雷码也无能为力。

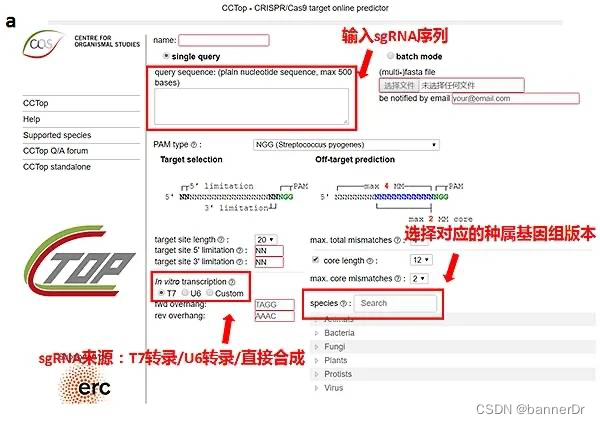

脉冲同步器:

分析:前面其实是一个T触发器,Data为1的时候输出就翻转。当Data是单周期脉冲时,输出变为一次toggle,后面跟两级同步器同步到时钟域2,经过边沿检测得到脉冲。(边沿检测即是一个D触发器延迟加异或)一段时间后,Data产生第二个脉冲,T触发器再次Toggle,后级同步加异或产生单周期脉冲。

适用情况:必须是单周期脉冲的同步,快时钟到慢时钟 和 慢时钟到快时钟 都适用。但要求输入脉冲的间隔(两个脉冲的下降沿间隔)要大于两个clk2周期。

堪称 单比特跨时钟域 脉冲传输 的万能解决方案。

对于单比特的CDC问题,有三种同步器,基本可以满足各种需求。但都有相应的限制。

三种同步器的详细说明:

A. 电平(level signal)同步器

就是一级clk1触发器+两级clk2触发器

要求跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。

在电平同步器中,

跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。

同步之后的信号是电平的形式,

而该电平所维持的时钟周期个数是其在跨时钟域期间被上升沿检测到的次数。

这种同步器是所有同步器电路的核心。

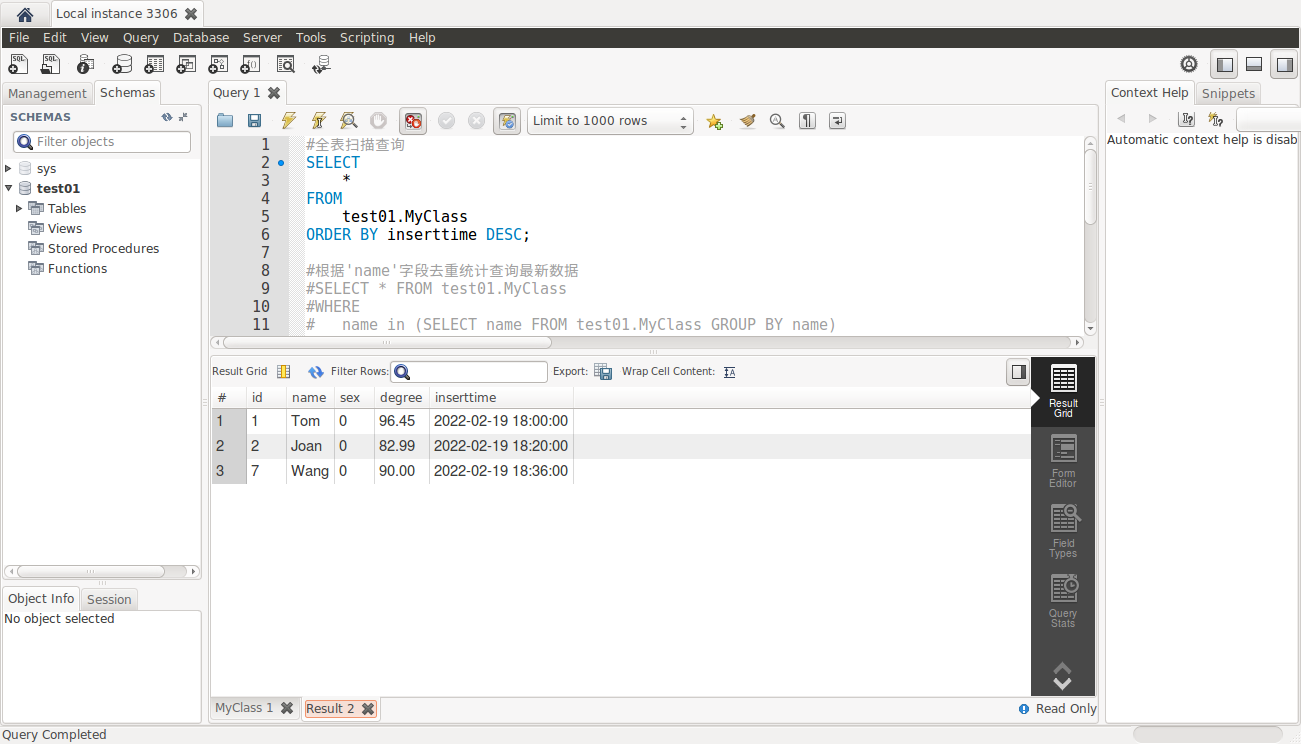

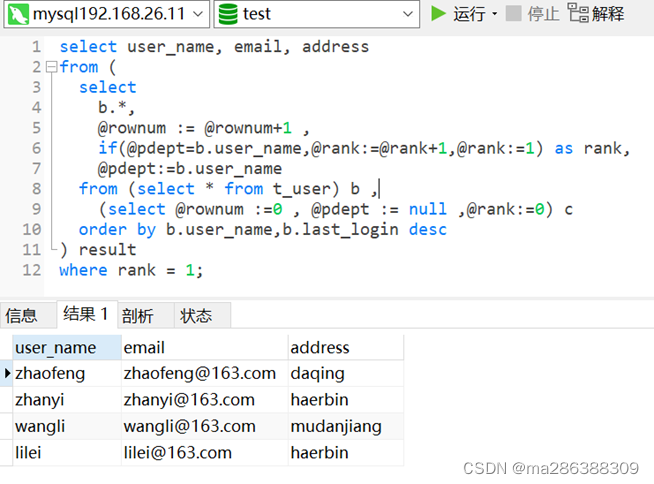

下面是用Verilog描述的电平同步器

module synzer_ls(data_out,clk1,clk2,data_in); //level signal synchronizeroutput data_out; // signal that after synchronizedinput clk1; // old clk signalinput clk2;