相关文章

74HC244;74HCT244——三态八路缓冲器/线路驱动器

1.特点: 2.引脚及封装: 3.引脚定义: 解释: output enable input (active LOW)输出使能,低电平有效 data input:数据输入 bus output:总线输出

4.使用逻辑:

解释: L:…

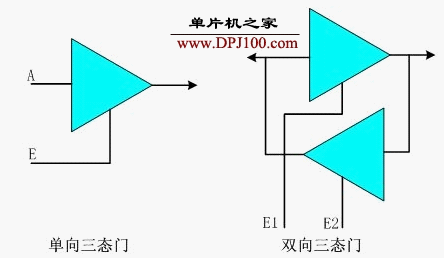

三态门(三态缓冲器)的工作原理

转载于http://www.eeworld.com.cn/mcu/article_2017102035218.html 为减少信息传输线的数目,大多数计算机中的信息传输线均采用总线形式,即凡要传输的同类信息都走同一组传输线,且信息是分时传送的。在计算机中一般有三组总线,即数…

2021-05-18

TTL集成门电路——三态门(与非门) 1、三态门的三种输出状态:高电平(逻辑1),低电平(逻辑0),高阻态(电阻大,可以视为开路) 2、三态门真值表及逻辑符号: !3、三态门的工作电路: 4、三态门的工作原理: EN为三…

锁存器、触发器、寄存器和缓冲器的区别

目录

一、锁存器

二、触发器

三、寄存器

四、移位寄存器

五、总线收发器/缓冲器

六、锁存器与触发器的区别

七、D触发器和D锁存器的区别

八、寄存器与锁存器的区别 一、锁存器

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用…

【微机原理与接口技术】简单易学的 简单接口芯片—— 三态门 74LS244和 锁存器 74LS273

作者:MiTu_-_ 本帖内容著作权归作者所有,转载请务必保留本文链接 接口电路的基本构成

CPU通过接口与外部设备的连接示意图如下: 负责把信息从外部设备传入 CPU 的接口(端口)叫做输入接口(端口)…

三态门——概念,作用,原理

介绍一下三态门的概念、作用、原理 目录

三态门的概念

三态门的作用

实现总线结构

实现双向数据传输

三态门的原理 三态门的概念

三态门是指逻辑门的输出有三种状态:高电平状态、低电平状态、高阻状态。

其中,高阻状态相当于隔离状态(…

数字IC设计中的三态门原理

数字电路中的三态门 可参考另外一篇博客数字电路基础知识——CMOS门电路 (与非门、或非、非门、OD门、传输门、三态门)

三态门除了高低电平,还有第三个状态——高阻态。 三态门(Three-state gate)是一种重要的总线接口电路。也常常出现在芯片…

计算机电源缓冲器,集成电路中缓冲器的作用

描述 缓冲器的概念 缓冲器在不同的领域有不同的含义。 在计算机领域,缓冲器指的是缓冲寄存器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设…

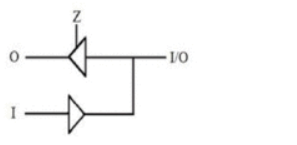

单片机I/O口管脚内部结构(锁存器,输出驱动器,三态缓冲器,多路开关)

学习ARM嵌入式的时候,发现自己对以前学过的数模器件的知识遗忘了不少,按照我的进度本来应该继续学习ARM微处理器控制的课程,但想着后来势必还会遇到相同的问题所以就准备中断一下,杀回来把汇编和一些电路知识再总结一下࿰…

三态(tri-state)门、双向(bi-directional)端口的建模、仿真和综合

目录

1. 概要

2. 三态门

2.1 概念

2.2 三态门建模

3. 双向端口

3.1 HDL语言描述

3.2 直接调用元件库中的模块

3. 仿真

4. 综合 1. 概要 双向端口顾名思义是一种既可以作为输入端口接收数据,也可以作为输出端口发出数据,它对数据的操作是双向的。比如某个设计需要一个…

FPGA基础知识极简教程(8)详解三态缓冲器

博文目录 写在前面正文 全双工与半双工FPGA和ASIC中的三态缓冲器如何在VHDL和Verilog中推断出三态缓冲区 参考资料交个朋友 写在前面 下面用举例子的方式引出三态门,内容过长,大家可直接跳过,进入正文! 三态门在FPGA以及ASIC设计中…

三态缓冲器的工作原理

转载自---百家号

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1)ÿ…

VSCODE调试时在cygwin.S中发生段错误

起因: C实现矩阵类和向量类 当看了我实现的矩阵类后,一个同学问我: 然后我就试了试1000维,结果运行时在cygwin.S里引发了奇奇怪怪的Segmentation fault,而且这个文件还是一片空白,压根就没有代码 后来一番…

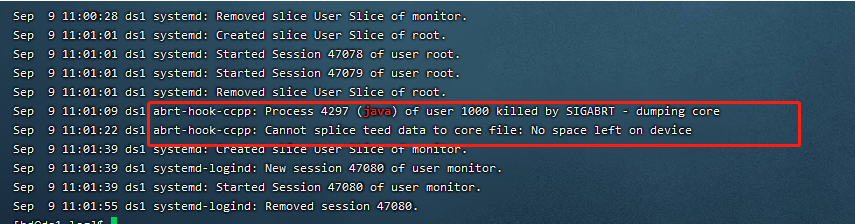

【高并发】高并发环境下如何优化Tomcat性能?看完我懂了!

写在前面 Tomcat作为最常用的Java Web服务器,随着并发量越来越高,Tomcat的性能会急剧下降,那有没有什么方法来优化Tomcat在高并发环境下的性能呢? Tomcat运行模式

Tomcat的运行模式有3种。

1.bio模式

默认的模式,性能非常低下,…

Java-JVM-常用参数和调优方案(超保姆级)

Java-JVM-常用参数和调优方案 必须了解的内容

必须看过Java-JVM基础(调优必须知道)知道JVM大概的情况,这篇文章我博客里有

堆区(Java堆:所有的线程共享该区域) 通过new的方式创建的对象(一个类的实例)、数组所占的空间。 非堆区:…

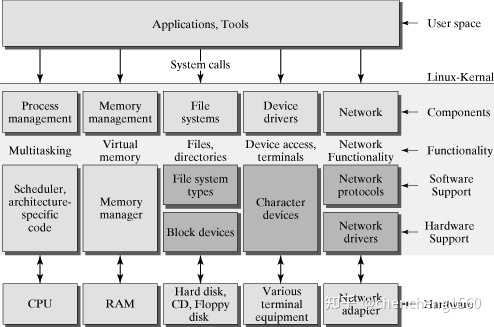

嵌入式知识图谱WiKi(嵌入式开发/研发入门教程和路线图)

嵌入式知识图谱WiKi 作者将狼才鲸创建时间2022-02-18 因图床更新不方便,最新版请跳转到Gitee文档源文件仓库网址 才鲸 / 嵌入式知识图谱WiKi CSDN有图的文档阅读网址 嵌入式知识图谱WiKi Bilibili视频讲解网址(待完成) 才鲸嵌入式主页 一、概…

select、poll和epoll

select、poll和epoll 对select、poll、epoll了解得不多,下面是从《构建高性能Web站点》摘录下来的介绍,等以后真正接触到select、poll和epoll方面的开发再详细写一下使用上的区别。 select select最早于1983年出现在4.2BSD中,它通过一个sele…