作者:MiTu_-_

本帖内容著作权归作者所有,转载请务必保留本文链接

接口电路的基本构成

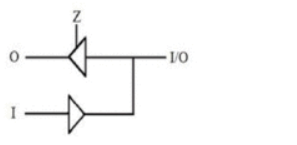

CPU通过接口与外部设备的连接示意图如下:

负责把信息从外部设备传入 CPU 的接口(端口)叫做输入接口(端口),而将信息从 CPU 输出到外部设备的接口(端口)叫做输出接口(端口)。

1)在输入数据时,由于外部设备处理的时间一般比 CPU 要长的多,不可能让 CPU 一直等外设传完数据再工作吧。所以

* 对输入接口的要求是:必须具有对数据的控制能力。不必让外设一直向 CPU 传数据,让外设传入到输入接口,等数据准备好后,CPU开始读取时,才将数据传入 CPU。这样在外设传入数据的时候,CPU 就不用一直等,可以干其他活,等需要时,在发出读信号获取外设的数据。典型的输入接口芯片是三态门芯片 74LS244。

2)在输出数据时,同样外设的速度比较慢,要使正确写入外设,CPU 输出的数据必须要保持一段时间,但这样对 CPU 来说是极大的浪费。所以

* 对输出接口的要求是:必须具有对数据的锁存能力。不必让 CPU 等待向外设传输数据的整个过程,通过向输出接口传输数据,让输出接口来为外设传输数据,就可以节约 CPU 的时间,让 CPU 干其他事情。典型的输出接口芯片是锁存器 74LS273。

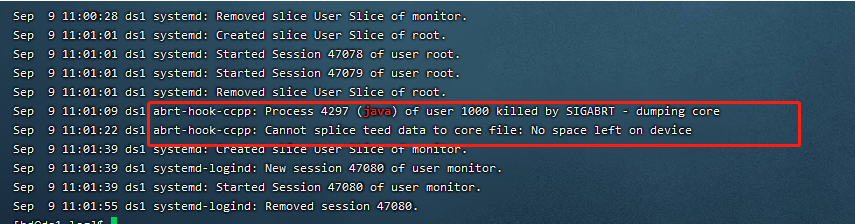

三态门接口

普通三态门如下图所示,A 为输入端,Y 为输出端,C 为控制端。当 C 为低电平,三态门导通,A 和 Y 之间导通;当 C 为高电平,三态门不导通,为高阻状态,A 和 Y 之间不导通。

典型的三态门芯片 74LS244 如图所示。它由8个三态门构成,有两个控制端 E1 和 E2。每个控制端各控制四个三态门。当某一控制端有效(低电平)时,相应的四个三态门导通,否则为高阻状态(断开)。实际应用中,通常将两个三态门并联,这样就可以用一个控制引号来使 8 个三态门同时导通或关断。

Example:

编写程序判断下图中的开关状态。如果所有开关都闭合,则程序转向 NEXT1 的程序段执行,否则转向 NEXT2。

先来分析电路结构:

- 右边是外设、开关Ki 和三态门输入端 Ii 构成的电路。当开关闭合时,三态门输入端被短路,不会导通;当开关断开时,三态门导通。于是就可以从 74LS244 的输出端 D0 ~ D7 传给 CPU 的数据端,从而得知开关的状态。

- 左下角是 CPU 的地址,可以看到地址线 A1 和 A0 未参与译码,所以它占用的地址是 83FCH ~ 83FFH。可以任选一个地址。CPU的地址线和端口读信号端一起经过或门到 74LS244 的使能端。

再来分析整体电路:

- 当 CPU 不发出端口读信号时,IOR非为高电平,使能端 E1非 和 E2非 为高电平,三态门不导通。

- 当 CPU 发出端口读信号时,IOR非为低电平,使能端为低电平,三态门导通,就可以由外设向 CPU 发送数据了。

程序段如下:

mov dx, 83FCH

in al, dx

and al, 0FFH

JZ NEXT1

JMP NEXT2

锁存器接口

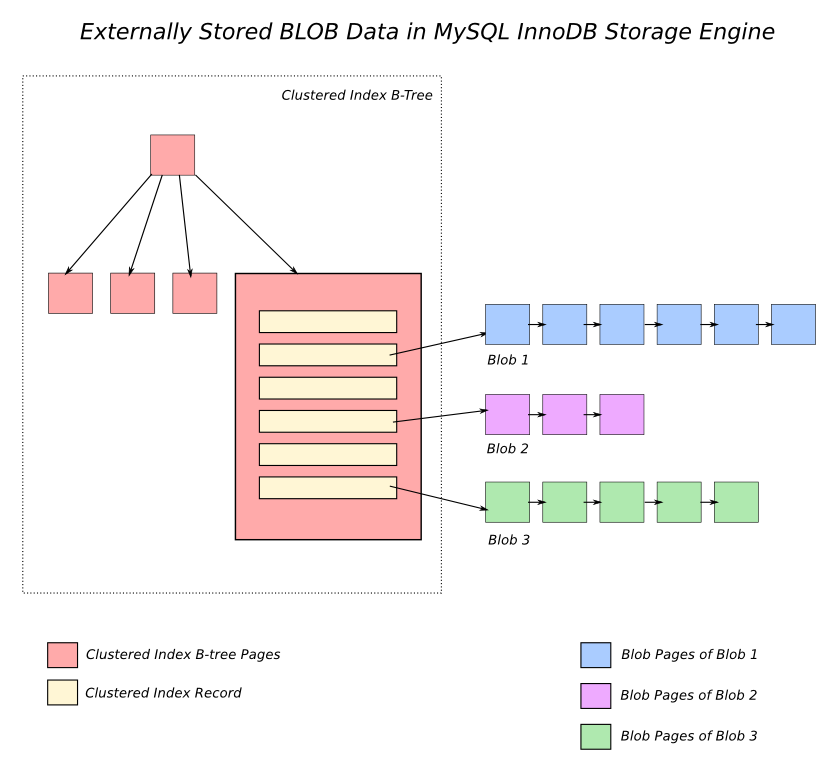

D触发器如下图所示。在每个上升沿,将 D 的状态所存到 Q 里。

常用的锁存器 74LS273 如图所示。它内部包含8个 D 触发器。共有 8 个数据输入端(D0 ~ D7)和8个输出端(Q0 ~ Q7)。S为复位端,低电平有效。CP 为脉冲输入端,在每个脉冲的上升沿将输出端 Di 的锁存到输出端 Qi 里,并将此状态保持到下一个时钟脉冲上升沿的到来。

Example:

8个 Q 端 与 8 个发光二极管相连接,编程使接到 Q0 端和 Q6 端的发光二极管发光。假设该输出接口的地址为 0FFFFH。

先来分析电路结构:

- 右边是外设,当 Q 端为高电平,经过非门,变为低电平,发光二极管才能发光;否则不发光。

- 左上角是 CPU 向 74LS273 发送数据,使指定的灯亮。左下角是 CPU的地址线,如题目所说地址为 0FFFFH。则 A0 ~ A7 与 A8 ~ A15 经过与非门输出的都是低电平。

再来分析整体电路:

- 当 CPU 不发出端口写信号时,IOW非为高电平,则脉冲 CP 为高电平,因为没有上升沿,之前C P 就是高电平,所以 Qi 状态不发生改变。

- 当 CPU 发出端口写信号时,IOW非为低电平,因为 CPU 发出的写脉冲是极窄的负脉冲,当 CP 读到下一次上升沿时,会将 CPU 写入的 数据 D0 ~ D7 存入到锁存器,再经锁存器输出到发光二极管的阴极,就可以使相应的二极管发光。

程序段如下:

mov dx, 0FFFFH

mov al, 01000001b

out dx, al

通过以上的两个例子,可以看出三态门和锁存器所发挥的作用。三态门控制输入端口的信号,锁存器锁存输出端口的信号。这样 CPU 就无需等待缓慢的外设了,而可以把任务交给这些接口芯片,去干其他更值得干的事情。如此便可以大大提高计算机的运转效率。

赠人玫瑰,手有余香!!!还望大家随手点个赞哟(^U^)ノ~YO