FPGA(22)实验综合17 OV7725

- OV7725简介

- SCCB协议

- VGA显示

- 模块配置

- PLL时钟模块

- I2C驱动模块

- I2C配置模块

- 摄像头模块

- SDRAM读/写控制模块

- VGA驱动模块

- OV5640简介

OV7725简介

OmniVision 公司生产的CMOS图像传感器,感光阵列达到640X480,能实现最快60fps VGA分辨率的图像采集。传感器内部包括自动曝光控制(AEC)、自动增益控制(ACG)、自动白平衡(AWB)等图像处理功能。

XCLK提供时钟到时序发生器,控制模拟信号处理器对模拟数据进行算法处理。处理成G(绿色)和R/B(红色/蓝色)两路通道经过A/D转换器后成数字信号。然后再通过DSP进行相关的图像处理,最终输出所配置格式的10位视频数据流。这些都可以通过寄存器进行配置,配置寄存器的接口就是SCCB接口,该接口协议兼容i2c协议。

SCCB协议

现在的都是用两线式串行总线,控制数据格式、分辨率、图像处理参数等。包括SIO-C串行时钟输入线和SIO_D串行双向数据线所以说兼容I2C。

主机不需要管应答位,因为OV7725会发出应答信号来响应主机是否传输完成。

SCCB读传输协议分为两部分

第一部分:通过虚写操作使地址指针指向虚写操作中的寄存器地址的位置

第二部分:读器件地址和读操作

SCCB不支持连续读写,所以NA位必须为高电平。

VGA显示

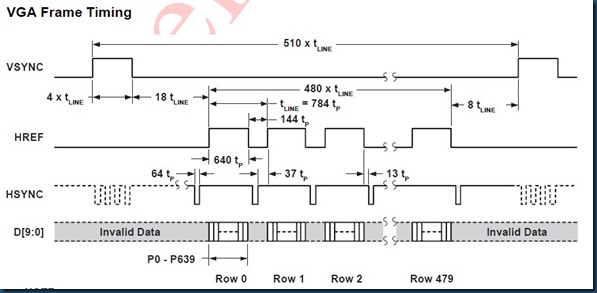

VSYNC:场同步信号,由摄像头输出,用于标志一帧数据的开始与结束。图中VSYNC的高电平作为一帧的同步信号,在低电平时输出的数据有效。注意场同步信号是可以通过设置寄存器0x15 Bit[1]位进行取反,即低电平同步高电平有效

HREF/HSYNC:行同步信号,由摄像头输出,用于标志一行数据的开始与结束。HREF和HSYNC由同一引脚输出,只是数据同步方式不一样。HREF为高电平时,图像输出有效,可以通过寄存器0x15 Bit[1]配置。

D[9:0]:数据信号,由摄像头输出,在RGB格式输出中,只有高8位D[9:0]是有效的。

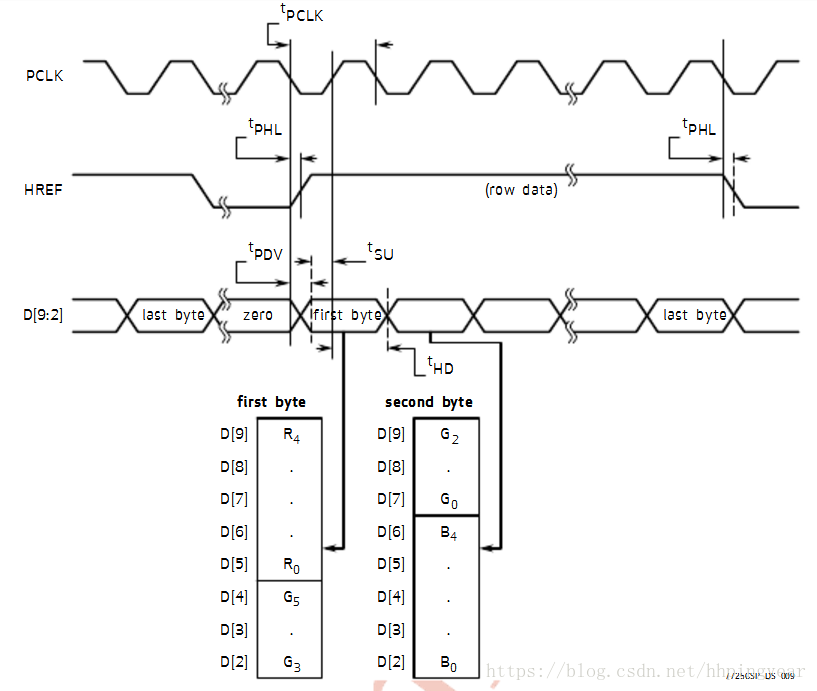

tPCLK:一个像素时钟周期

tP:一个数据周期,在RGB模式中表示两个像素周期,这是因为RGB565采用16bit表示一个像素点,而OV7725在一个像素周期只能传输8个bit。

tLINE:摄像头输出一行数据的时间,共768个tP,包含640tP个高电平和144tP个低电平。640tP是有效数据的输出时间。

YSYNC的上升沿作为一帧的开始,高电平同步脉冲的时间4 X tLINK,紧接着等待18 X tLINK时间后,HREF开始拉高,此时输出有效数据;输出480行数据之后等待8 X tLINE一帧数据传输结束。所以输出一帧图像的时间为510 X tLINE

然后假设PCLK为25MHz则一帧图像的输出时间为510 X tLINE = 510 X 784 tP = 510 X 784 - 2tPCLK=31.9872ms

摄像头输出帧率为1000ms/31.9872ms=31Hz

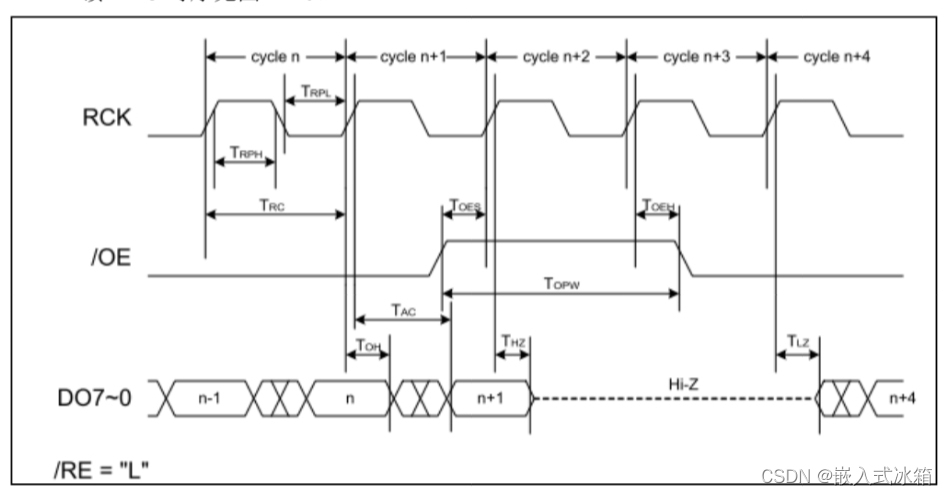

PCLK为OV7725输出的像素时钟,HREF为行同步信号,D[9:2]为8位像素。OV7725最大可以输出10位数据,在RGB565输出模式中,只有高8位是有效的。像素数据为高电平时有效,第一次输出数据为RGB565数据的高8位,第二次为低8位,数据是在像素时钟的下降沿改变,为了在数据最稳定时采集图像数据,所以需要在像素时钟上升沿采集数据。

模块配置

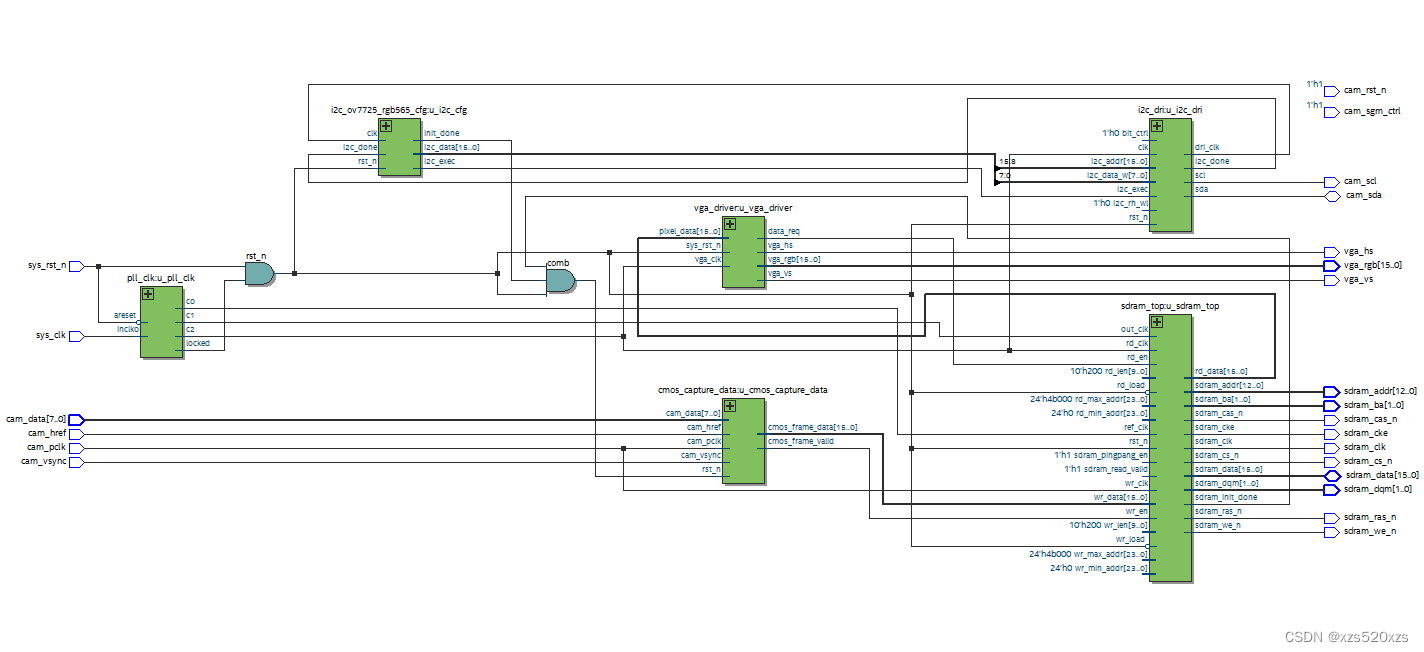

PLL时钟模块

共输出三个时钟,SDRAM读/写控制模块的驱动时钟需要两个100MHz。I2C驱动模块和VGA驱动模块的驱动时钟需要25MHz。

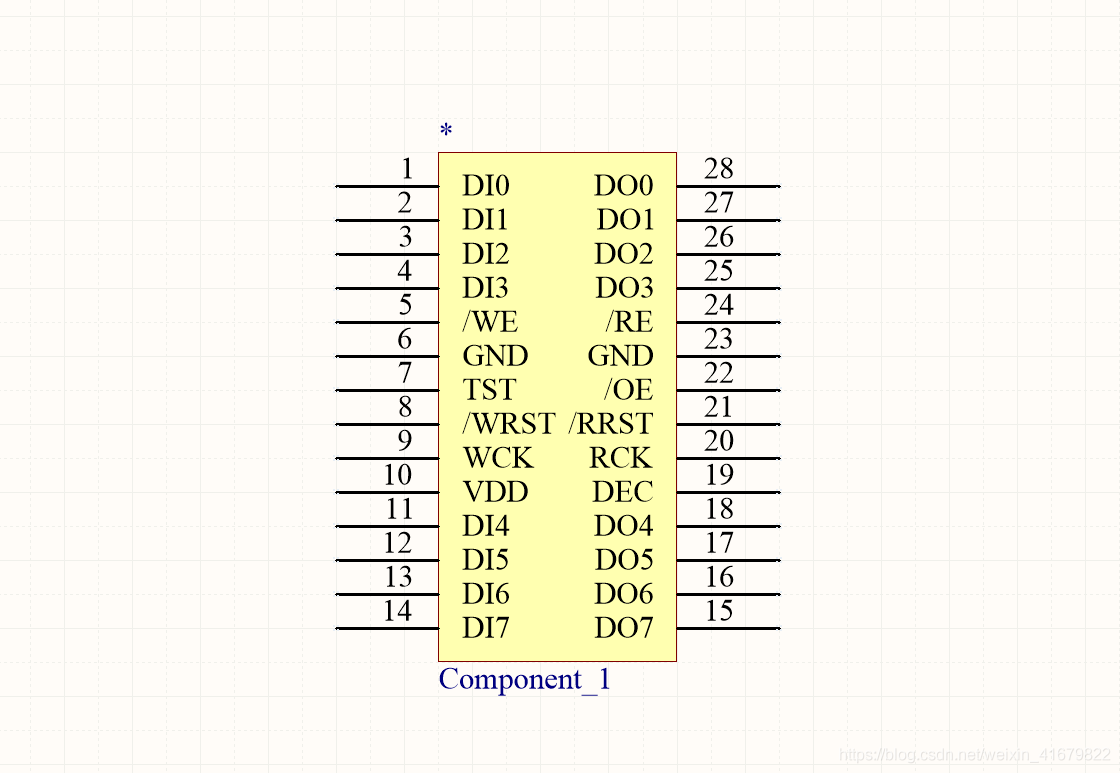

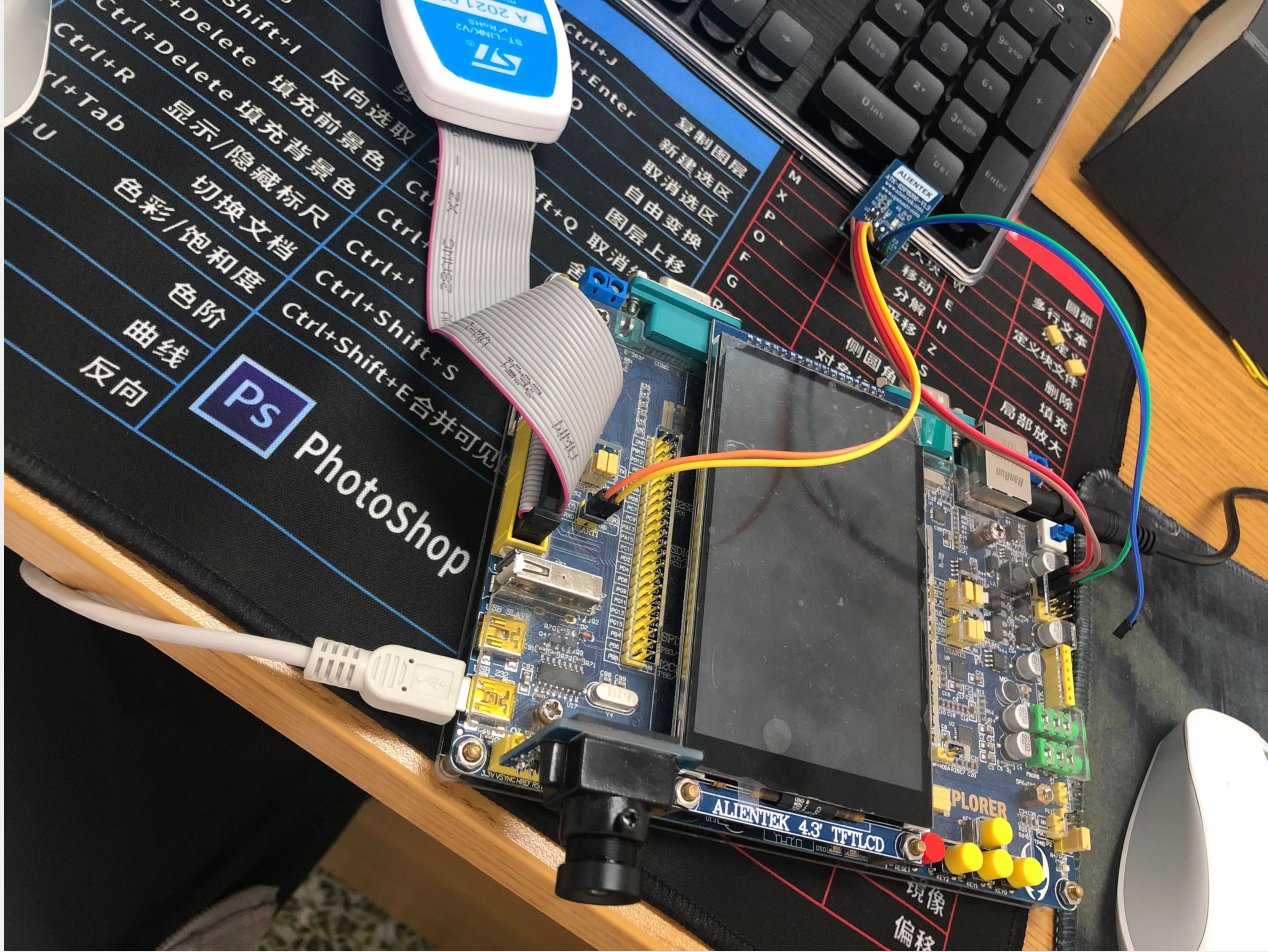

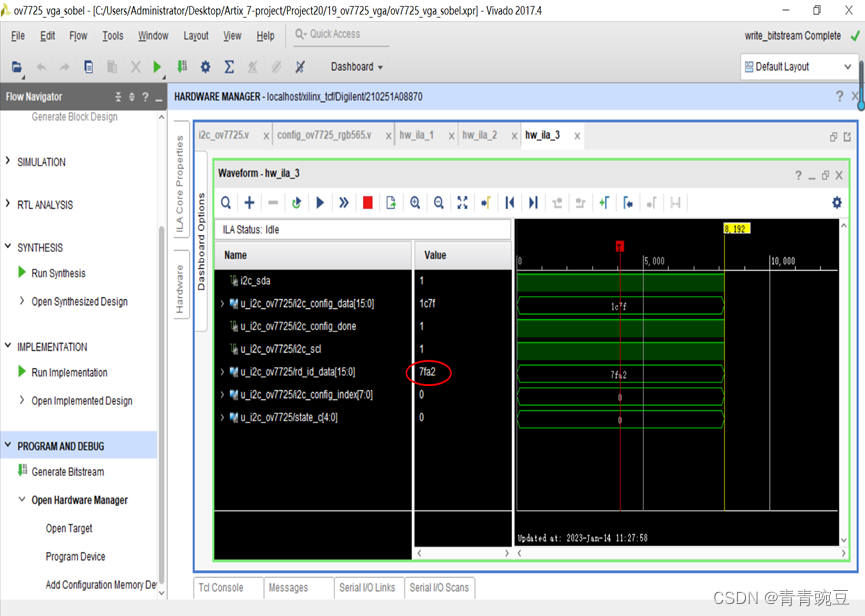

I2C驱动模块

负责驱动OV7725的SCCB接口总线

I2C配置模块

时钟由I2C驱动模块提供。该模块寄存需要配置的寄存器地址、数据以及控制初始化的开始与结束,同时该模块输出OV7725的寄存器地址和数据以及控制I2C驱动模块开始执行的控制信号,直接连接到I2C驱动模块的用户接口

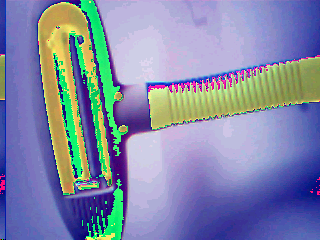

摄像头模块

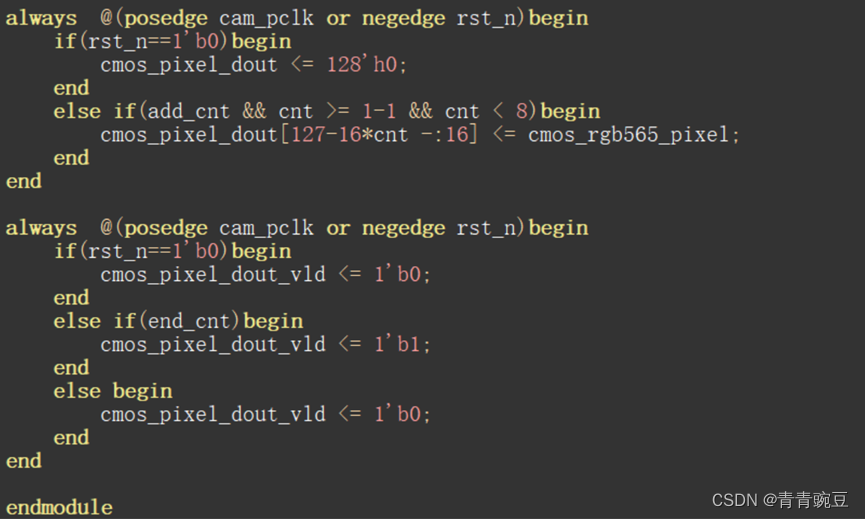

摄像头采集模块在像素时钟驱动下将传感器输出的场同步信号、行同步信号以及8位数据转换成SDRAM读/写控制模块的写使能信号和16位写数据信号,完成对OV7725的图像采集

SDRAM读/写控制模块

负责驱动SDRAM片外存储器,缓存图像传感器输出的图像数据。

VGA驱动模块

负责驱动VGA显示器,通过读取SDRAM读/写控制模块来输出像素数据

代码中 为了解决两帧图像错乱的情况,使能SDRAM的乒乓操作内部使用两个存储器分别缓存两帧图像。图像数据在两个存储器之间来回切换

OV5640简介

OmniVision 公司生产的图像传感器。支持500W像素、采集速率,具有高图像处理性能