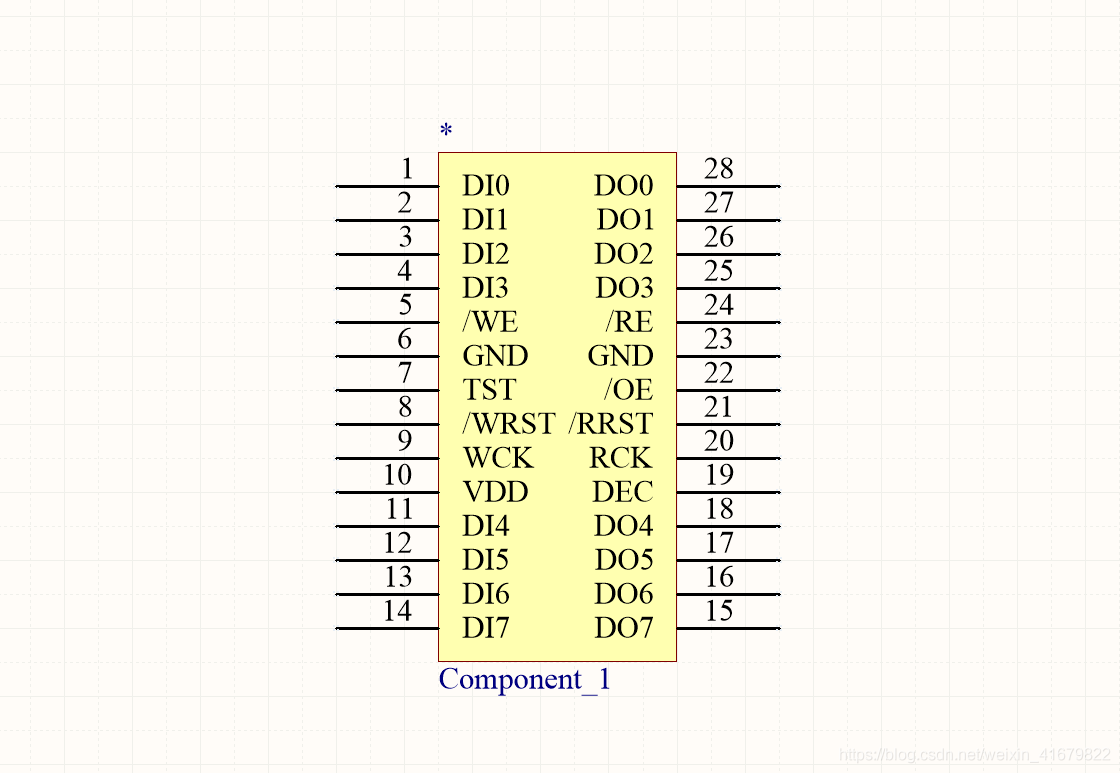

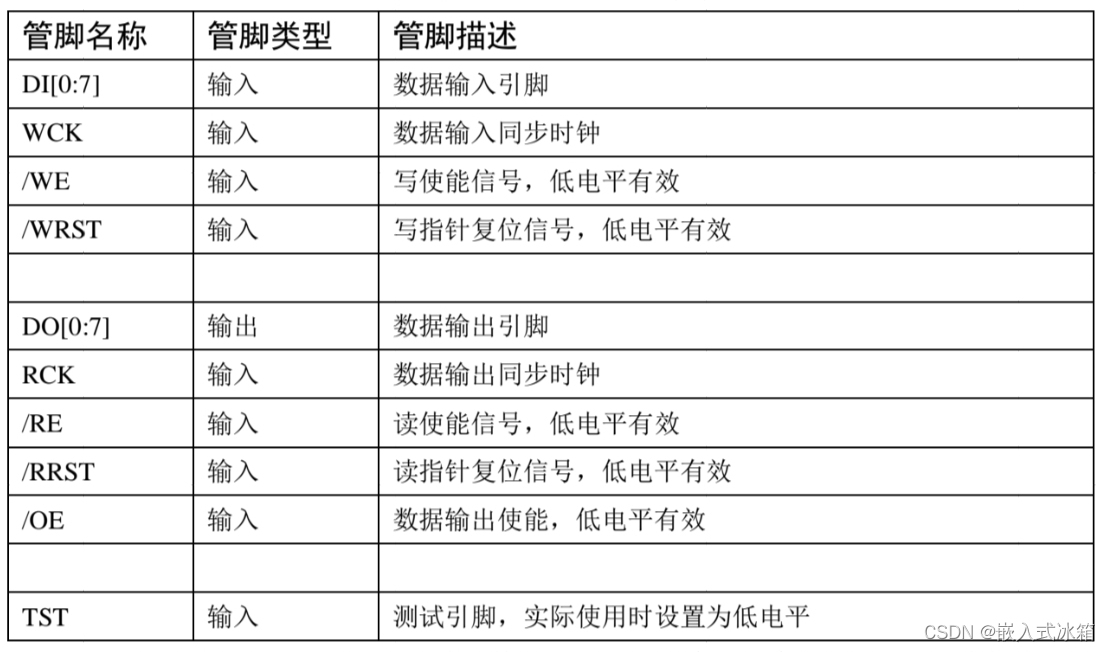

一、引脚定义

摄像头引出的接口包含了OV7725传感器及FIFO的混合引脚,外部的控制器使用这些引脚即可驱动摄像头

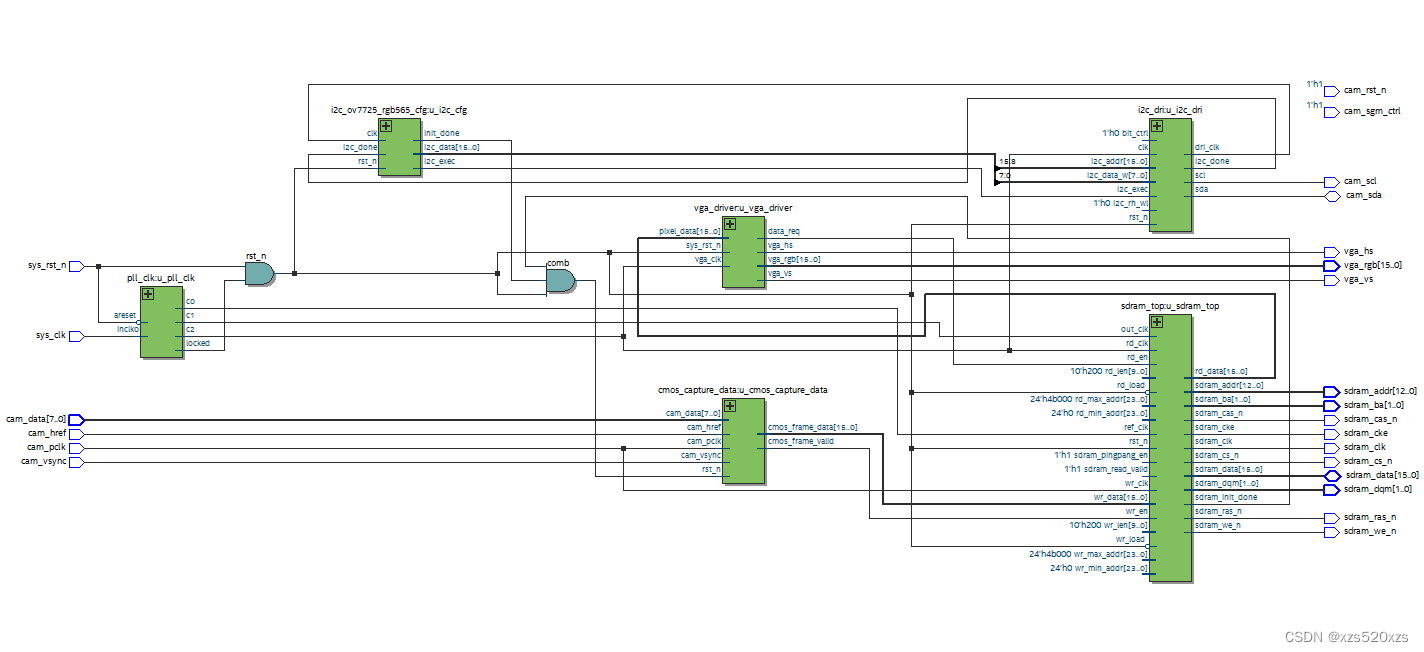

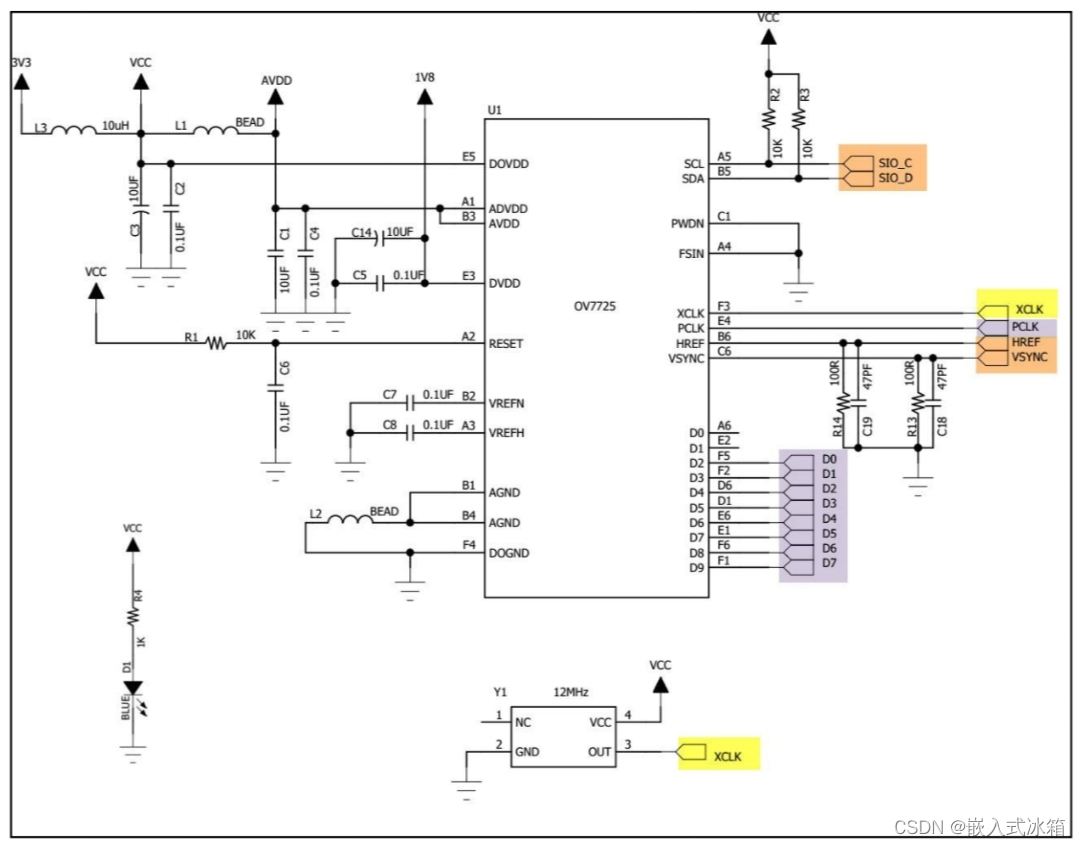

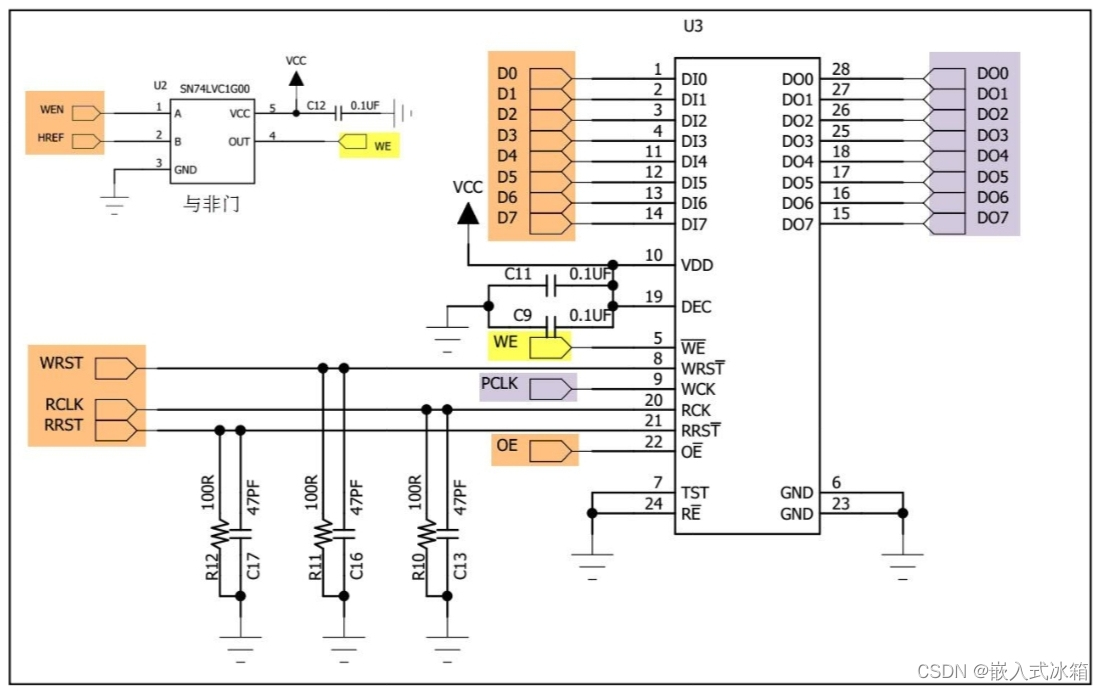

二、原理图

V7725传感器像素输出相关的PCLK和D[0:7]并没有引出,因为这些引脚被连接到了FIFO的输入部分,OV7725的像素输出时序与FIFO的写入数据时序是一致的,所以在OV7725时钟PCLK的驱动下,它输出的数据会一个字节一个字节地被FIFO接收并存储起来。

其中最为特殊的是WEN引脚,它与OV7725的HREF连接到一个与非门的输入,与非门的输出连接到FIFO的WE引脚,因此,当WEN与HREF均为高电平时,FIFO的WE为低电平,此时允许OV7725向FIFO写入数据。外部控制器通过控制WEN引脚,可防止OV7725覆盖了还未被控制器读出的旧FIFO数据。另外,在OV7725输出时序中,只有当HREF为高电平时,PCLK驱动下D[0:7]线表示的才是有效像素数据,因此,利用HREF控制FIFO的WE可以确保只有有效数据才被写入到FIFO中。

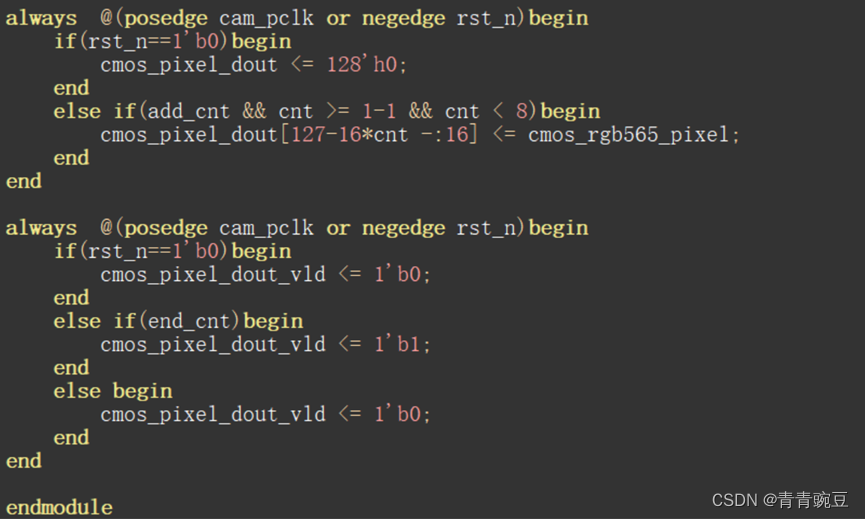

三、像素数据输出时序(SCCB协议)

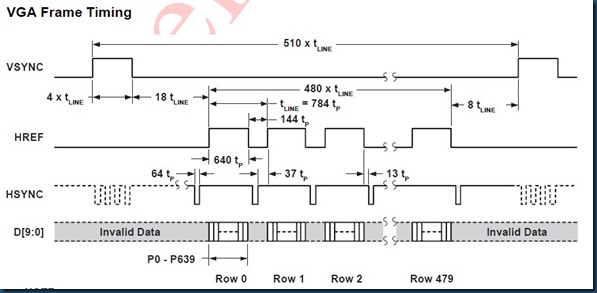

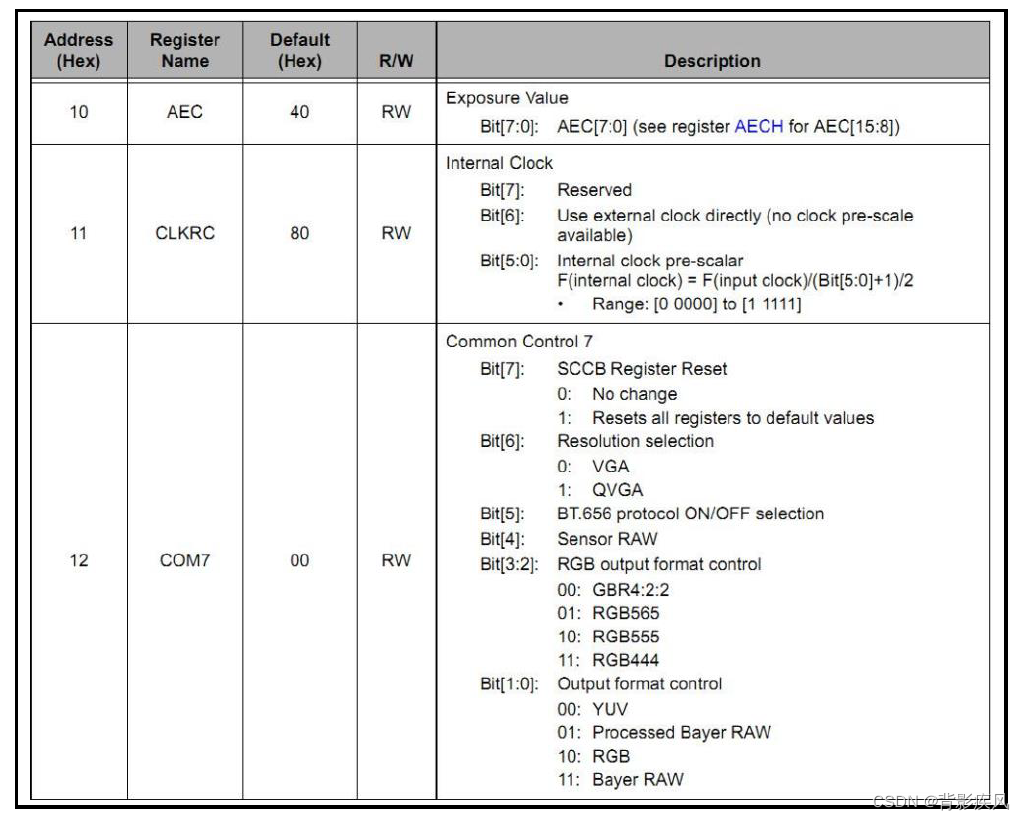

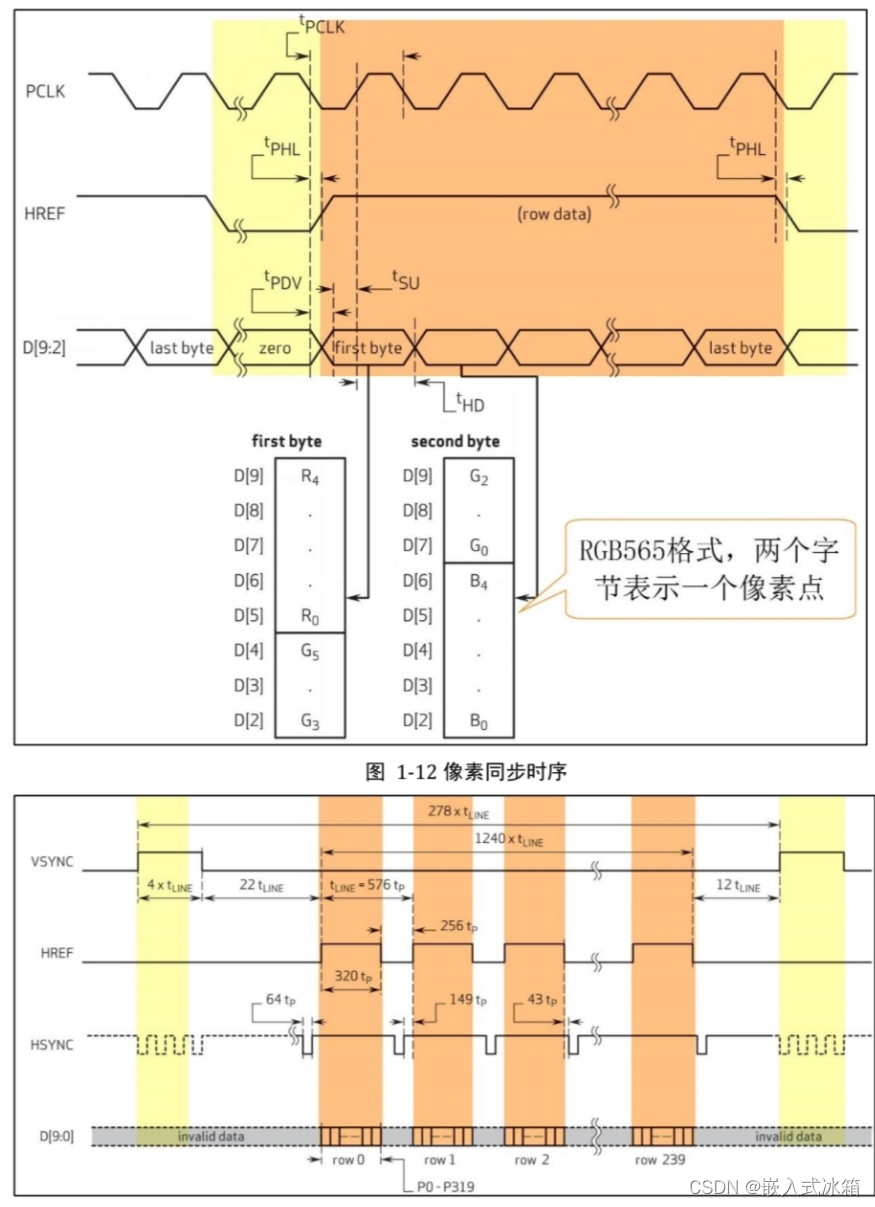

主控器控制OV7725时采用SCCB协议读写其寄存器,而它输出图像时则使用VGA或QVGA时序,其中VGA在输出图像分辨率为480*640时采用,QVGA是Quarter VGA,其输出分辨率为240*320,这些时序跟控制液晶屏输出图像数据时十分类似。OV7725传感器输出图像时,一帧帧地输出,在帧内的数据一般从左到右,从上到下,一个像素一个像素地输出(也可通过寄存器修改方向),见图。

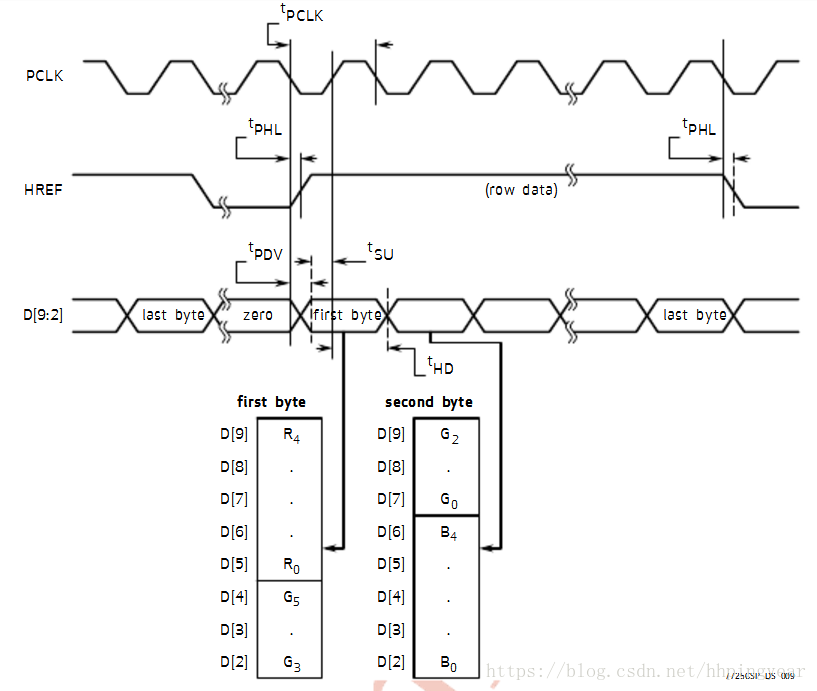

例如,若我们使用D2-D9数据线,图像格式设置为RGB565,进行数据输出时,D2-D9数据线在PCLK在上升沿阶段维持稳定,并且会在1个像素同步时钟PCLK的驱动下发送1字节的数据信号,所以2个PCLK时钟可发送1个RGB565格式的像素数据。当HREF为高电平时,像素数据依次传输,每传输完一行数据时,行同步信号HREF会输出一个电平跳变信号间隔开当前行和下一行的数据;一帧的图像由N行数据组成,当VSYNC为低电平时,各行的像素数据依次传输,每传输完一帧图像时,VSYNC会输出一个电平跳变信号。

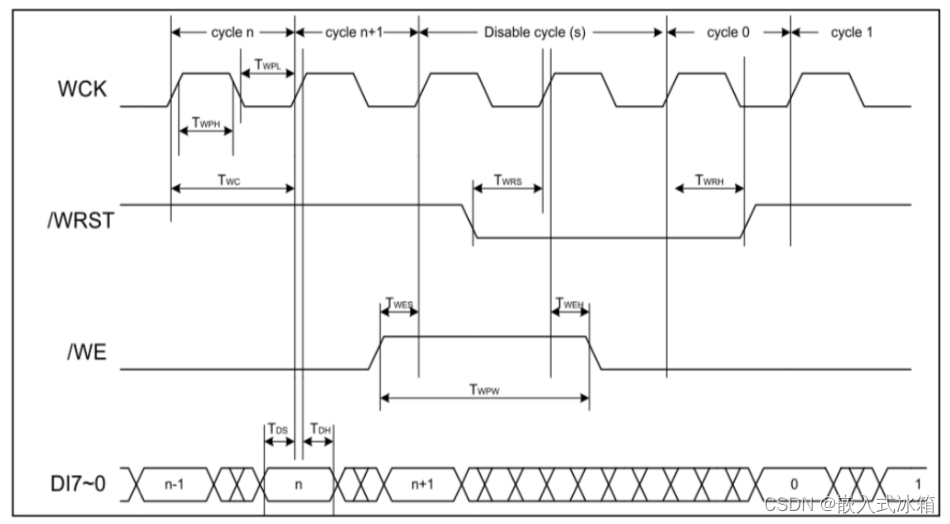

四、FIFO读写时序

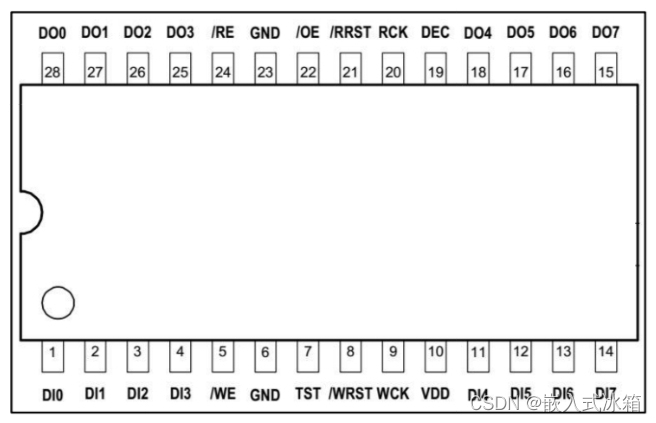

OV7725摄像头在图像传感器之外还添加了一个型号为AL422B的FIFO,用于缓冲数据。AL422B的本质是一种RAM存储器,它的容量大小为393216字节,支持同时写入和读出数据。

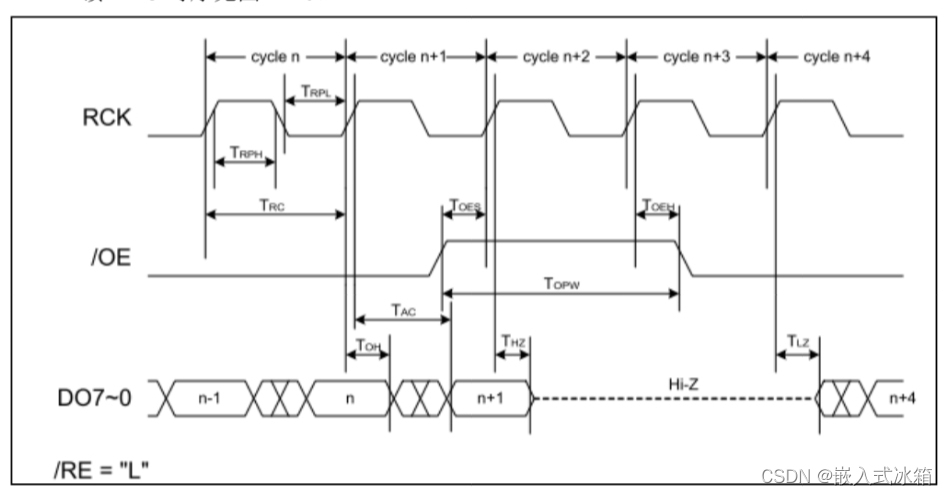

2.读时序

2.读时序