《计算机组成原理》

课程设计报告

微指令模型机实现

班级:

姓名:

学号:

小组成员:

完成日期:2020.10.16

一、计算机的功能和用途

通过该课程设计的学习,我们设计一台模型机,该模型机运行在FPGA平台上,可以模拟真正的计算机设备的一部分功能,通过微指令进行实现,使其可以完成一些基本操作,包括:加法、自增、减法、判断全0和判断进位,还有包括存储器读取写入等操作。具体实现了(1)(A1)+(A2)->A3。将A1、A2地址的数分别存到R0、R1寄存器,再通过ALU将加法结果存到寄存器R0,同时将结果状态cvnz存入寄存器STATE,将状态存入内存,再将寄存器R0的值存入内存。(2)数组累加。取出数组首地址放入地址累加器D,取出数组的数进行累加,使内存中的累加次数X+1,使D中地址+1,接着判断累加次数X是否等于N,若X与N不相等,则跳转到累加指令,否则结束循环,将累加结果存入内存。调试过程中通过平台指示灯观察内部的数据流动情况,了解计算机的运行、计算过程和内部的时序问题并辅助修改。

二、指令系统

1.指令格式

1.1基本字长:8位

1.2单字长指令:指令由高4位操作码、低4位全0构成。

7 4 3 2 1 0

| 操作码OP | 0 | 0 | 0 | 0

|

1.3双字长指令:指令由第一字节高4位操作码、低4位全0;第二字节操作数或操作数地址构成。

7 4 3 2 1 0

| 操作码OP | 0 | 0 | 0 | 0

|

|

操作数/操作数地址

| ||||

两种指令格式的高四位为操作码,支持16种不同的指令。使用10、20...90作为九条指令以及F0停机指令。

2.寻址方式:

2.1:立即数寻址:操作数在指令的第二个字节

2.2:直接寻址:操作数的地址在指令的第二个字节。

3.指令功能

| 指令 | 指令功能 |

| LDR0 A | 读内存将A地址的数存入寄存器R0 |

| LDR1 A | 读内存将A地址的数存入寄存器R1 |

| LDD A | 读内存将A地址的数存入地址累加器D |

| ADD1 S | 将寄存器R0、R1中的数相加,结果存入R0,加法结果状态从寄存器STATE写入内存地址S |

| ADD2 | 读内存将地址累加器D中地址的数与寄存器R0中的数相加,结果存入R0 |

| STA A | 将寄存器R0中的数写入内存地址A |

| INX #X | 将内存中的累加次数X取出、+1再写回内存 |

| CPX #N | 累加次数X与N比较,若相等则跳出循环,否则继续循环累加 |

| BNE #M | 跳转回加法指令 |

| HALT | 停机 |

三、总体结构与数据通路

3.1总体结构

总体结构的设计参考课件中的设计方案。下面简要介绍一下各个部分:

1.寄存器

根据功能的需要,共设计了8个8位寄存器,其中R0、R1为通用寄存器。PC为程序计数器,存储下一条将要执行的指令的地址。IR为指令寄存器,用来存储从RAM中取出的指令。MAR为地址寄存器,该寄存器提供对RAM进行读写的地址。MBR为三态门寄存器,隔离RAM读写冲突,数据通过MBR写入RAM。状态寄存器为三态门寄存器,保存ALU的计算结果状态,并可以直接写入RAM。地址累加器寄存器,提供自增的RAM数组地址。

2.ALU

ALU为组合74181和74182的算术运算器,接收从A和B两个端口传来的数据进行相应的运算并输出,可以提供的加法、直传、减法、判断全0、判断进位的操作。

3.选择器

因为我们的算术运算器的数据来源有很多,所以需要设计数据选择器。

- 连接算术运算器的两个选择器,左边的是数据选择器A,选择RAM或R0的数据。右边的是数据选择器B,选择R1或PC的数据。

- 连接uPC的选择器,选择无条件跳转或按操作码散转。

- 连接MAR的选择器,选择总线或地址累加器的数据。

3.2数据通路

模型机的数据通路是以总线为基础

下面就几个基本的操作分析其数据通路:

1)取指令

RAM → 选择器A →ALU → Bus → IR

2)送指令地址

PC → 选择器B →ALU → Bus → 选择器C → MAR

3)程序计数器加一

(PC)+1 → PC

4)(R0)->RAM

R0 → 选择器A →ALU → Bus → MBR → RAM

5)(R0)+(R1)->RAM

R0 → 选择器A →ALU ,R1 → 选择器B →ALU,

ALU→ Bus → MBR → RAM

四、指令执行流程

五、微程序执行流程

1.取指周期

| 00 | M(MAR)->IR |

| 01 | (PC)+1->PC |

| 02 | QJP |

2.LDR0 A1

| 10 | (PC)->MAR |

| 11 | (PC)+1->PC |

| 12 | M(MAR)->MAR |

| 13 | M(MAR)->R0 |

| 14 | (PC)->MAR |

| 15 | JP |

3.LDR1 A2

| 20 | (PC)->MAR |

| 21 | (PC)+1->PC |

| 22 | M(MAR)->MAR |

| 23 | M(MAR)->R1 |

| 24 | (PC)->MAR |

| 25 | JP |

4.ADD1 S

| 30 | (R0)+(R1)->R0 |

| 31 | (PC)->MAR |

| 32 | M(MAR)->MAR |

| 33 | 状态->M(MAR) |

| 34 | (PC)+1->PC |

| 35 | (PC)->MAR |

| 36 | JP |

5.STA

| 40 | (PC)->MAR |

| 41 | (PC)+1->PC |

| 42 | M(MAR)->MAR |

| 43 | ****R0->M(MAR) |

| 44 | (PC)->MAR |

| 45 | JP |

6.LDD D

| 50 | (PC)->MAR |

| 51 | M(MAR)->D |

| 52 | (PC)+1->PC |

| 53 | (PC)->MAR |

| 54 | JP |

7.INX #X

| 60 | (PC)->MAR |

| 61 | M(MAR)->R1 |

| 62 | (R1)+1->R1 |

| 63 | R1->M(MAR) |

| 64 | (PC)+1->PC |

| 65 | (PC)->MAR |

| 66 | JP |

8.CPX #N

| 70 | PC ->MAR |

| 71 | N==X? M(MAR)-(R1) |

| 72 | 特殊(PC)+1->PC |

| 73 | 特殊(PC)+1->PC |

| 74 | (PC)+1->PC |

| 75 | (PC)->MAR |

| 76 | JP |

9.BNE #M

| 80 | (PC)->MAR |

| 81 | (PC) + M(MAR)->PC |

| 82 | (PC)->MAR |

| 83 | JP |

10.ADD2

| 90 | (D)->MAR |

| 91 | (D)+1->D |

| 92 | M(MAR)->R1 |

| 93 | (R0)+(R1)->R0 |

| 94 | (PC)->MAR |

| 95 | JP |

六、微程序设计

- 微操作字段定义

23-20:

20控制AB累加

0:不选中累加

1:选中累加

21:是否特殊PC+1

22:en_MBR:1为写

19-16:S3210

15:PC_LD

计数1

置数0

14-12:

ALU_AB选择

R0:001

R1:010

PC:011

RAM:100

R0R1:101

RAPC:110

RAR1:111

11-9:寄存器

R0:001

R1:010

PC:011

IR:100

MAR:101

MBR:110

地址累加器D:111

8:停机

7:ALU_CN

6:en

状态寄存器:1为写

5:RAM读

4:RAM写

3:地址累加器D_LD

2-0:跳转

upc+1:001

JP:010

QJP:011

2.特殊规定

1.ALU直传状态寄存器不计状态

2.s3210、cn:00001表示直传

3.只能通过R0存回RAM

4.直传B(PC)用加法

S1001 CN1

状态寄存器控制:1.脉冲2.A的AY、BY有选中即A中有传数3.s3210非全零,即非A直传。实现了A+B和A-B时存状态

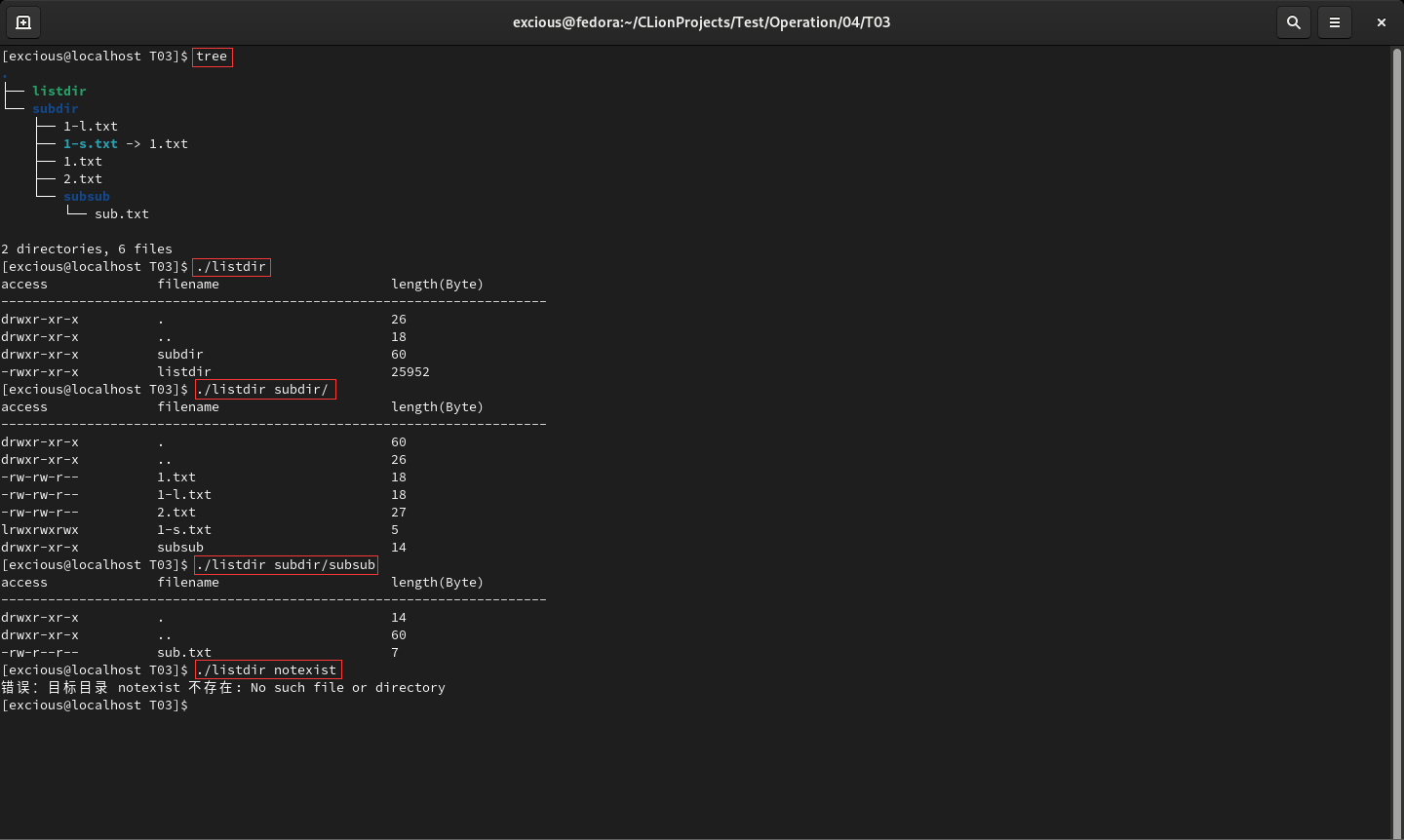

七、系统的调试、测试方法:

7.1单元测试部分

ALU测试:

a输入、b输入、s0-s3、cn接开关

输出、进位接指示灯

通过控制开关查看指示灯的方式验证ALU加法、减法、直传、进位功能

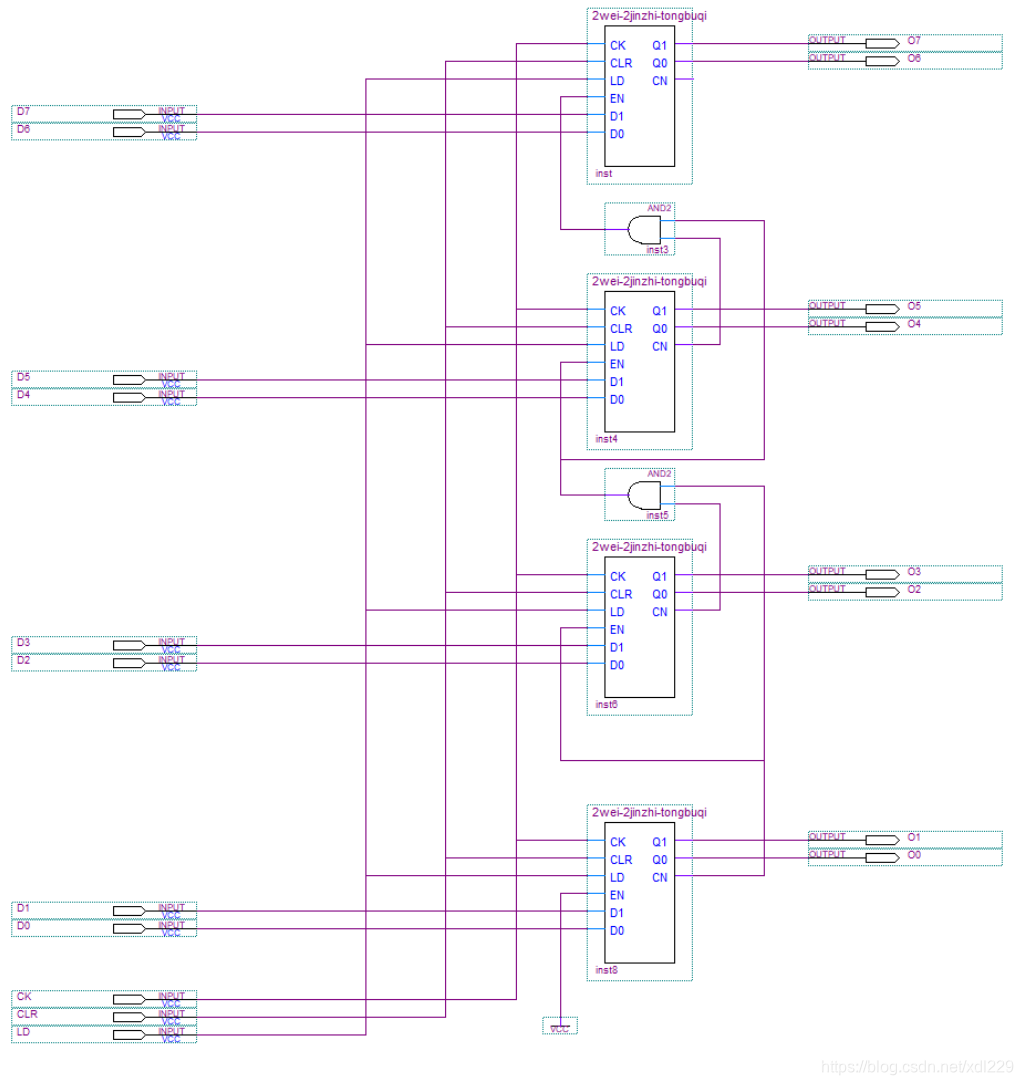

累加器测试(PC、地址累加器、uPC):

输入、LD、CLR接开关,CP接单脉冲

输出接指示灯

通过控制开关和单脉冲查看指示灯的方式验证累加器置数、计数功能

7.2整机测试部分:

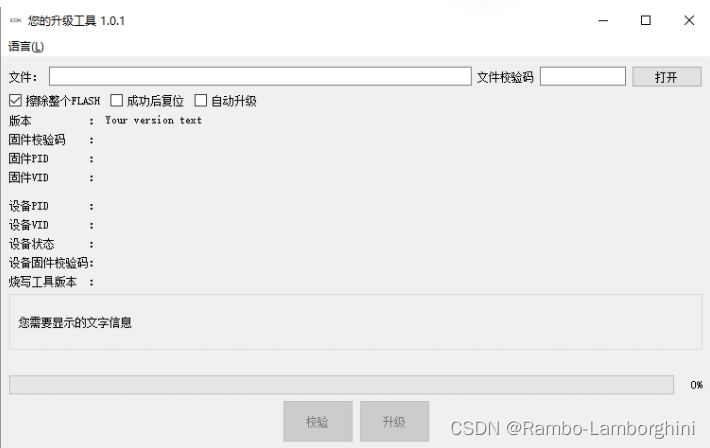

①微程序经过检查无误后通过软件以十六进制写入ROM的相应单元。

②指令经过检查无误后通过软件以十六进制写入RAM的相应单元。

③拨清零开关使所有寄存器、累加器清零,按复位键。

④按一次脉冲键发单脉冲使启动器发送连续脉冲,开始运行程序。

⑤根据指示灯观察R0、R1、总线、MAR、PC、uPC的值。

⑥等到程序运行结束后通过软件读取RAM的值。

八、课程设计总结

8.1遇到的问题

三态门:起初由于不理解RAM的单数据通路而发生读写冲突报错,后来通过使用带有三态门的寄存器MBR调控总线与RAM的数据线连接解决问题。

时序问题:由于把握不好读取ROM微操作和寄存器打入脉冲的顺序,导致数据未在正确时机打入寄存器和RAM读写混乱,经过加灯观测调试和询问老师,最终解决时序问题。uRD和CPuIR是下降沿有效,而各个寄存器CP是上升沿有效,而单脉冲为负脉冲,因此在各个寄存器CP脉冲之前都要加上一个非门。

ALU直传:ALU器件设计功能只能直传A输入端的数据,无法直传B输入端的数据,通过使用加法0+B输入端数据实现B输入端数据的直传。

ALU输入组合问题:我们设计的电路中RAM和R1接入ALU的A输入端,pc和R0接入ALU的B输入端。因而无法做到RAM与R1相加,解决方案是将R1的值写入R0中,接着从RAM中取出相应的值放入R1寄存器实现R1寄存器中的值与RAM相加。

如何判断累加次数x和数组大小n是否相等:起初尝试各种简单电路发现难以完成该功能,接着按照真值表转换逻辑电路的方法成功实现该功能。

连续脉冲下不能正常工作:单步执行时程序没有出现问题,当处于连续脉冲自动执行时会发生跳过某条指令、循环指令等问题,最终发现与实验台有关,更换实验台解决问题。

8.2收获和体会

回顾这次实验,自己收获还是挺多的,加深了对课本知识的认知,也增强了动手能力。

1. 经过这次实验加深了对CPU工作原理的认识,对于CPU的数据传输以及工作方式有了更进一步的了解。学会了简单指令系统的设计以及微程序工作原理。

2.通过课程设计掌握了模型机的设计流程。并从模型及设计流程中学会了解决实际问题,体会到了设计与实际实现之间的不同。

3. 通过实验过程更加熟悉了实验平台的使用,以及模型及设计流程。同时也锻炼了在实验中锻炼自己的动手能力和解决问题的能力。

4.总线结构有利也有弊,好处在于电路结构清晰、数据通路简单、组合多样,弊端在于容易发生读写冲突、总线上只能传输一组数据。

九、小组成员各自的任务和完成情况

1.小组分工

各部件设计、整机实验中,两人共同设计电路框架、画电路图、测试部件、指令和微程序的编写。曾尝试过分工,在检查时发现单独完成部分效果不佳,出现器件连线出错、设计理念不一致、编码不完善的问题,因而选择两人一起边讨论边思考完成实验。

2.完成情况

基础实验和拓展数组累加实验最终均实现,各个指令的实验结果均正确,完成了预期的功能。

附录1:逻辑图

一、总图

二、各部件图

2.1ALU

2.2 8位2选1选择器

2.3 8位寄存器

2.4 8位进制计数器

2.5 连续脉冲启动器

附录2.1:微程序编码

附录2.2:指令编码