接上文 基於Quartus II和MATLAB的FIR濾波器設計與仿真(一):

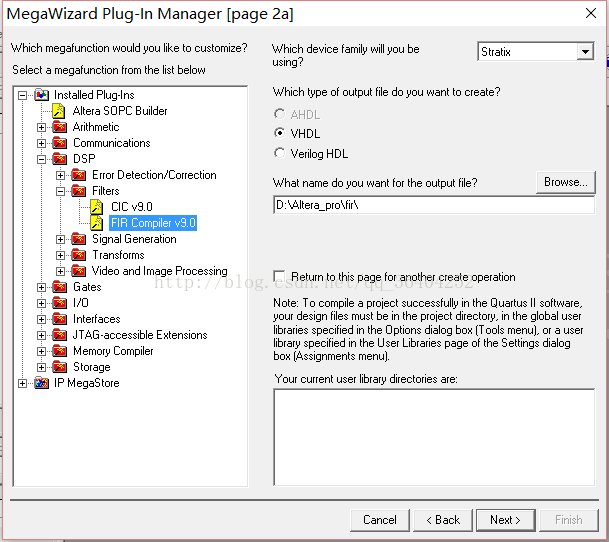

3 QuartusII 調用 IP 核生成 FIR 濾波器模塊

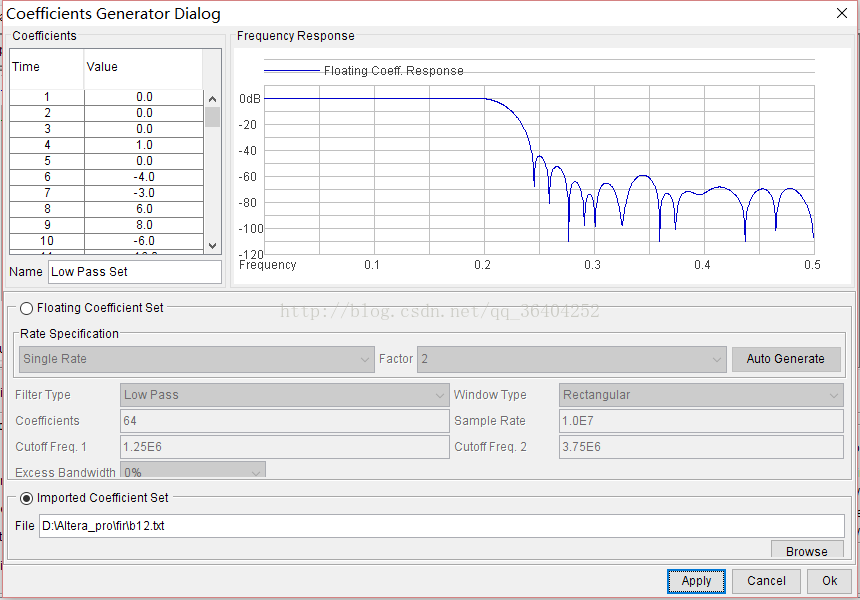

在 Quartus II 中, Altera 提供了一系列可供用戶免費使用的 IP 核, FIR濾波器就包含其中,所以只需要在 Quartus II 中調用 FIR 濾波器 IP 核,導入在 2.1 生成的濾波器系數並設置端口性質即可生成 FIR 濾波器模塊。調用 FIR濾波器 IP 核的設置過程如下圖所示:

點擊 step1

接着點擊step2,勾選所有選項即可,也可不勾選。最后點擊step3 generate 生成模塊。

注意:1.在導入濾波器系數時,要檢查系數文件.txt文件的格式,Quartus II 9.0只支持一行只有一個數據,並且最后沒有分號;2.如果點擊step3 generate后進度條卡住不動可以嘗試打開任務管理器找到“quartus_map”或者類似的任務項然后結束任務即可。

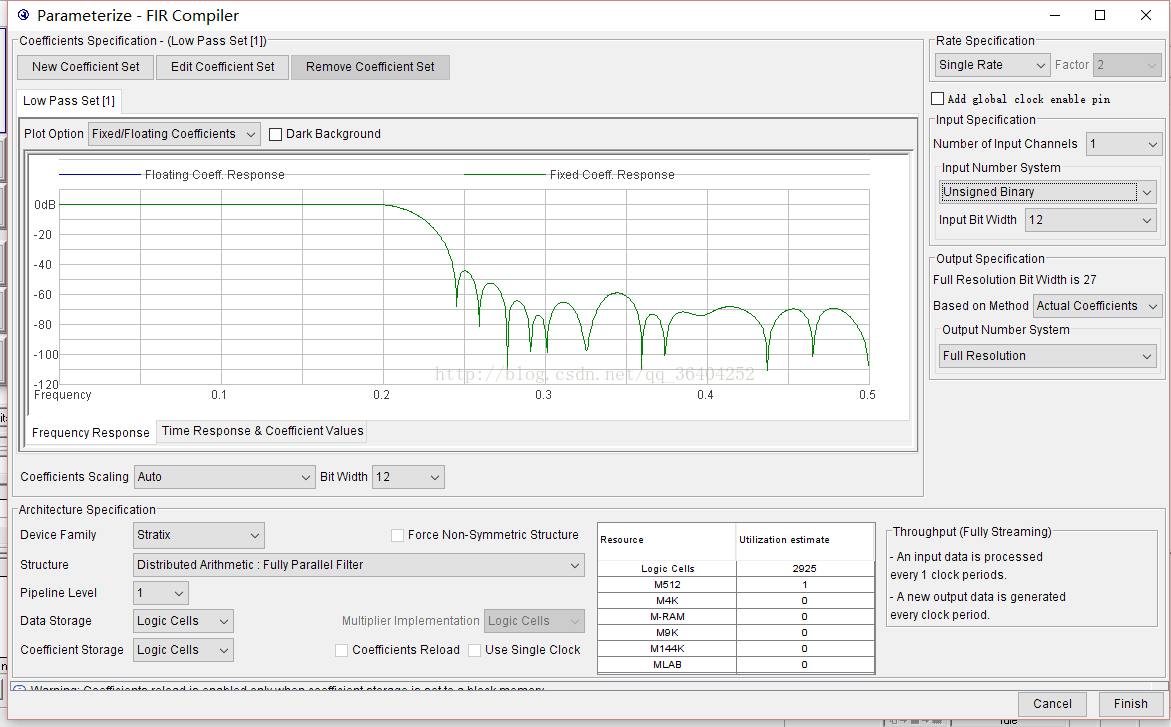

由於在 2.1 中對濾波器系數和輸入信號的值進行了 12 位量化處理,所以把濾波器的系數和輸入數據位寬設置為 12,如圖設置完參數后即可生成濾波器模塊,生成的濾波器模塊如下圖所示:

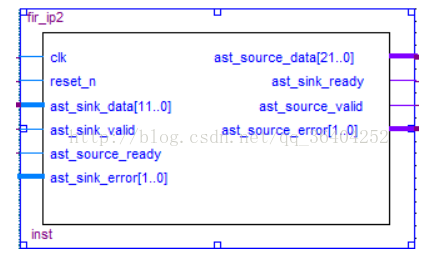

其中 ast_sink_data[11..0]和 ast_source_data[21..0]分別表示數據輸入端口與數據輸出端口, clk 為輸入時鍾信號端口。 4 Quartus II 仿真 FIR 濾波器

4.1 生成一個 ROM 模塊存儲輸入數據

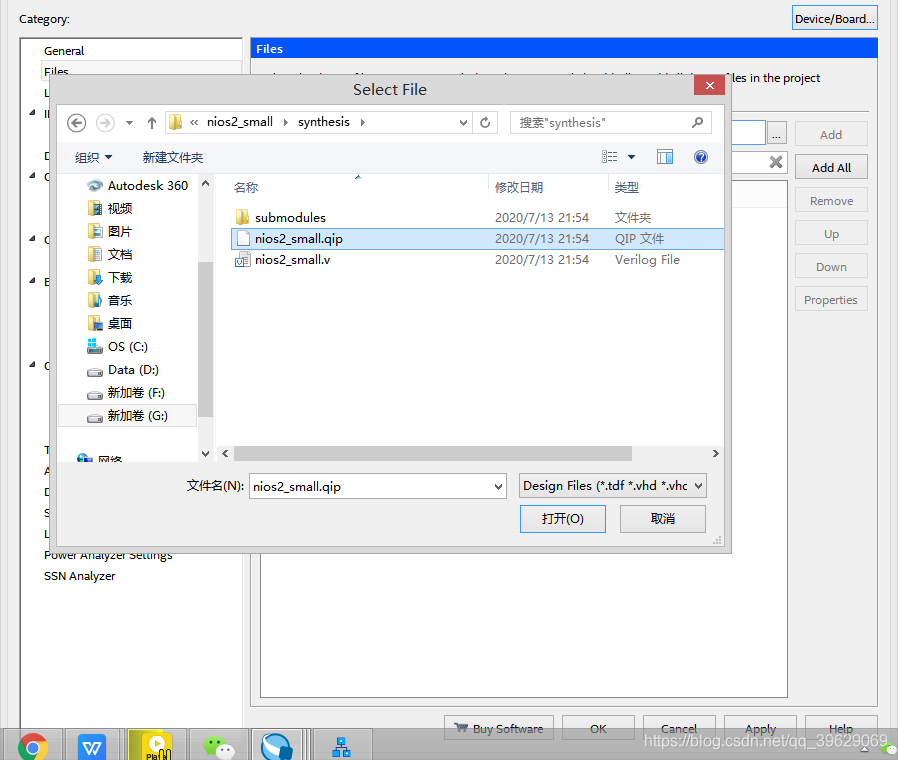

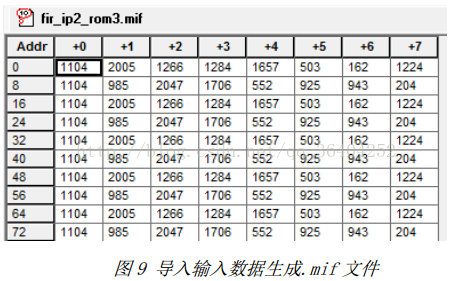

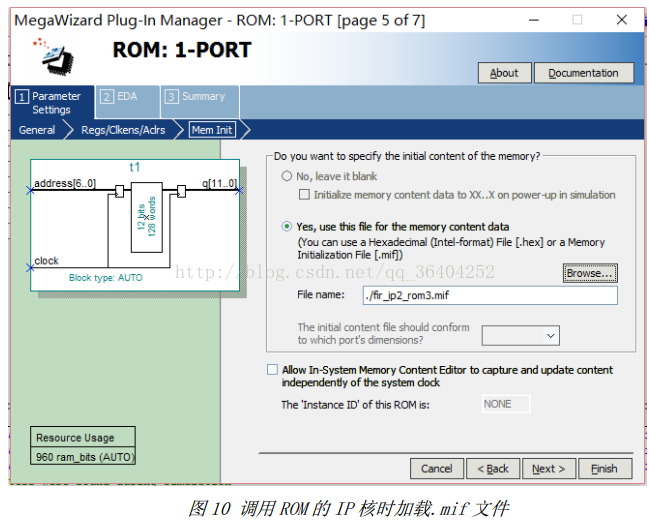

本文需要在 Quartus II 中導入 2.2 在 MATLAB 中生成的濾波器輸入信號作為仿真的數據輸入,所以需要調用 IP 核生成一個 ROM 模塊存儲導入的輸入數據,再連接 ROM 模塊和 FIR 濾波器模塊進行仿真。在調用 ROM 模塊之前首先需要導入輸入數據保存為.mif 文件,之后再在調用 IP 核時加載.mif 文件把輸入數據存入 ROM 中,相當於調用ROM生成一個正弦信號發生器,生成過程如下圖所示:

首先新建一個文件保存為.mif 文件:

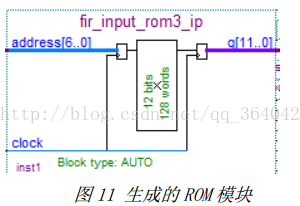

圖中 address[6..0]為地址輸入端口, clock 為時鍾輸入端口, q[11..0]為數據輸出端口,輸出存在 ROM 中的數據 。

4.2 Quartus II 仿真與 MATLAB 繪圖

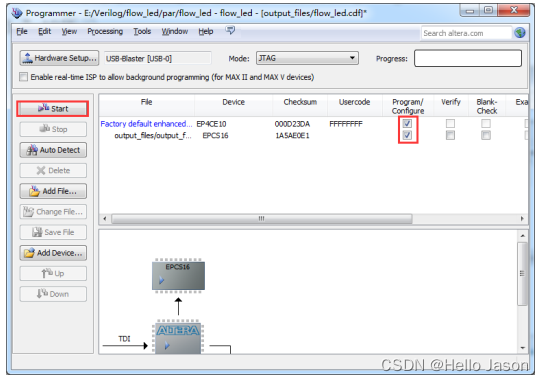

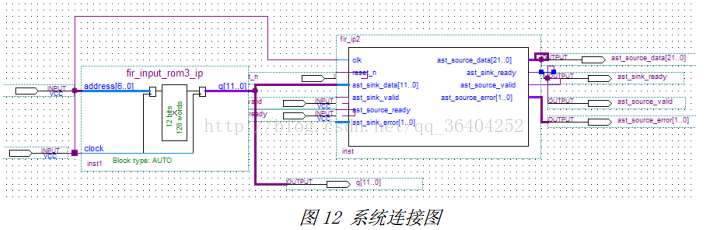

Quartus II 中可以通過建立一個.vwf 文件作為輸入激勵做時序仿真。本文也以這種形式利用 Quartus II 仿真。首先我們連接以上建立的兩個模塊,連接成為一個完整的濾波器。 系統連接圖如下所示:

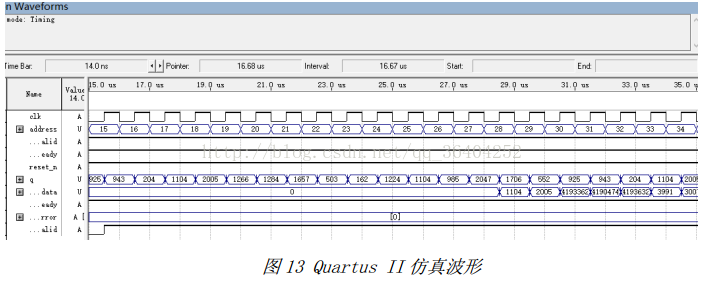

圖 12 中端口 q[11,,0]作用在於測試 ROM 輸出的數據是否與導入的輸入數據一致。 Quartus II 中仿真的波形如下圖所示:

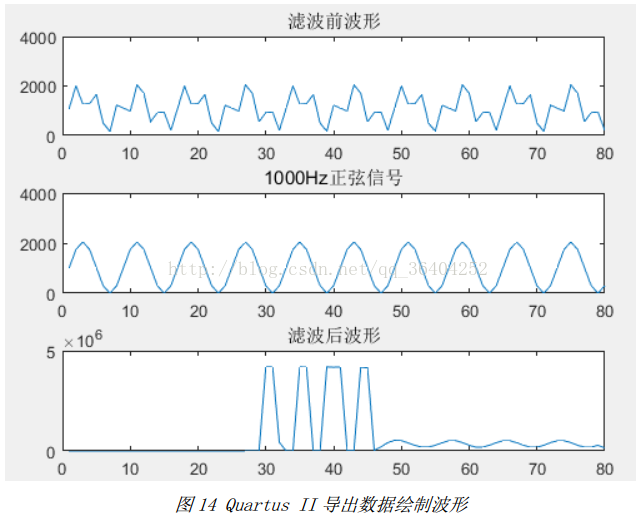

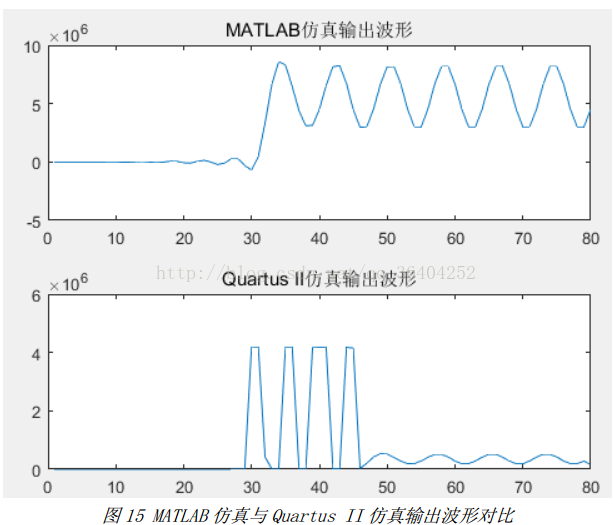

經過核對, q[11..0]輸出的數據與 MATLAB 中產生的輸入數據是一致的,證明ROM 模塊是無誤的。從圖 13 中我們也可以看出, 該 FIR 濾波器也會有一段時間的延時,這與 MATLAB 中的仿真結果是一致的。由於 Quartus II 中只能顯示低電平和高電平,無法繪制正弦函數波形,所以本文選擇將波形文件中的輸出數據導出到 MATLAB 中繪圖觀察結果。在MATLAB 中繪制的圖如下所示:

由圖我們就可以看到橫坐標 0-29 對應的是 FIR 濾波器的延時,是正常的,而橫坐標 29-46 對應的波形是失真的波形,失真原因還有待深入研究, 橫坐標46 之后對應的波形則與 MATLAB 仿真波形一致,是正確的,並且在濾波之后的信號中還存在 1000Hz 附近頻率的噪聲。仿真結果表明,該設計整體式可行的,主要存在的問題就是正確輸出之前

的一段輸出失真原因有待深入研究,在取輸出信號時也要注意處理這段失真波形。

注意:1.由於數據量不大,我是直接將Quartus II中的輸出數據手動輸入到MATLAB中建立一個新的變量然后繪圖的,直接導入數據到MATLAB中網上也有教程,但由於采樣點數的不同可能導致繪制的圖和MATLAB中原來繪制的輸入波形不好對比頻率。

2.注意到在輸出波形的前面一段有明顯的失真,經過驗證是因為我輸入和輸出都設置為了無符號變量,而實際輸出是有正有負的,所以導致出現了太大的數,后面我也改設成有符號數驗證過是無誤的,因為當時沒有截圖保存所以沒有上傳圖片,大家可以自行嘗試。