参考达尔文公众号:https://mp.weixin.qq.com/s?__biz=Mzg5MDIwNjIwMA==&mid=2247496018&idx=1&sn=f8109b6f5b5ea3a175e52eb7074bb7bc&chksm=cfe293c5f8951ad3570a64a07ce0deba1ec12f3c8d0a15bbf1c64ed25e5faca46ef5974fef72&mpshare=1&scene=23&srcid=0803nlTiigTFnaIxL8qt2Oko&sharer_sharetime=1628239001949&sharer_shareid=b3cf96bbd8b8c72ec5d099a7c5bef855#rd

1、Verilog HDL的数值集合有4种基本的值组成,它们是:( )

0低电平

1高电平

x未知态

z高阻态

2、TTL与非门的空余输入端错误的处理方法是?( )

A 、接地

B 、通过1k欧电阻接地

C 、接高电平

D、 空置

E 、通过1k欧电阻接高电平

解析:

对于TTL 与非门,只要电路输入端有低电平输入,输出就为高电平,只有输入端全部为高电平时,输出才为低电平。根据其逻辑功能,当某输入端外接高电平时对其逻辑功能无影响,根据这一特点应采用以下四种方法:

1)将多余输入端接高电平,即通过限流电阻与电源相连接。所以E选项正确。

2)根据TTL门电路的输入特性可知,当外接电阻为大电阻时.其输入电压为高电平。这样可以把多余的输入端悬空此时输入端相当于外接高电平。所以D选项正确。

3)通过大电阻到地,这也相当于输入端外接高电平。所以B选项正确。

4)当TTL门电路的工作速度不高,信号源驱动能力较强多余输入端也可与使用的输入端并联使用。

3、下面的逻辑代码哪些可以综合( )

解析:本题目主要考察了对Verilog-2001相关语法的了解

这道题目也是基础的语法题,首先A选项我们知道“#”主要在用于仿真的Testbench中出现,“#”后面往往跟具体的数值或常数参数,表示延时多少个时间单位,所以A选项错误。此外initial也不可综合

B选项是用到了函数功能,并调用了这个函数,在语法中规定函数是可以被综合的,但函数多出现在用于仿真的Testbench中,在可综合RTL设计中很少见,所以不要以为不可综合,所以B选项正确。

C选项用了for循环,大家往往以为不可被综合,如果单纯写for是不可被综合的,但题目中的代码还用了一个特殊的语法就是generate,generate往往和for一起被使用,主要用于逻辑复制,是IEEE Verilog-2001标准的新语法。IEEE Verilog-2001标准相较于IEEE Verilog-1995标准有不少实用的重大改动,大家可以到网上自行查询或者查看IEEE的手册对比,几乎所有的EDA工具都支持IEEE Verilog-2001标准,所以可以放心大胆的使用,所以C选项正确。

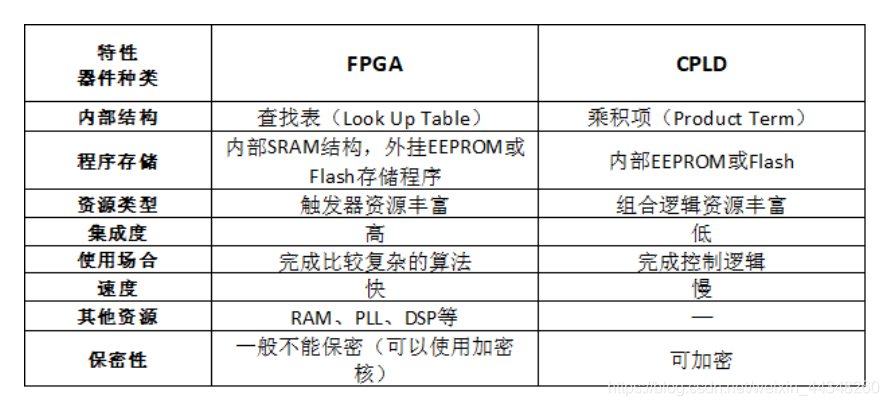

4、FPGA和CPLD的区别有( )

A FPGA是易失性逻辑器件;CPLD是非易失性逻辑器件

B FPGA的保密性比CPLD差

C FPGA规模和逻辑复杂性比CPLD高

D FPGA基于LUT,CPLD基于乘积项或LUT

解析:

A、因为FPGA内部是SRAM的结构,所以是易失性逻辑器件,只能外挂EEPROM或Flash;而CPLD内部有EEPROM或Flash,所以是非易失性逻辑器件,所以A选项正确

FPGA一般不能保密,需要使用额外的加密核,而CPLD可加密,所以B选项正确。

FPGA的规模往往比CPLD要大,用于完成比较复杂的算法,而CPLD因为资源有限往往用于简单的控制逻辑,所以C选项正确。

其实大家比较拿不准的就是D选项的后半句,前半句肯定毫无疑问,FPGA就是基于查找表LUT的结构,CPLD主要是基于乘积项的结构,那CPLD有没有基于LUT的结构呢?其实是有的,就是我们熟悉的Altera的MAXII系列。Altera的MAXII系列产品的核心采用了新的体系结构,即摒弃了传统宏单元体系结构而采用查找表体系结构,以满足CPLD设计者的需求。基于LUT体系结构的MAXII采用了TSMC的6层金属0.18微米嵌入式Flash工艺,使得其裸芯尺寸是相同工艺下同类器件的四分之一,所以D选项正确。

5、在FPGA设计中,如果时钟信号没有走全局时钟网络,会有什么影响?( )

A 时钟的SKEW会显著增大

B 减少功耗

C 会影响时序

D 驱动能力增强

解析:本题目主要考察了全局时钟网络的相关知识

全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。FPGA中的全局时钟网络资源,贯穿整个器件,为各个Bank中的各个资源类型(IO、LE/ALM、乘法器、M9K等)提供服务。走全局时钟网络的信号具有低偏斜(Skew)、低抖动(Jitter)以及高扇出(Fan-out)的特点。所以如果时钟信号没有走全局时钟网络就会导致较高的时钟偏斜(Skew),从而影响时序;而扇出少,对应的就是驱动能力减弱。

适合使用全局时钟网络的控制信号有:时钟、复位、内部逻辑产生的锁存信号、使能信号等,即具有高扇出(Fan-out)、低延时(Delay)要求的信号

一个系统可能使用多个时钟,但是在每个时钟控制的区域内部都设计成一个同步的子系统,通过时钟树综合、插入缓冲器减少时钟的偏移。这种方法在时钟网络上添加了大量的缓冲器,时钟网络消耗的功耗也增加。所以在异步设计里面,不需要全局时钟,两个模块通过握手信号进行交互,这时候就可以减少功耗,因此异步设计也是降低功耗的一种方法。所以只有D选项不选。

6、采用可编程逻辑器件有哪些优点?( )

A 系统的器件使用数量大大减少

B 开发周期短

C 可以减小产品体积,降低电源功耗

D 设计灵活,易于修改升级

E 可以借助设计工具自动进行设计

解析:本题主要考察了可编程逻辑器件的使用特点

可编程逻辑器件也就是FPGA之所以有很大的需求是因为它有很多不可替代的优点,首先就是FPGA可以减少在一个系统中其他数字芯片的使用,这些功能都可以在FPGA中来实现,FPGA的可配置管脚也很多,往往可以解决很多IO使用较多的情况。其次FPGA相对于ASIC的开发周期要短很多,而且非常灵活,易于修改升级,而不需要更换新的器件,往往用于那些更新较快的产品领域,而ASIC从设计之初到最后的产品量产需要的周期往往更久,且ASIC的功能往往比较单一,如果出现新的应用场景或协议就需要重新设计,所以A、B、D选项正确。

在FPGA的设计中厂商所提供的EDA工具往往可以很大程度帮助我们实现自动设计,比如编译、综合、布局布线等等,而ASIC在这方面的设计往往需要多人合作完成,且添加各种约束,自动化程度相对低一些,因为E没有说完全自动化,如果理解为和ASIC设计的对比则选。C选项中可以减小产品体积从减少器件使用数量上来讲是正确的,但是后半句降低电源功耗是不对的,FPGA的功耗往往要比实现同样功能的ASIC器件要高。因为FPGA的内部结构是相对固定的,使用时并不能保证所有资源被完全使用,还会有冗余逻辑消耗功耗,而ASIC可以专门去做功耗的约束以及通过各种方式降低功耗,所以和ASIC的对比C选项不选。