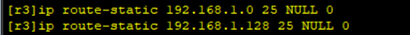

1. 1bitD型触发器verilog 程序

2.RTL等效电路图

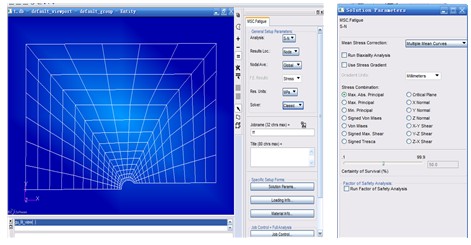

3.仿真结果

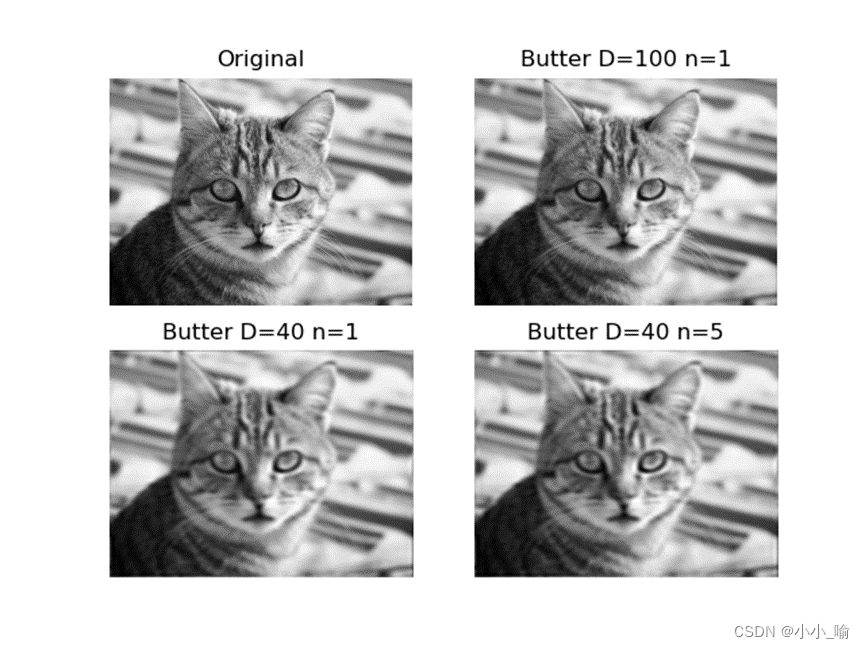

当CLK上升沿的时候,q值变化,就是此时此刻d的数值(高低电平),当上升沿发生在高电平区间,q值就是高电平;当上升沿发生在低电平区间,q值就是低电平

此时时因为有always,所以遇到上升沿就会有数值变化。

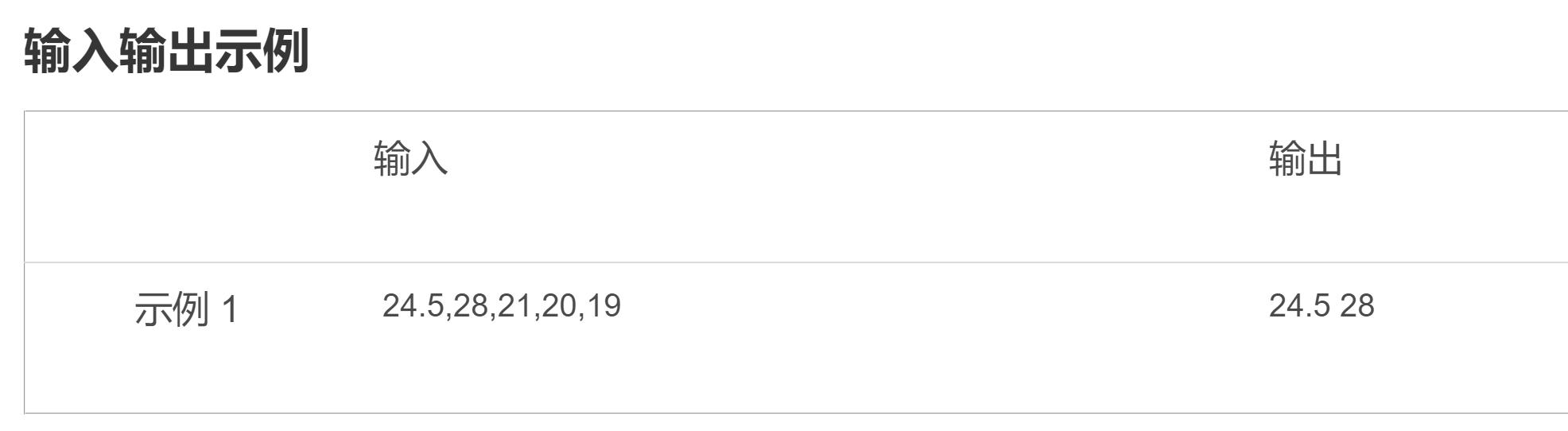

下面在介绍几个仿真实例进行分析:

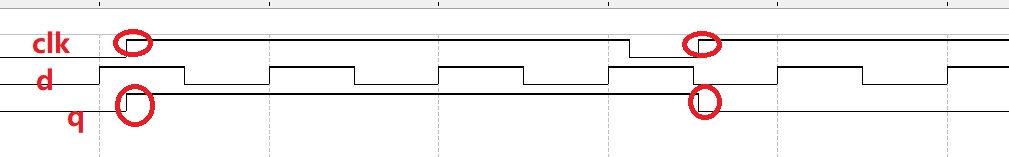

根据verilog程序,只需要关注clk的上升沿即可;

当clk为上升沿那一时刻,d的值还是低电平,因此q的值为低电平;

并且下降沿不会引起q值的变化,因此q值每个周期都是低电平。

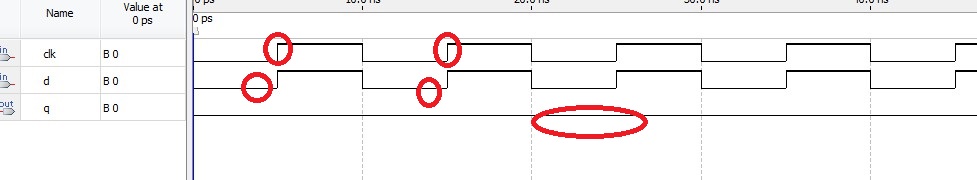

上图中,clk和d的相位相差半个周期,此时每次clk上升沿开始的时候,d的值还是高电平,因此q的值为高电平。而下降沿不会导致q值的变化,因此每个周期,q值都是高电平。

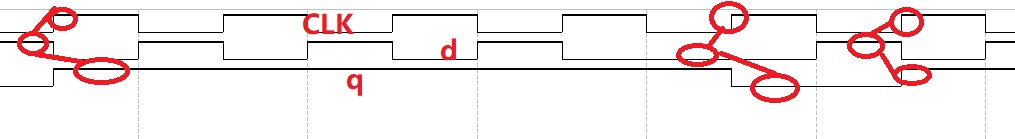

上图中第一个红圈中上升沿开始,d值还是高电平,因此q值为高电平;

第二个红圈中的上升沿开始后,d值还是低电平,因此上升沿此刻开始q值为低电平;

第三个红圈中上升沿开始,d值还是高电平,因此q值变为高电平;

总结,对于触发器,只看电平是高低电平哪个有效,关注有效电平即可。