文章目录

- Compression Analysis

- analyze_compression

- Preparetion For EDT Logic Creation

- Parameter Specification for the EDT Logic

- Dual Compresson Configuration

- Define Dual Compression Configurations

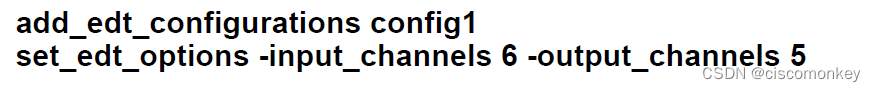

- ASYmmetric Input and Output Channels

- Bypass Scan Chains

- Latch-Based EDT Logic

- Compractor Type

- Pipeline Stages in the Compactor

- Pipeline Stages Added to the Channel

- Longest Scan Chain Range

- EDT Logic Reset

- EDT Architecture Version(EDT IP Version)

- Specifying Hard Macros

- Pulse EDT Clock Before Scan Shift Clocks

- Reporting of the EDT Logic Configuration

- EDT Control and Channel Pins

- DRC check

- Creation of EDT Logic Files清单

本篇文章是对EDT logic的creation的介绍,本文并非完全是对tessent Kompression 文档的完全翻译,而是融入了自己的理解。

不得随意转载

CSDN博主:ciscomonkey

Compression Analysis

你可以通过优化更改 channel ratio(scan channels的数目以及scan chain的长短)来生成测试向量,从而评估下面的参数。

1、testcoverage

2、data volume:决定有多少pattern的数据生成,是否tester能够装得下。

3、ATPG baseline:详情请见P61 ATPG Baseline Generation

你可以使用 analyze_compression 来探索不用的ratio对测试数据的影响。

analyze_compression

使用该命令的目的就是在还没有做EDT之前,先预估一下如果按照该EDT的架构,那么coverage、pattern这些结果会是多少,如果符合你的预期,那么你再按照该方案去做EDT。

在你打ATPG之前,你可以按照如下分析;

set_fault_type stuck

set_fault_sampling 5

analyze_compression

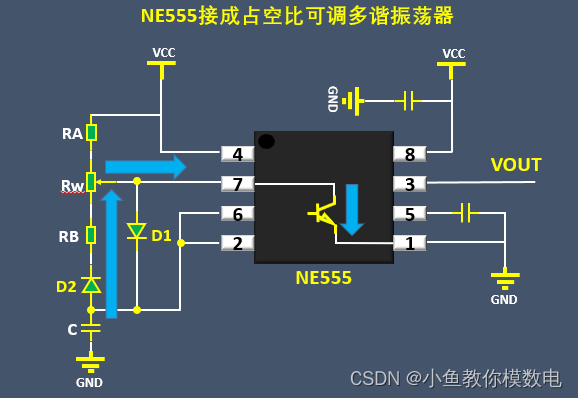

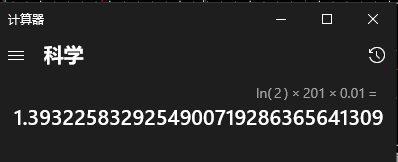

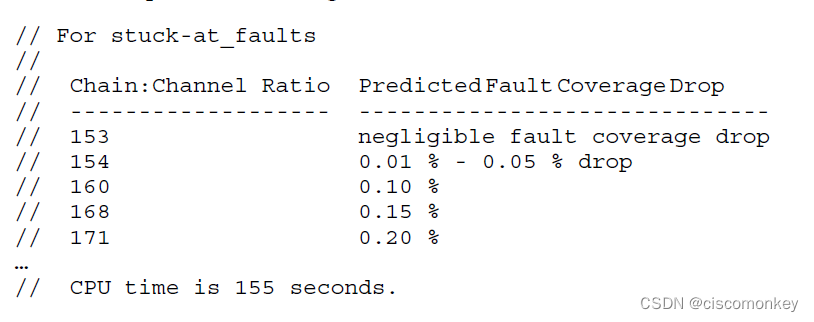

该cmd会从coverage变化微乎其微的channel ratio开始,如下图的153 的ratio,这是微乎其微的coverage的变化,然后一直到1%的落差。

此外,你还可以手动的定义chain和channel 以及一些power的参数等,指定某一个block,是否做EDT。然后分析。

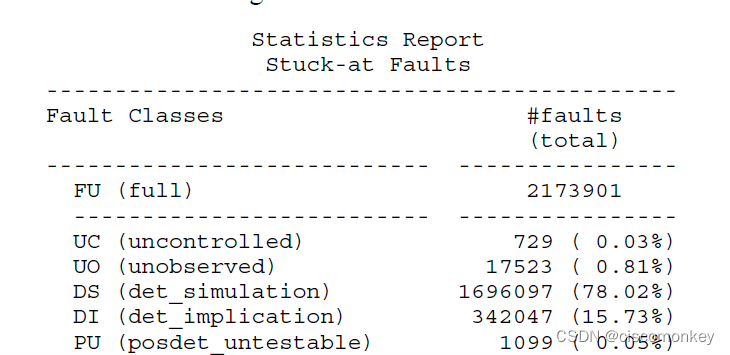

如下图所示,Tool会生成临时的testpattern,并且display statistic report出来,这样可以避免去生成EDT,然后又建立ATPG环境等一系列FLOW,就可以完成cov以及pattern的预估。

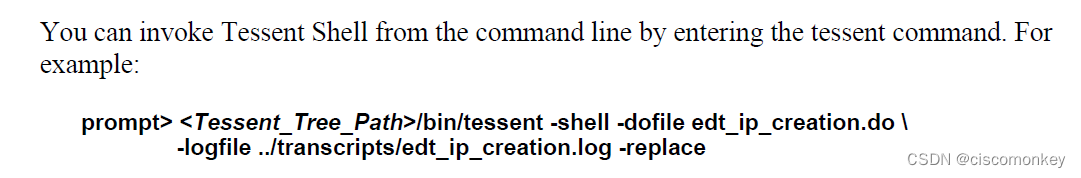

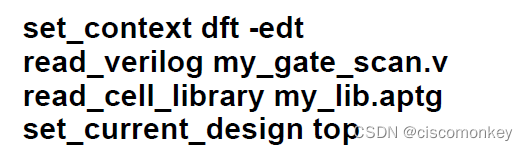

Preparetion For EDT Logic Creation

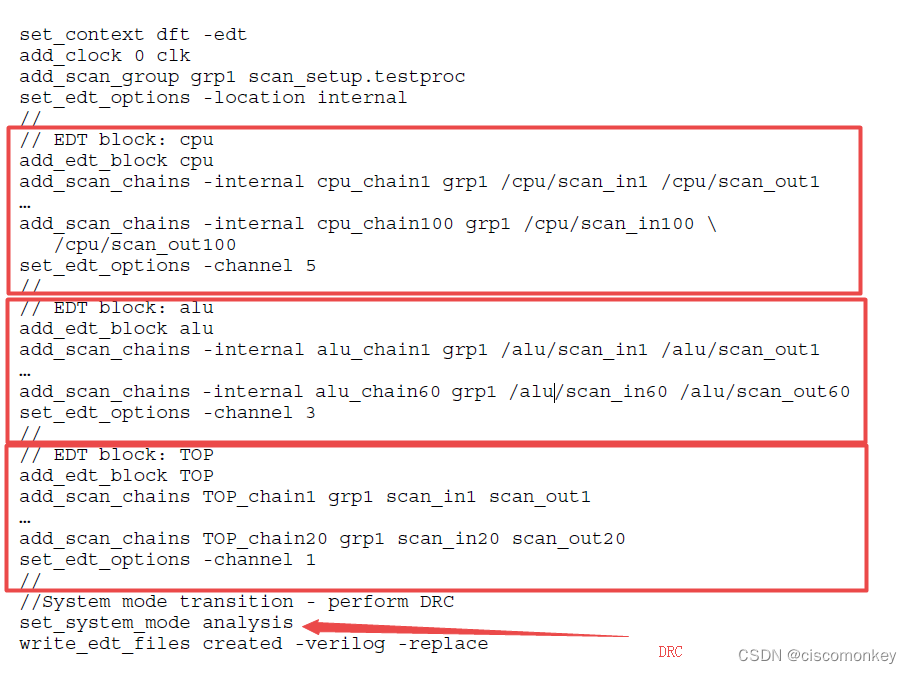

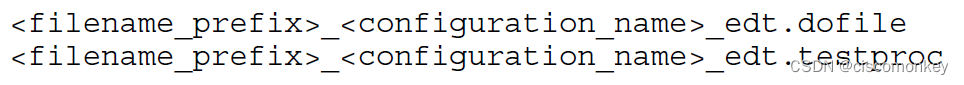

如下图所示,可以在dofile文件里面执行这些配置。

例子:

该例子show 3个EDT blocks 的IP creation: CPU 和alu have internal scan chains,并且存在TOP 有top-level scan chains。 并且cpu和alu的blocks都被定义在instance的pin上,并且不会带到top level。 这些scan pins 对于top 来说会在top level定义。

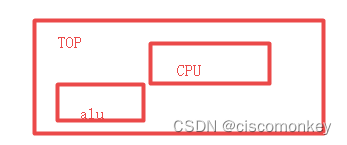

如下图所示,这里我绘制了一个框架图,也就是说CPU和alu内部就有internal scan chain,而在top层也有TOP-level的chain.

并且alu和CPU的internal scan chain都是只拉到其自身的isnatnce的pin上。所以我们看到在CPU和alu上做EDT的时候,我们需要add_scan_chain -internal的选项。

但是在做top level的时候是不需要的。

而且通常我们不会采用这种TOP - DOWN Flow,而是一个block一个block的做EDT,采用bottom-UP Flow. 通常用不到-internal选项。

Tessent shell(dft -edt)支持这种定义internal chain的Flow,但是对于TestKompress是不支持-internal 这种使用方法的。否则会报告如下的错误。

Parameter Specification for the EDT Logic

set_edt_options 可以指定EDT logic的诸多参数

比如下面指明channels

set_edt_options -channels 2

此外,还有重要的参数,比如internal or external to the design core(internal flow 还是external flow)

此外还可以指定是创建DFF-based 还是latch-based EDT logic,这一点是不是非常类似于DFTMAX和DFT MAX Ultra。

以及 是否要插入bypass电路,pipeLine, lockup cell in decompressor.

Dual Compresson Configuration

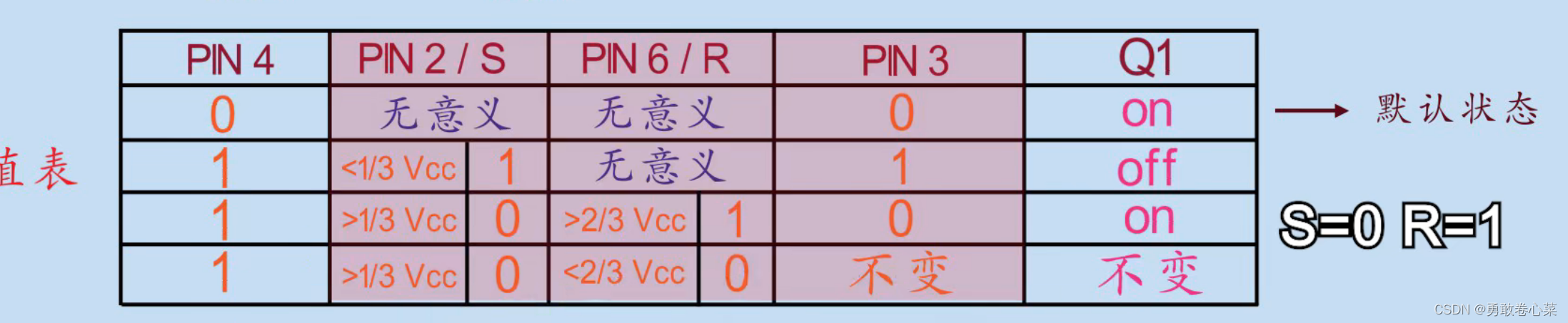

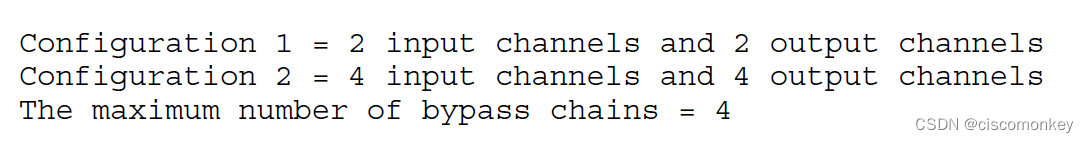

dual(成对)的压缩配置,可以通过一个EDT logic从而生成两种不同的测试阶段,比如CP测试和FT测试。从而就会增加一个额外的EDT pin用来控制选择哪一种configuration被激活: edt_configuration , block与block之间的channel 参数可以不相同,但这属于说top down flow,实际我们一般不会这样做。如下图所示,通过

set_current_edt_block 来指定要做压缩的block,然后通过制定set_current_ed_configuration 来设置不同的input/output channel,从而实现dual compression parameter的目的。

对于每个EDT来说,虽然有dual compression configuration parameter,但是可以计算ratio的时候,要以最高的ratio来计算这个EDT的ratio。

提问,是否set_current_edt_configuration是不是只能设置两个?

如果要控制走哪个configuration,必然有一个控制的channel,详情请通过下面的cmd来查看

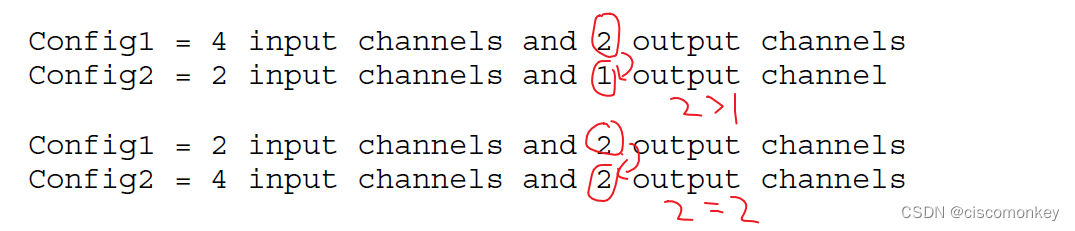

对于设置dual compression 参数的原则:对于input channels更高的通道,那么与之对应的configuration的output的通道也要比另一个configuration高,如下图所示,因为 对于input channels来说 4更高,那么与之对应的output channel为2 也要更高。

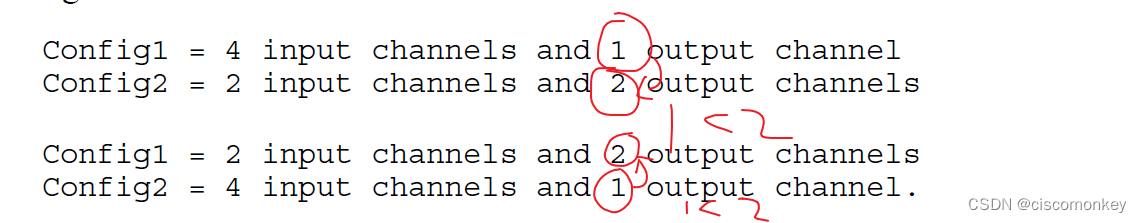

如下图所示,是不合法的配置,对于输入通道为4的channel,与之对应的通道输出为1,小于另一个配置输出通道为2.

如下图所示,bypass chain 设置为2 3 4 均可,bypass chain的输入输出要相等。

局限:

1、analyze_compression 对这种dual compression configuration是不生效的。

2、basic compactor并不支持超过一种configuration,默认情况下,工具使用的是Xpress compactor.

3、默认情况下,对于dual compression configuration不会有DRC需求,你必须要run DRC在每一种configuration在不同的测试pattern阶段。

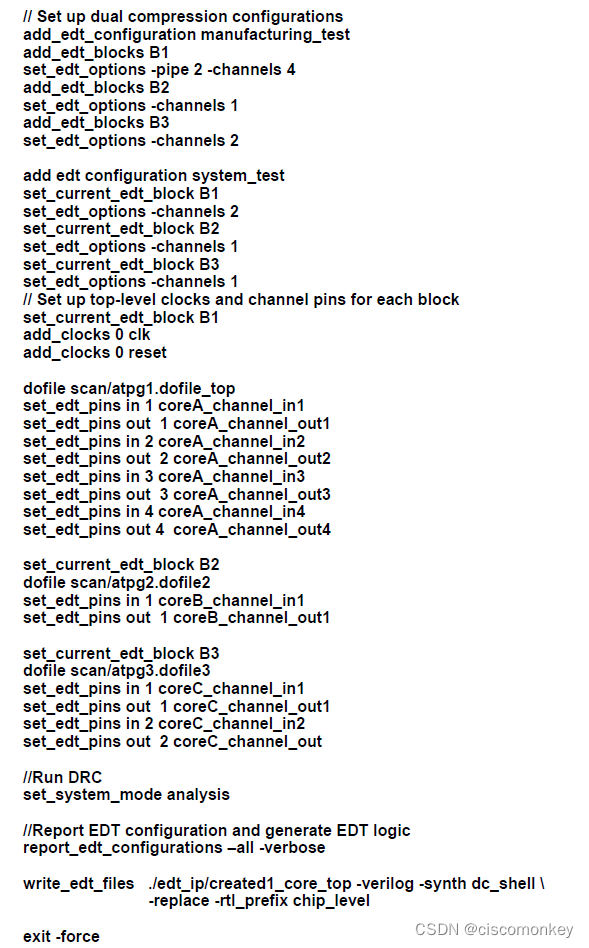

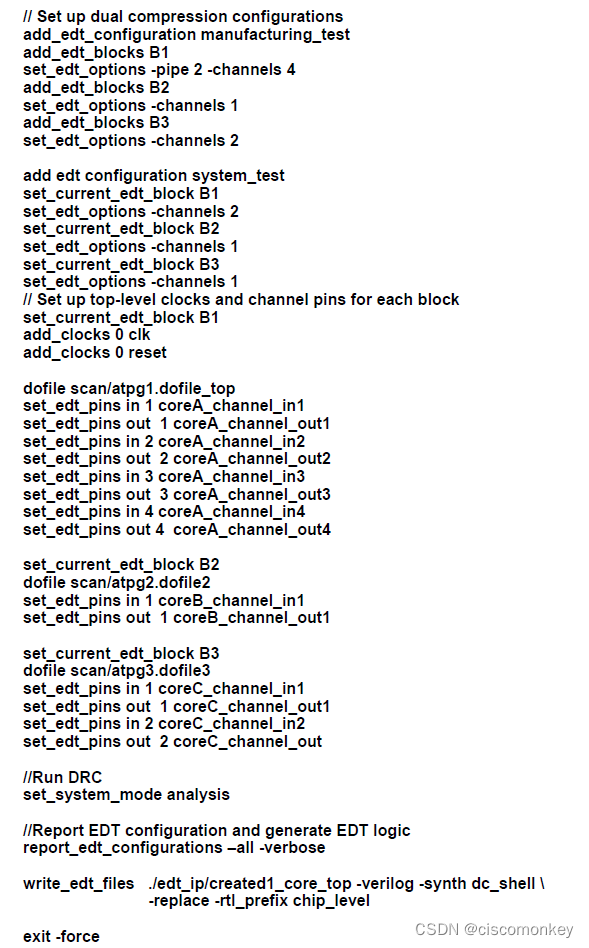

Define Dual Compression Configurations

run DRC 你需要基于每一种configuration。

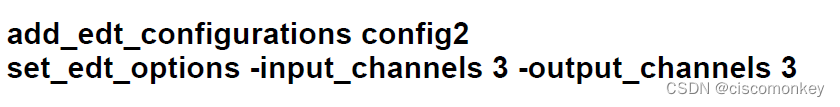

生成EDT logic,独立的dofile文件以及procedure文件,会在每一种configuration 创建。创建的命名,在使用write_edt_files的时候,会用如下前缀:

如下图所示,是基于模块配置EDT的demo脚本:

如下图所示,是基于Top层,然后分别去指定要做EDT的block 的脚本,下面这种TOP-DOWN Flow一般不采用这种方式:

ASYmmetric Input and Output Channels

ASYmmetric 英[ˌeɪsɪˈmetrɪk] 不对等的

你可以指定不同的输入channel和输出channel,通过set_edt_options 的-input channels 和-output_channels开关

Bypass Scan Chains

通过配置set_set_options -bypass_chains integer 来配置有多少条bypass chain,也就是我们以前所说的Only Internal Chain,默认情况下bypass chain的数目是等价于input channels以及output channels的。但是,如果input channels和output channels的数目如果不相同的话,将默认采用小的那个值,因为对于bypass chain来说,一个input channel对应一个output channel。你可以指定小于默认的bypass chain值。

Latch-Based EDT Logic

Tessent支持mux-DFF以及LSSD scan architecture(Latch Based EDT Logic),Tessent默认是创建DFF-based EDT Logic, 如果你想要使用LSSD scan architectures. 需要通过set_edt_option -clocking 来指定。

Compractor Type

使用-compactor_type 来指定哪一个类型的compactor会在generate EDT logic过程中使用。

默认情况下, 使用的是the Xpress compactor

Pipeline Stages in the Compactor

EDT的logic生成可以将pipeline satges 包含在compactor中

set_edt_options -pipeline_logfic_levels_in_compactor

该名v零可以让你指定最大数量的logic levels(XOR gates)in compactor before pipeline stages are inserted。默认情况下是不会有pipeline stages 插入到compactor中的。详情参考:use of pipeline stages in the compactor P247

Pipeline Stages Added to the Channel

将pipeline stages增加到Channel,当我们generate EDT IP的时候,如果output channels pipeline stage通过set_edt_pins -chainge_edge_at_compactor_output trailing_edge 来知名,那么tessent会在output channel上增加pipeline。需要注意要确保这些pipeline的EDT clock是trailing edge。

Longest Scan Chain Range

有的时候,你可能需要在你的EDT logic生成之后,然后去改变你的scan chains的长度。

通常情况下,你必须要重新生成EDT logic,当这种改变影响到了最长的那条scan chain。

during setup阶段,在你生成EDT logic之前,你可以通过-longest_chain_range 来指定最长的scan chain的范围。

只要随后你去修改scan 的长度的时候,最长的scan chain不要超过这个范围,你就不需要重新生成EDT logic。

EDT Logic Reset

大多数情况下,如果你有设计需要(需要所有的sequential elements 都处于复位状态),你可以提供一个异步复位信号(edt_reset)for EDT logic。

set_edt_options -reset_signal asynchronous

如果你有配置该设置,那么会引入一个新的专属控制pin (named “edt_reset”)

EDT Architecture Version(EDT IP Version)

为了确保老版本创建的EDT Logic 架构可以在新的工具中生成pattern。可以使用 -Ip_version 来指定你想要的EDT架构的版本。

在EDT logic生成的过程中,tool会write一个dofile,这个dofile会包含EDT 指定的cmd,用来提供给ATPG使用,任何set_edt_options的命令都会包含在这个dofile中,这个dofile文件会指定version告诉给ATPG。(我不知道怎么EDT context下写出dofile)

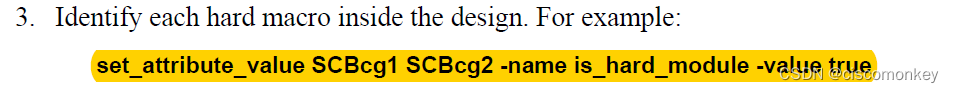

Specifying Hard Macros

为了工具能够识别到一些硬核IP,以及避免工具在bypass mode的时候tracing clock path会修改到这些硬核IP,你可以通过下面标识,给这些硬核添加属性,具体我还没有用到如下的cmd经验。

Pulse EDT Clock Before Scan Shift Clocks

默认情况下,EDT 和scan chain shift clocks是同是pulse的。设置EDT logic pulse在scan shift clock之前,可以使得EDT clock独立于scan chain shift clock ,并且可以带来如下的好处:

1、EDT logic RTL 的creation更加容易。

2、betweent scan chains和EDT logic之间的lockup会被remove掉,只有一个lockup cell会放在bypass chain的中间。

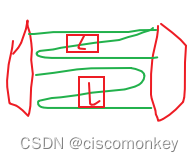

如下图所示,为singgle lockup cell at bypass chain。

3、clock routing变得更加容易,因为LOCKUP cell被用于bypass chain,这些LOCKUP被driven by the EDT clock, 而并非被system clock drive, 消除掉route system clock到EDT logic的需求。

详细见P81

set_edt_options -pulse_edt_before_shift_clocks

Reporting of the EDT Logic Configuration

如下图所示,上面说的这些参数,我们都可以在ATPG 吃入EDT的tcd的时候看到,或者在set context dft- edt 的环境下,用

report_edt_configuration

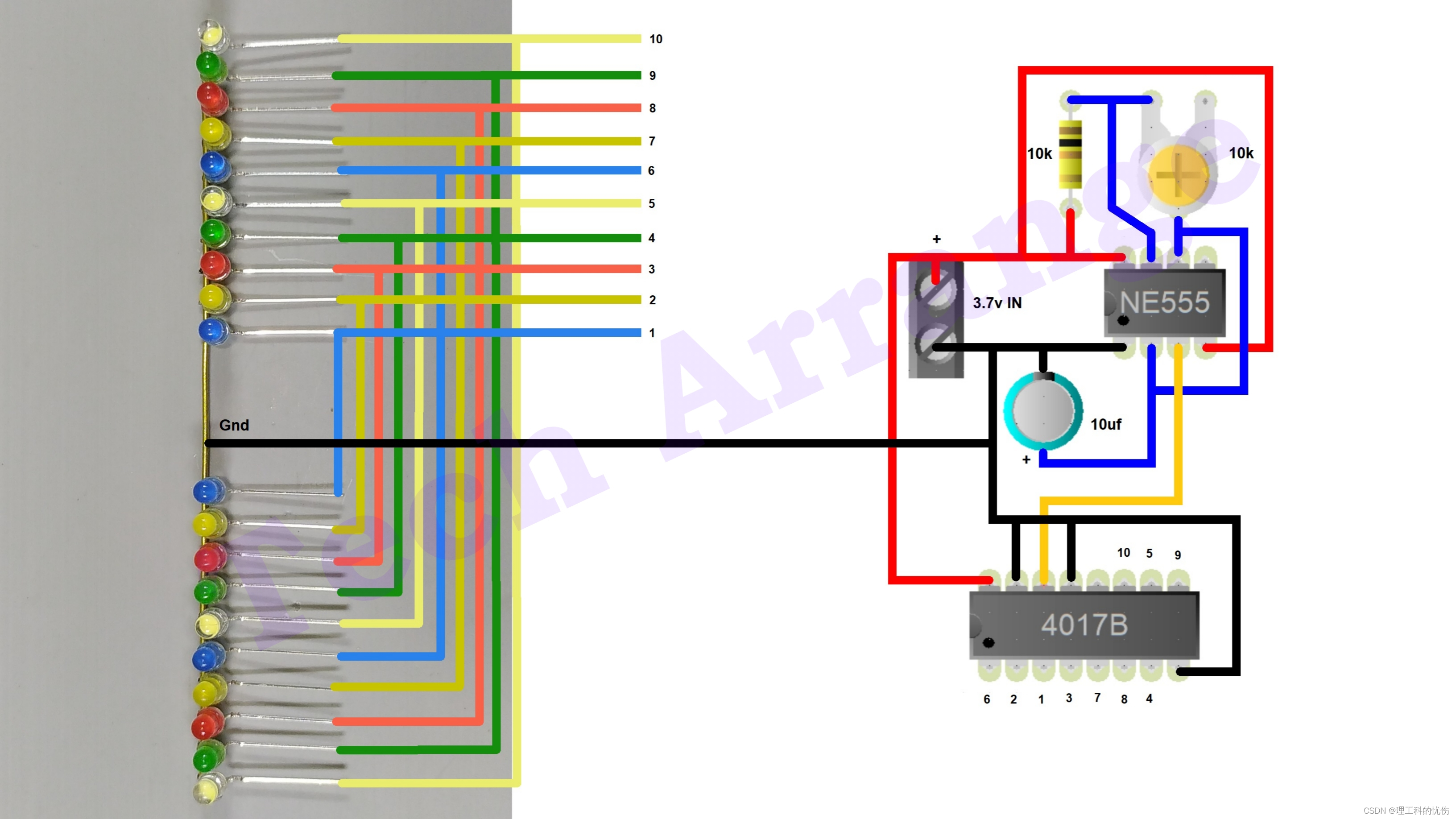

EDT Control and Channel Pins

本节内容是比较核心的一部分

EDT logic包含了控制信号(control pin)以及通道信号(channel pins)

控制信号,比如说edt_clock,edt_update,以及edt_bypass 这些控制信号控制着EDT是如何进行工作的。对于通道信号来说,比如edt_channels_in以及edt_channels_out 这些信号是scan channels。

以下图片是EDT logic所要用到的pins

scan channel input pin : 没有限制

scan channel output pin: 不能share bid或者tri-state 在core level。因为tool会插入一个mux。

EDT Clock:EDT clock必须要要定义为时钟,并且约束其off状态,注意不能share with bus bit,否则 DC 可能不接受这种bus时钟。

另外EDT时钟必须要share一个非时钟的function pin,并且不能影响到其他的scan cell,否则的话,这些scan cell会在load_unload 过程中被干扰,当EDT clock pulse的时候。这种限制会影响cov,你最好使用一个专门的时钟。

-

EDT reset,同EDT clock一样。

-

EDT update :可以被和任何一个non-clock pin share。因为 EDT update pin并不需要constraint, share 并不会被影响到。

-

Bypass (optional): 必须要during scan的时候被force,force on in the bypass test mode,在EDT test procedure mode的时候force off。

-

EDT_configuraton(optional): 在scan shift 的时候,必须要被force上selected configuration.

-

scan enable 如果是bypass mode, 这个pin必须要是专业用的,否则么有其他限制,EDT 使用SE,只有在share channel out pin的时候。

report_edt_pin 查看edt的pin,以及shared pin

set_edt_pin 定义share pin,实现shared 功能

DRC check

DRC的步骤发生在当你从setup mode 进化到set system mode analysis 的时候

P98 待再看

使用report_edt_configurations 可以查看edt的配置信息。

Creation of EDT Logic Files清单

使用TCD的好处是,在ATPG的时候你可以取代传统的dofile文件。

使用write_edt_file 命令会吐出一些必要的文件。

1、created_edt_top.tcd 文件

当使用EDT pattern的时候,吃入该文件。

2、created_edt_top.v EDT 的.v 文件(仅仅当使用external mode的时候)

Top-level wrapper that instantiates the core

3、created_edt.v 使用RTL描述的EDT logic

4、created_edt.icl EDT 的ICL文件

5、created_edt.pdl EDT logic的PDL文件

6、 created_core_blackbox.v blackbox描述

7、created_dc_script.scr DC综合EDT logic的脚本

8、created_rtlc_scripts.scr RTL compiler 综合EDT logic的脚本

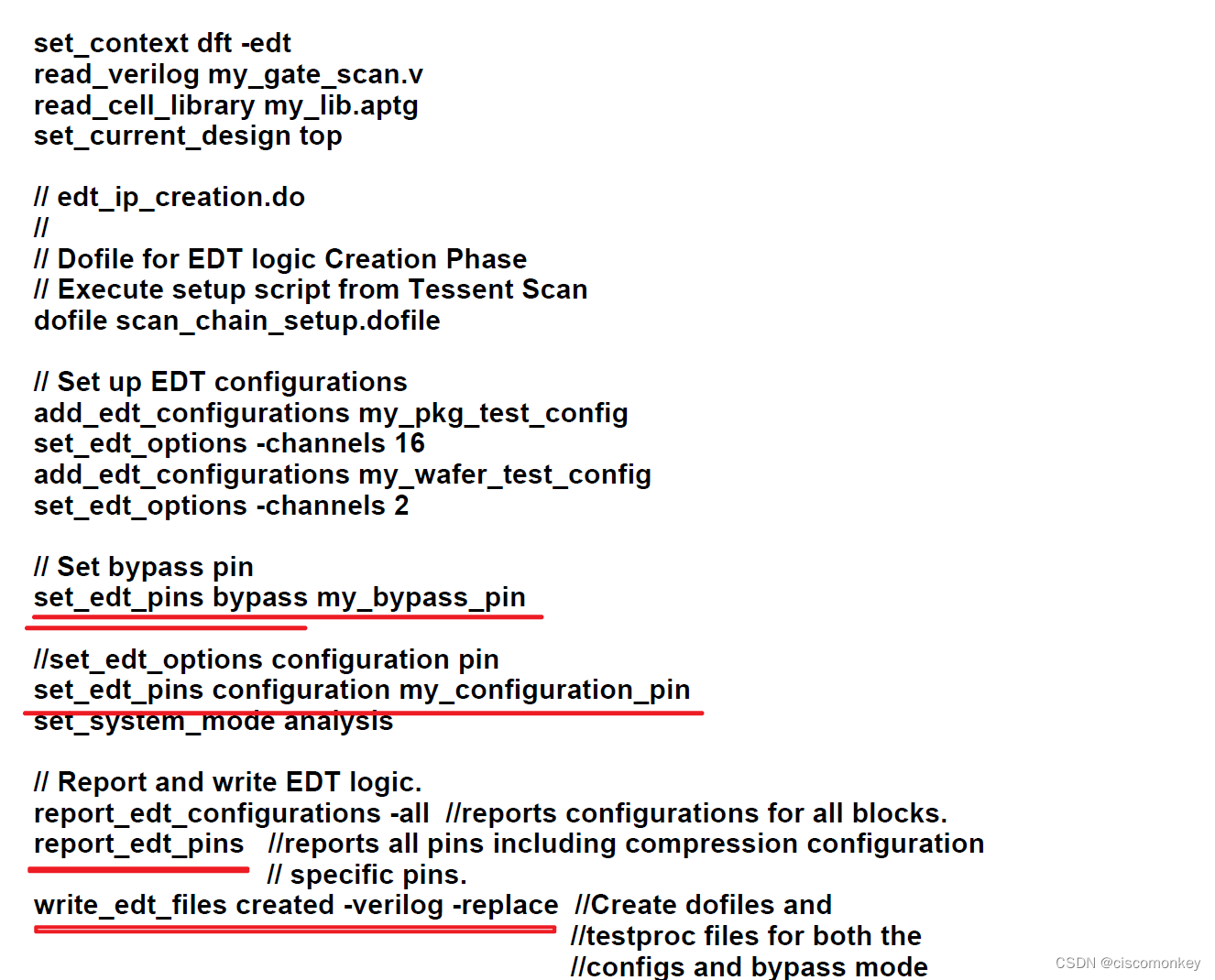

如果不使用TCD flow,tool还会写出下面的文件

created_edt.dofile dofile文件,用于pattern生成

created_edt.testproc test proc 文件用于测试向量的生成。

created_bypass.dofile dofile文件用于bypass mode

created_bypass.testproc test proc file用于bypass mode

P102 EDT logic描述