文章目录

- 1.makefile进行工程管理

- 2.文档里面输入的内容

- 3.如何运行这个makefile文件

- 3.makefile 的变量

- 4.其他

1.makefile进行工程管理

先创建一个名称为makefile或者Makefile的文档

2.文档里面输入的内容

输入相应内容的时候,要遵循相应的规则

规则:用于说明如何生成一个或多个文件;

规则格式:

target:dependency_files //目标项:依赖项

<TAB>command //command必须以【tab】键开头

规则就是为了生成某个文件。

目标项:这个就是你要生成的文件名;

依赖项:要生成目标项需要的文件;

编译命令:如果有依赖项生成目标项;必须以【tab】键开头;

反斜杠:\可以换行,便于makefile的易读

在这个 makefile 中,目标文件(target)包含:执行文件 test和中间目标文件(*.o),依赖文件(prerequisites)就是冒号后面的那些 .c 文件。每一个 .o 文件都有一组依赖文件,而这些 .o 文件又是执行文件 test 的依赖文件。

依赖关系的实质上就是说明了目标文件是由哪些文件生成的,换言之,目标文件是哪些文件更新的。

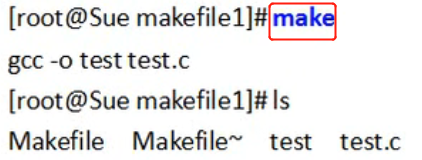

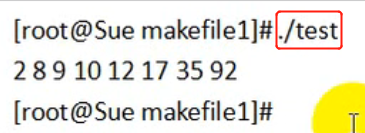

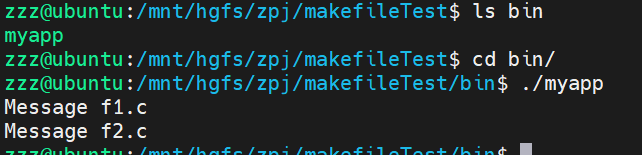

3.如何运行这个makefile文件

在该目录下直接输入make就可以生成执行文件test

总结:

1.目标文件不存在,执行命令

2.文件已经更新,执行命令

3.Makefile的第一条规则为最终的目标

2.在验证仿真中,最长使用的则是伪目标,下面介绍伪目标

# .PHONY 是Makefile文件的关键字,表示它后面列表中的目标均为伪目标

.PHONY:clean

clean:rm -rf hello main.c func1.o func2.o

#伪命令的使用:

[root@makefile] make clean

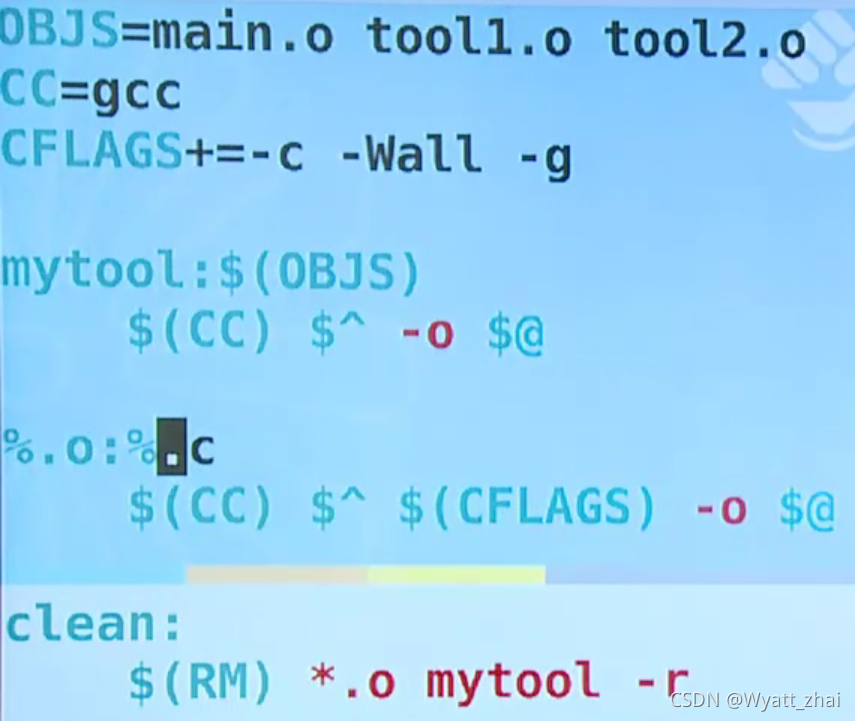

3.makefile 的变量

变量类似C语言里面的宏定义

变量分为:用户自定义变量,自动变量,预定义变量,环境变量

1.自定义变量:

1.定义变量格式:变量名 = 变量值 #最基本的赋值方式变量名 := 变量值 #覆盖之前的值,与=相似,效果更好,常用变量名 ?= 变量值 #若没有则赋值,有则保留原来的(不执行当前赋值)变量名 += 变量值 #在原来的基础添加

2.如何引用变量:$(变量名)=?? //给变量赋值??=$(变量名) //引用变量

.PHONY:com sim cleanOUTPUT = adder_topVCS = vcs -sverilog +v2k -timescale=1ns/1ns \-debug_all \-o ${OUTPUT} \-l compile.log \SIM = ./${OUTPUT} -l run.logcom:${VCS} -f verilog_file.fsim:${SIM}clean:rm -rf ./csrc *.daidir *.log simv* *.key

2.自动变量

4.其他

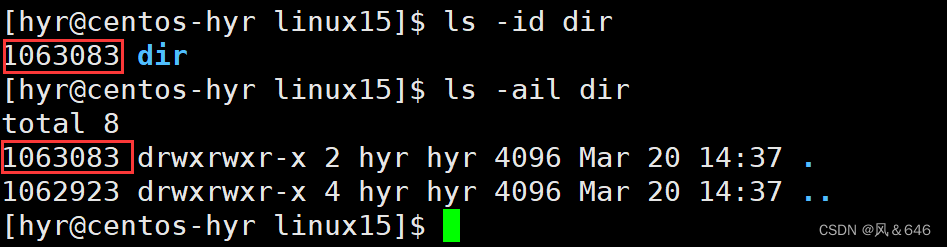

1.把生成的目标存放到其他的文件夹里面

DIR := ./debug/

$(DIR)test:$(DIR)test.o $(DIR)sequence.ogcc -o $(DIR)test.o $(DIR)sequence.o

2.makfile里面的注释使用#

3.命令如果不想显示到终端,在命令前加@

4.如果你命名的makefile文档名并非makefile,那么就要加上**-f**

[root@makefile]# make -f Makefile1

参考:

https://www.bilibili.com/video/BV1dW411n7vk?spm_id_from=333.999.0.0

跟我一起写Makefile——陈皓

![[转载]复旦女博士于娟——为啥是我得癌症? (转)](http://simg.sinajs.cn/blog7style/images/common/sg_trans.gif)