ZYNQ 是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。与传统 SoC解决方案不同的是,高度灵活的可编程逻辑(FPGA)可以实现系统的优化和差异化,允许添加定制外设与加速器,从而适应各种广泛的应用。

Zynq-7000 系列是 Xilinx 于 2010 年 4 月推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。这款基于 ARM 处理器的 SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力等要求。

ZYNQ 的本质特征,是它组合了一个双核 ARM Cortex-A9 处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件。由于该新型器件的可编程逻辑部分基于赛灵思 28nm 工艺的 7 系列 FPGA,因此该系列产品的名称中添加了“7000”,以保持与 7 系列 FPGA 的一致性,同时也方便日后本系列新产品的命名。

ZYNQ 的全称是 Zynq-7000 All Programmable SoC,也就是说,ZYNQ 实际上是一个片上系统(System on

Chip,SoC)。那么,什么是“SoC”?

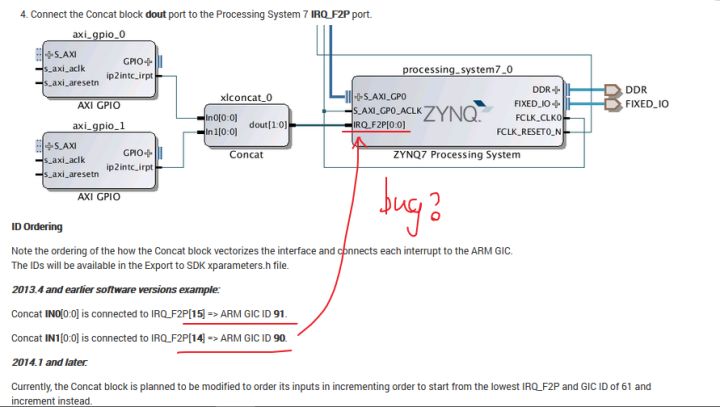

一个能够实现一定功能的电路系统由多个模块构成,如处理器、接口、存储器、模数转换器等等。这些功能模块可以由分立的器件来实现,然后在印刷电路板(PCB)上组合起来,最终形成板上系统(System-on-a-Board)。板上系统的示意图如下所示:

在上图所示的板上系统中,绿色的矩形代表印刷电路板(PCB),上面各种颜色的小矩形代表了系统中各个功能模块,如存储器等。这些模块的功能都由一个个独立的硅芯片分别实现的,它们之间通过 PCB 上 的金属走线连接,最终构成一个完整的系统。

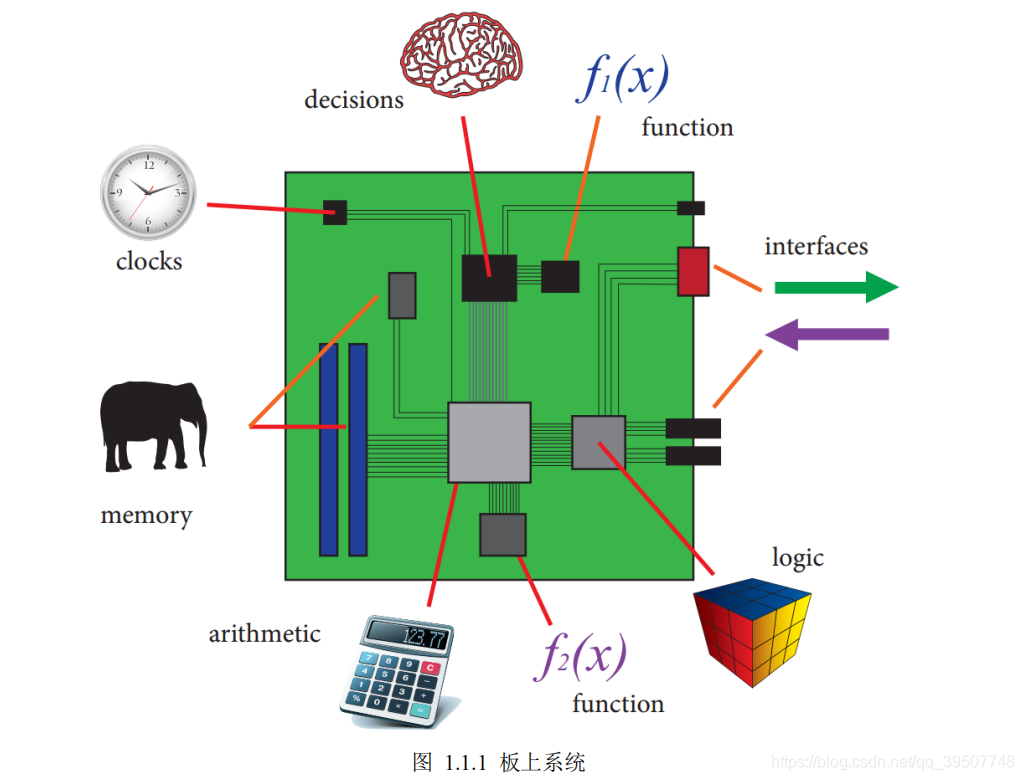

而片上系统(System-on-Chip)指的是在单个硅芯片就可以实现整个系统的功能,其示意图如下所示:

如上图所示,片上系统 SoC 在一个芯片里就实现了存储、处理、逻辑和接口等各个功能模块,而不是像板上系统那样,需要用几个不同的物理芯片来实现。与板上系统相比,SoC 的解决方案成本更低,能在不同的系统单元之间实现更快更安全的数据传输,具有更高的整体系统速度、更低的功耗、更小的物理尺寸和更好的可靠性。

在过去,SoC 这个术语常用于指专用集成电路 (Application Specific Integrated Circuit,ASIC) 。基于 ASIC的 SoC 的代表性例子包括在 PC、平板和智能手机上使用的处理器,如华为旗舰手机中的麒麟系列芯片。这些处理器典型地是由至少两个处理器核、存储器、图形处理器、接口和其他功能模块组合起来的。基于 ASIC的 SoC 的主要缺点有两个:

1、开发周期长且成本巨大;

2、缺乏灵活性。

开发 ASIC 时不可重用的工程投入是巨大的,使得这种 SoC 类型只适合于大批量而且寿命有限的产品中。

ASIC SoC 的局限性导致它们不适用于很多应用,特别是当快速投入市场能力、灵活性和升级能力已经成为重要的关键因素。对于小批量或中批量的产品,ASIC SoC 也不是好的解决方案。

可编程片上系统(SOPC,System-on-Progammable-Chip) 为上述应用提供了一个更灵活的解决方案:一种在可编程、可重新配置的芯片上实现的 SoC。其中,可编程的芯片指的就是 FPGA。FPGA 天生的灵活性使其可以被随心所欲地重新配置,以实现不同系统的功能,包括嵌入式处理器。和使用 ASIC 来实现 SoC相比,FPGA 能构成更为基础灵活的平台,方便系统的升级。

相比于 SOPC,ZYNQ 为实现灵活的 SoC 提供了一个更加理想的平台:Xilinx 将其打造成 “全可编程片上系统(APSoC,All-Programmable SoC)” 。它将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

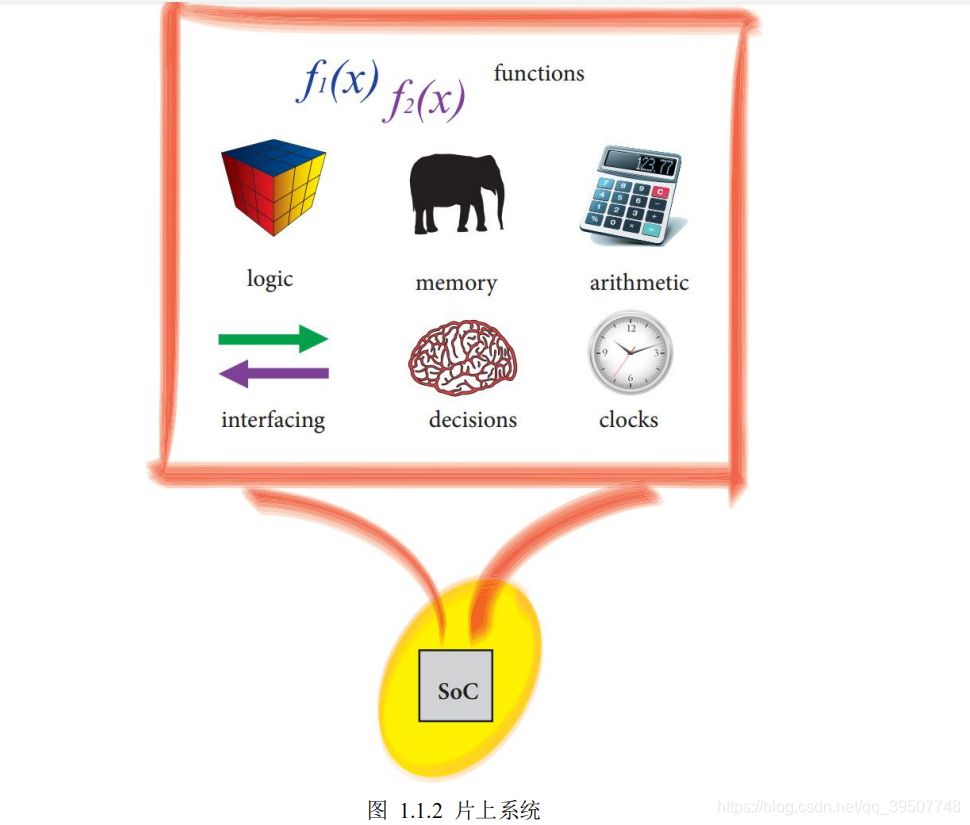

ZYNQ 是由两个主要部分组成的:一个由双核 ARM Cortex-A9 为核心构成的处理系统(PS,Processing System),和一个等价于一片 FPGA 的可编程逻辑(PL,Programmable Logic)部分。ZYNQ 架构的简化模型如下图所示:

在上图中,PS 具有固定的架构,包含了处理器和系统的存储器;而 PL 完全是灵活的,给了设计者一块“空白画布”来创建定制的外设。

在 ZYNQ 上,ARM Cortex-A9 是一个应用级的处理器,能运行像 Linux 这样的操作系统,而可编程逻辑是基于 Xilinx 7 系列的 FPGA 架构。

ZYNQ 架构实现了工业标准的 AXI 接口,在芯片的两个部分之间实现了高带宽、低延迟的连接。这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会产生在两个分立器件之间的接口开销。与此同时,又能获得系统被简化为单一芯片所带来的好处,包括物理尺寸和整体成本的降低。