目录

一、ZYNQ简介

二、vivado工程

①创建工程

②添加设计文件

③生产顶层HDL模块

④生成 Bitstream 文件并导

三、vitis工程

①启动vitis

②创建工程

③编译与下载

一、ZYNQ简介

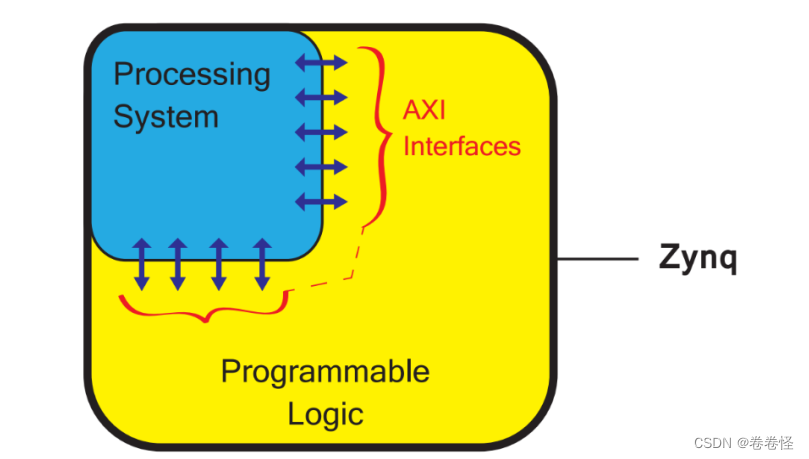

ZYNQ 是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。与传统SoC 解决方案不同的是,高度灵活的可编程逻辑(FPGA)可以实现系统的优化和差异化,允许添加定制外设与加速器,从而适应各种广泛的应用。

ZYNQ芯片总统框图:

ZYNQ 是由两个主要部分组成的:一个由双核 ARM Cortex-A9 为核心构成的处理系统(PS,

Processing System)和FPGA 的可编程逻辑(PL, Programmable Logic)部分。

ZYNQ 架构的简化模型如上图所示。

PS 具有固定的架构,包含了处理器和系统的存储器;PL 是灵活的,由使用者定制外设。

这里记录一下vivado和vitsi软件的使用过程。

二、vivado工程

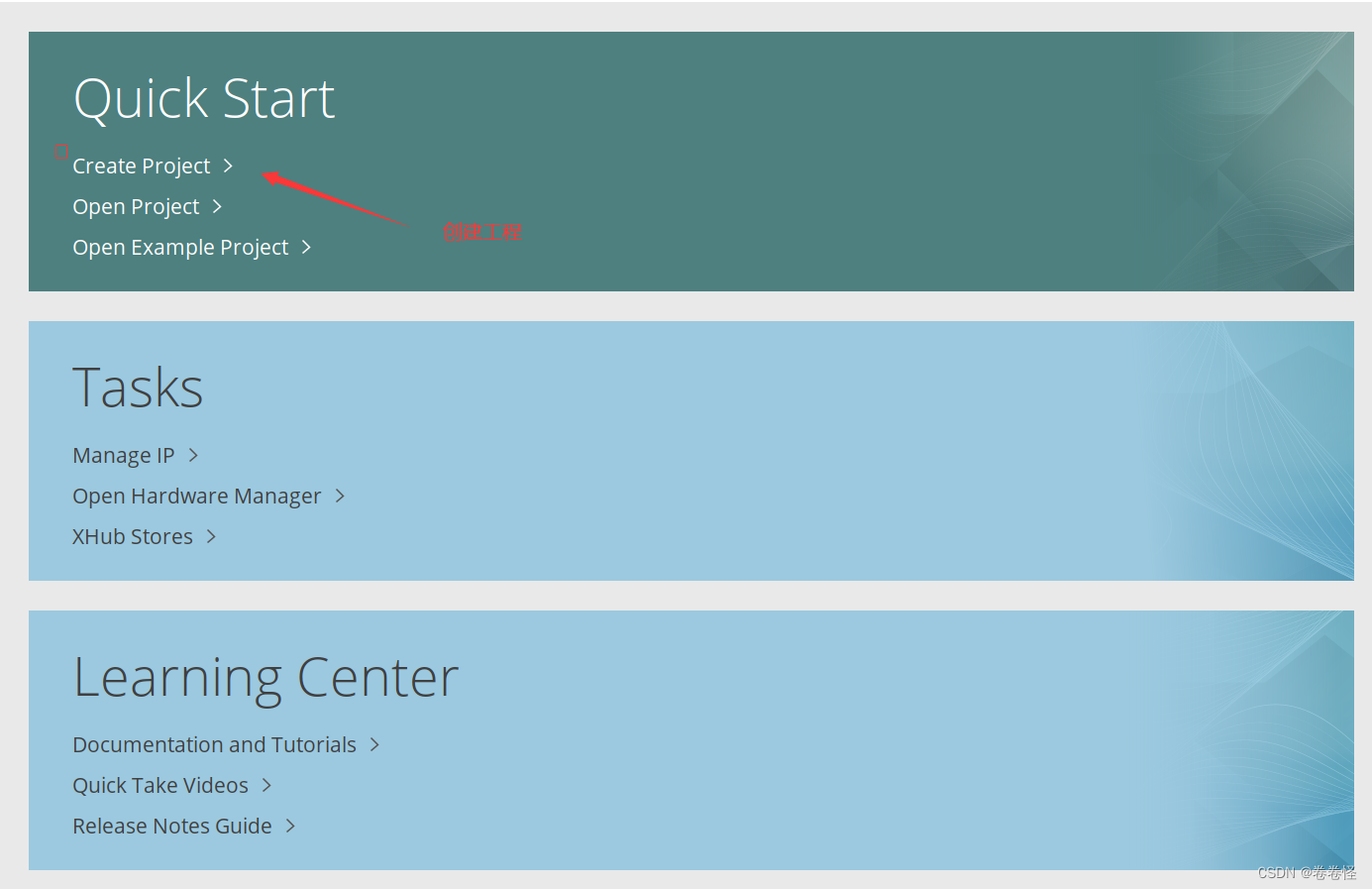

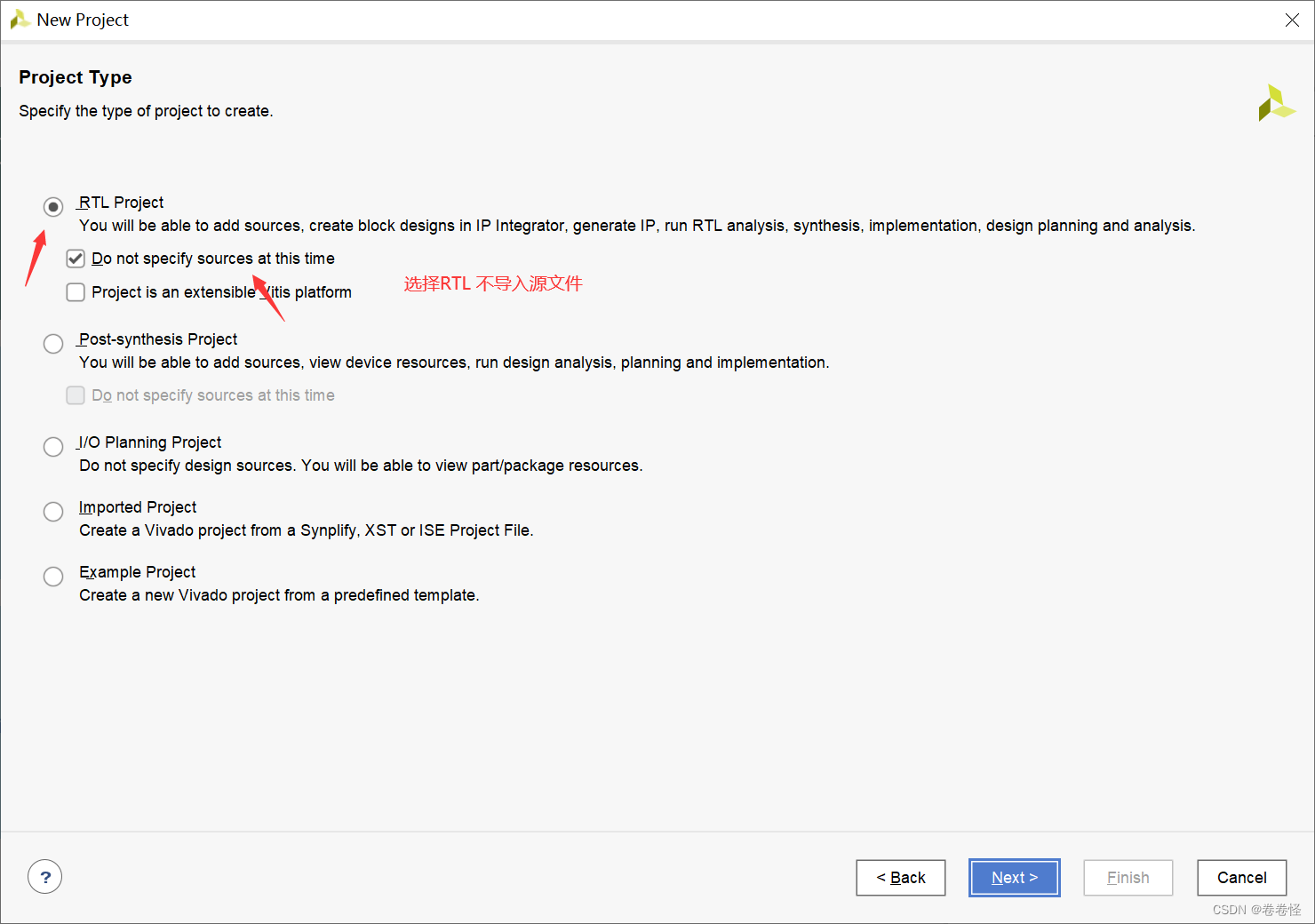

①创建工程

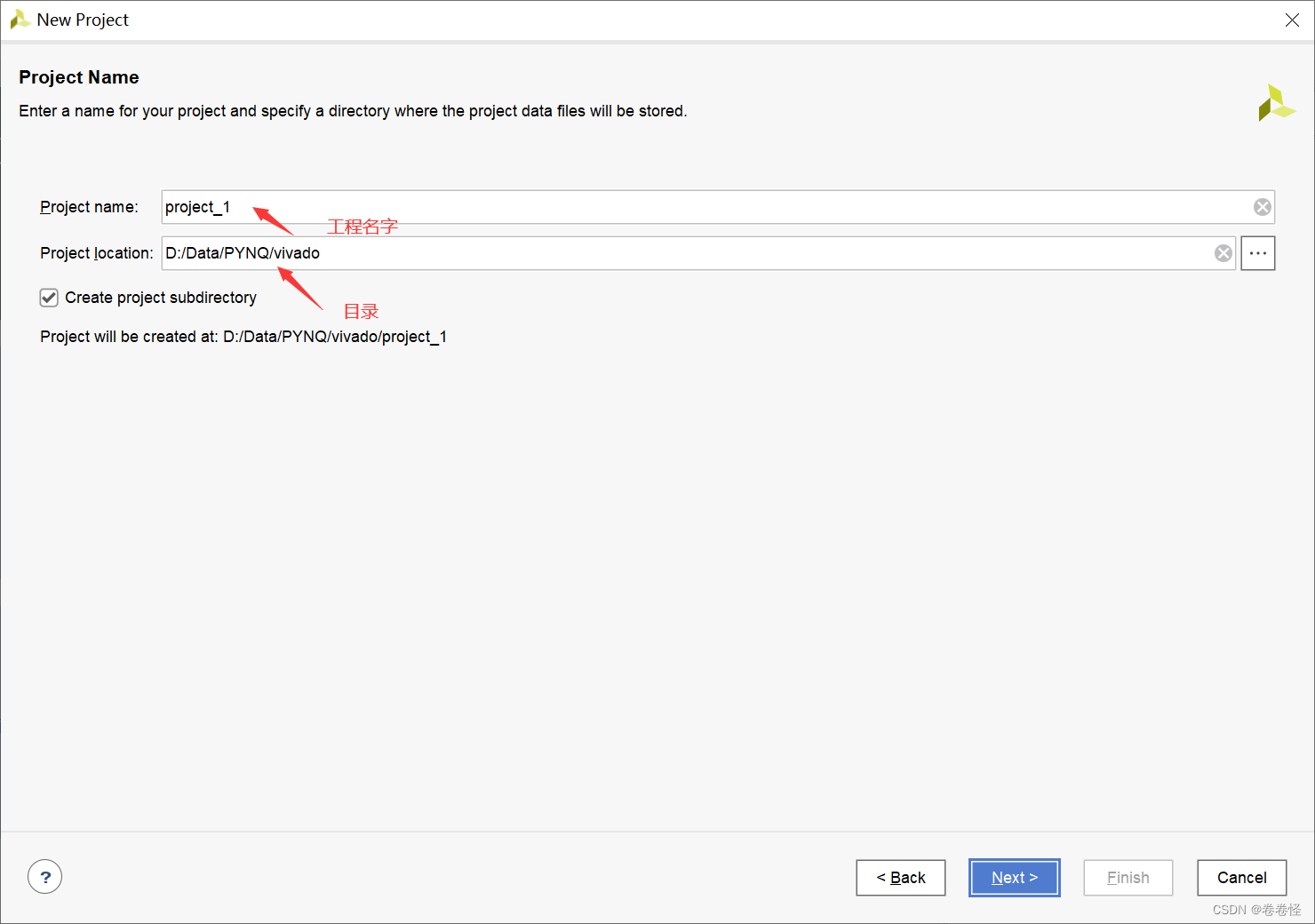

进入到工程名字创建和位置指定

选择开发板型号

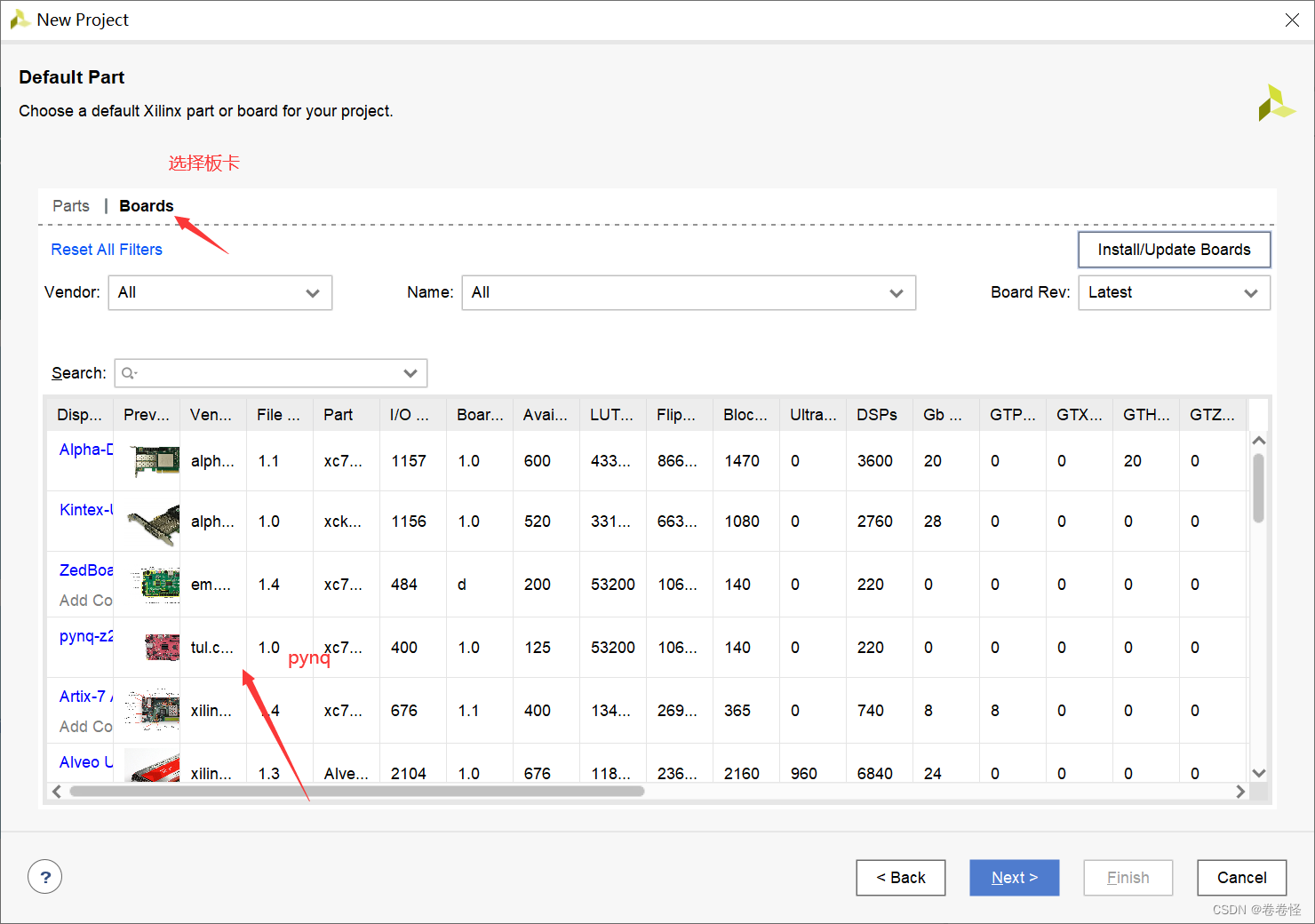

创建成功后,来到主界面

Vivado 工程主界面中的主要子窗口:

①Flow Navigator:Flow Navigator 提供对命令和工具的访问,其包含从设计输入到生成比特流的整个过程。 在点击了相应的命令时,整个 Vivado 工程主界面的各个子窗口可能会作出相应的更改。

②数据窗口区域:这个区域显示的是设计源文件和数据相关的信息

• Sources 窗口: 显示层次结构(Hierarchy)、 IP 源文件(IP Sources)、库(Libraries)和编译顺序(Compile Order)的视图。

• Netlist 窗口: 提供分析后的(elaborated)或综合后的(synthesized)逻辑设计的分层视图。③Properties 窗口: 显示有关所选逻辑对象或器件资源的特性信息

④工作空间(Workspace): 工作区显示了具有图形界面的窗口和需要更多屏幕空间的窗口,包括:

• Project Summary。提供了当前工程的摘要信息,它在运行设计命令时动态地更新。

• 用于显示和编辑基于文本的文件和报告的 Text Editor。

• 原理图(Schematic)窗口。

• 器件(Device)窗口。

• 封装(Package)窗口。⑤结果窗口区域:在 Vivado 中所运行的命令的状态和结果,显示在结果窗口区域中,这是一组子窗口的集合。在运行命令、生成消息、创建日志文件和报告文件时,相关信息将显示在此区域。

• Tcl Console: 允许您输入 Tcl 命令,并查看以前的命令和输出的历史记录

• Messages: 显示当前设计的所有消息,按进程和严重性分类,包括“Error”、“Critical

Warning”、“Warning”

• Log: 显示由综合、实现和仿真 run 创建的日志文件。

• Reports: 提供对整个设计流程中的活动 run 所生成的报告的快速访问。

• Designs Runs: 管理当前工程的 runs。⑥主工具栏: 主工具栏提供了对 Vivado中最常用命令的单击访问

⑦主菜单: 主菜单栏提供对 Vivado命令的访问

⑧窗口布局(Layout)选择器: Vivado 提供预定义的窗口布局,以方便设计过程中的各种任务。布局选择器使您能够轻松地更改窗口布局

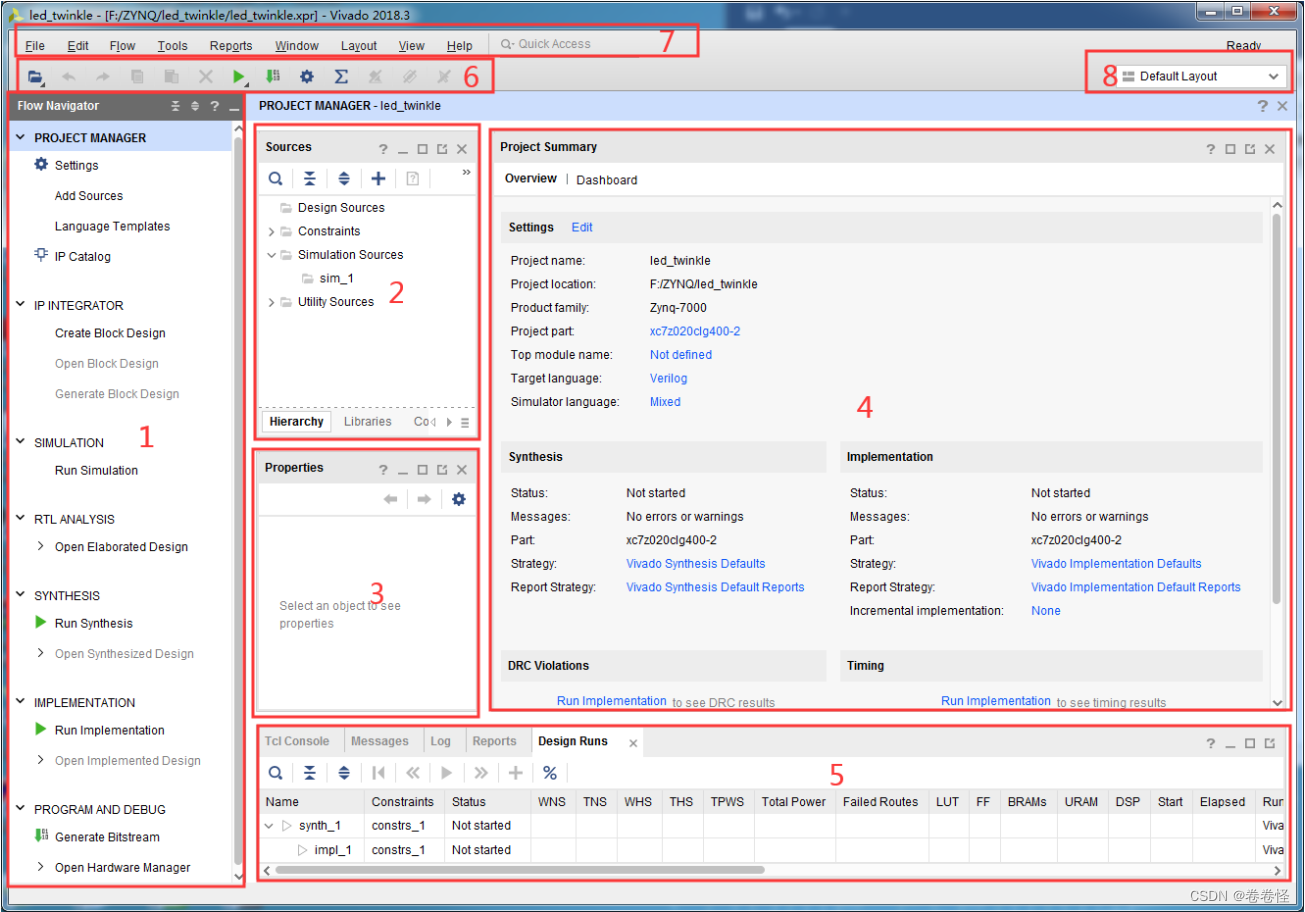

②添加设计文件

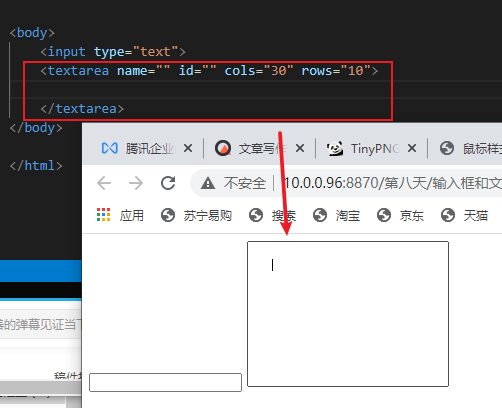

点击 Create Block Design,创建一个Block设计。名字可以不用改。

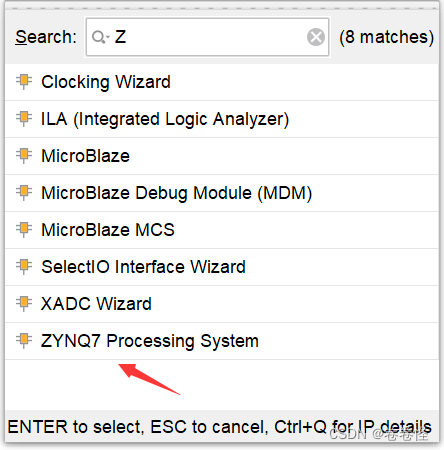

然后点击add IP图标,添加IP核

搜索zynq,在搜索结果列表中双击“ ZYNQ7 Processing System”

出现如下图:

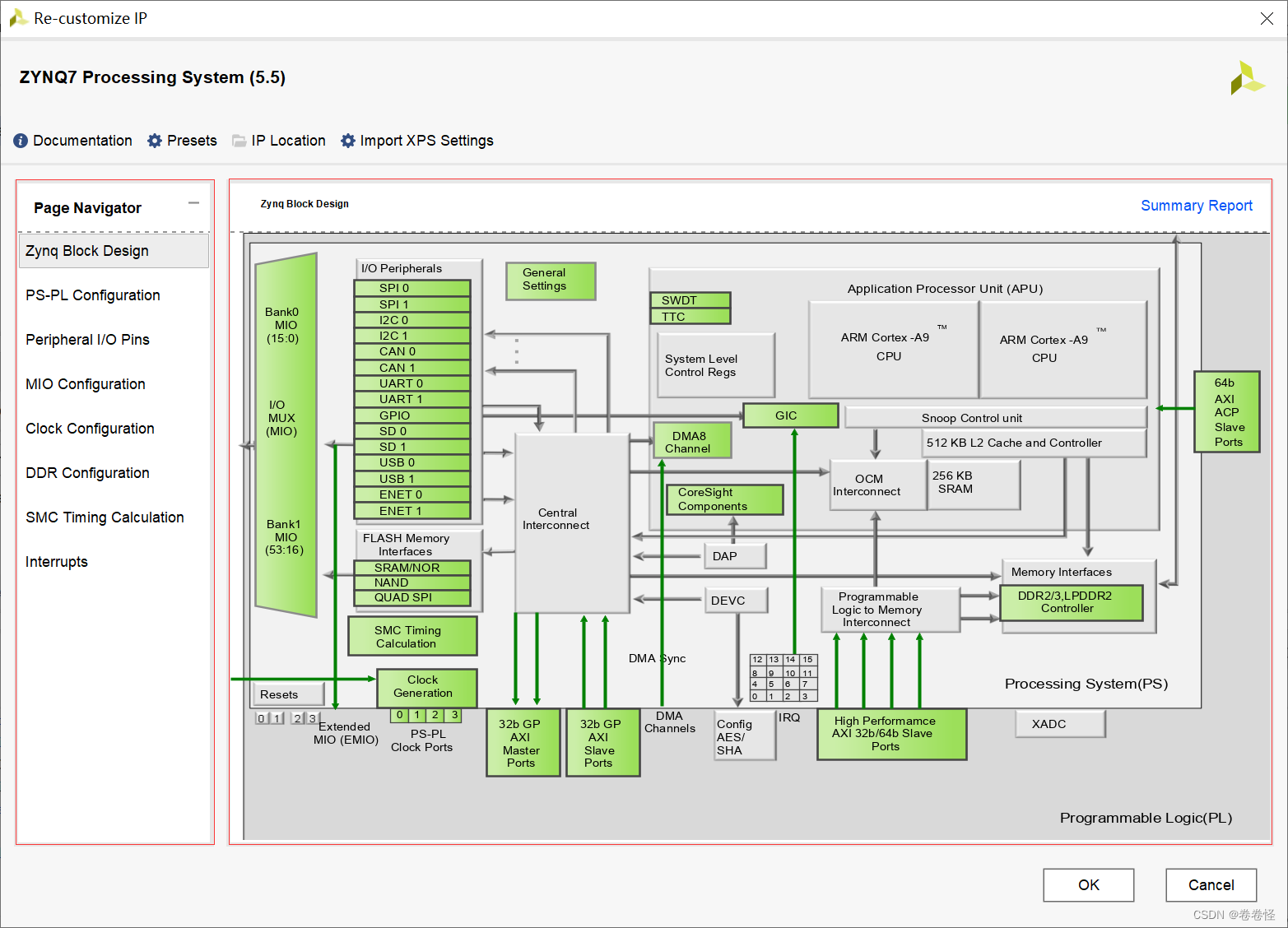

可以双击processing_system7_0 ZYNQ7 Processing,配置相关参数,如下图

在 Zynq Block Design 页面,显示了 Zynq 处理系统( PS)的各种可配置块,其中灰色部分是固定的,绿色部分是可配置的,按工程实际需求配置。可以直接单击各种可配置块(以绿色突出显示)进入相应的配置页面进行配置,也可以选择左侧的页导航面板进行系统配置。

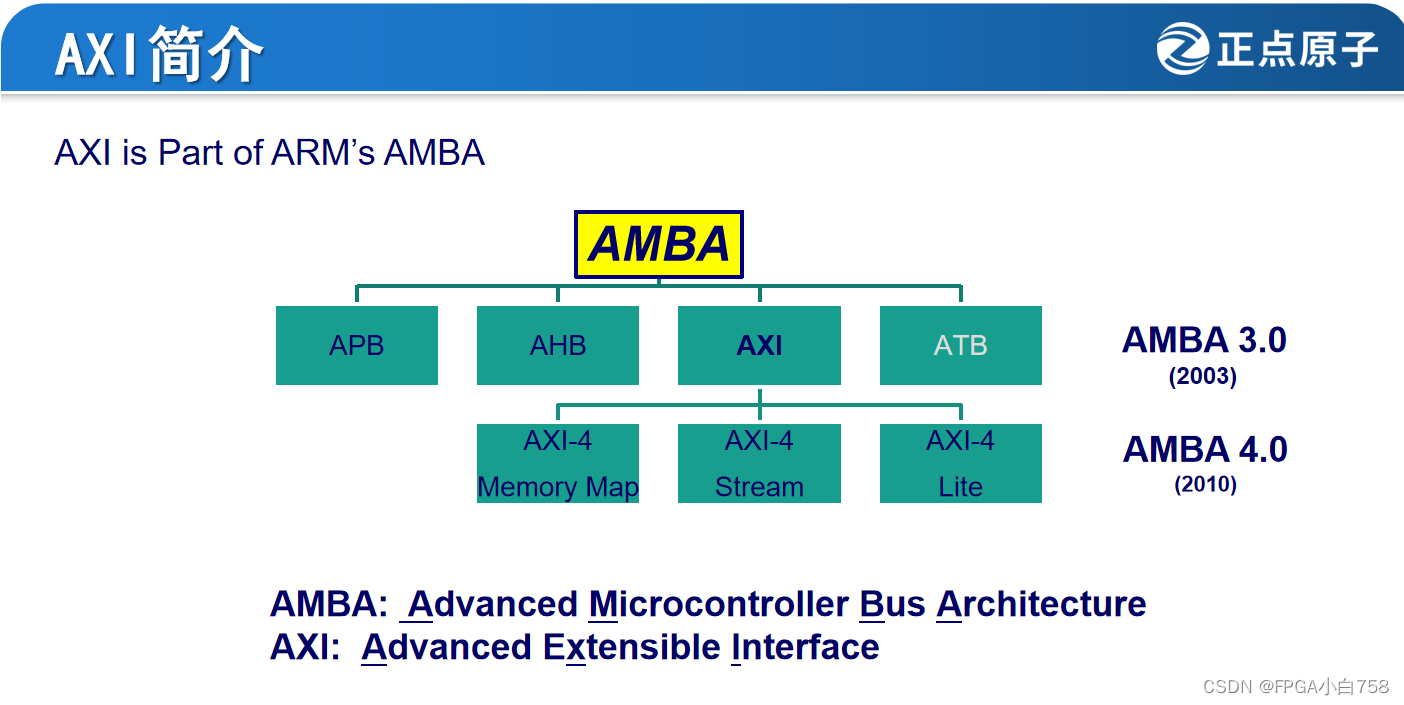

PS-PL Configuration:配置 PS-PL 接口,包括 AXI、 HP 和 ACP 总线接口

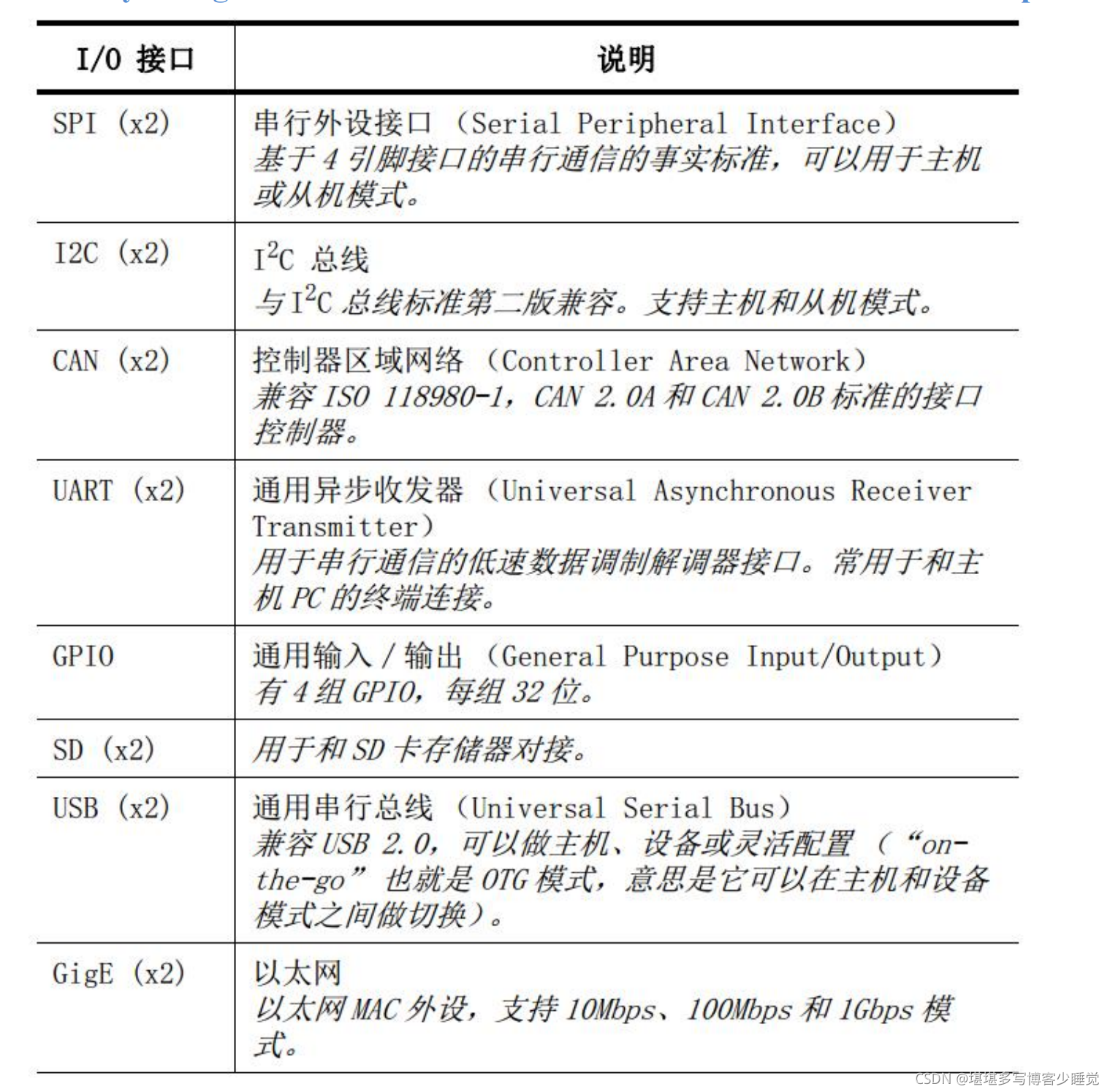

Peripheral IO Pins:为不同的 I/O 外设选择 MIO/EMIO 配置

MIO Configuration :为不同的 I/O 外设具体配置 MIO/EMIO

Clock Configuration :配置 PS 输入时钟、外设时钟,以及 DDR 和 CPU 时钟

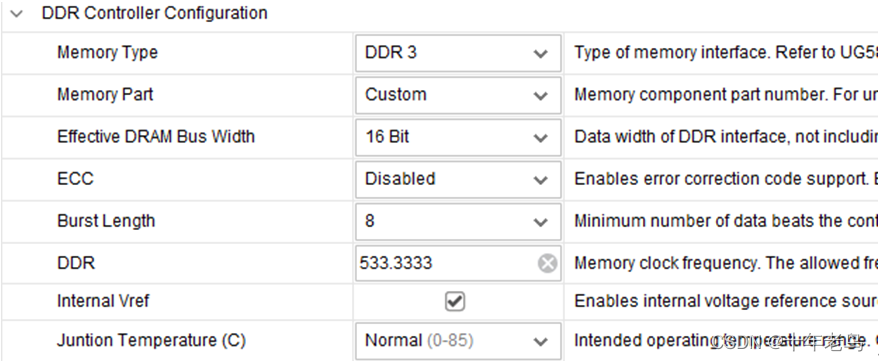

DDR Configuration :设置 DDR 控制器配置信息

SMC Timing Calculation :于执行 SMC 时序计算

Interrupts :配置 PS-PL 中断端口。

本次使用基本上不用设置,点击ok退出。

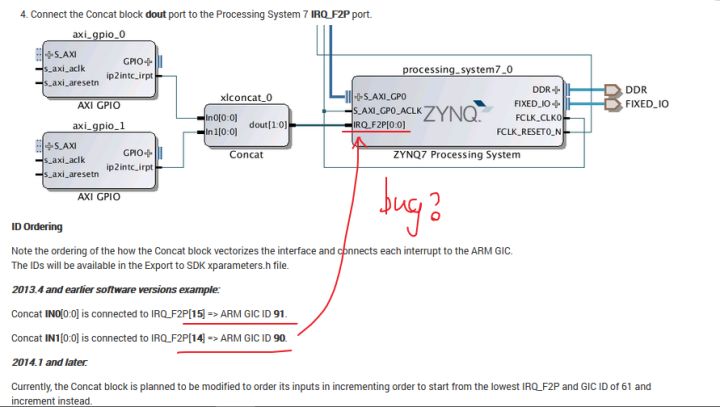

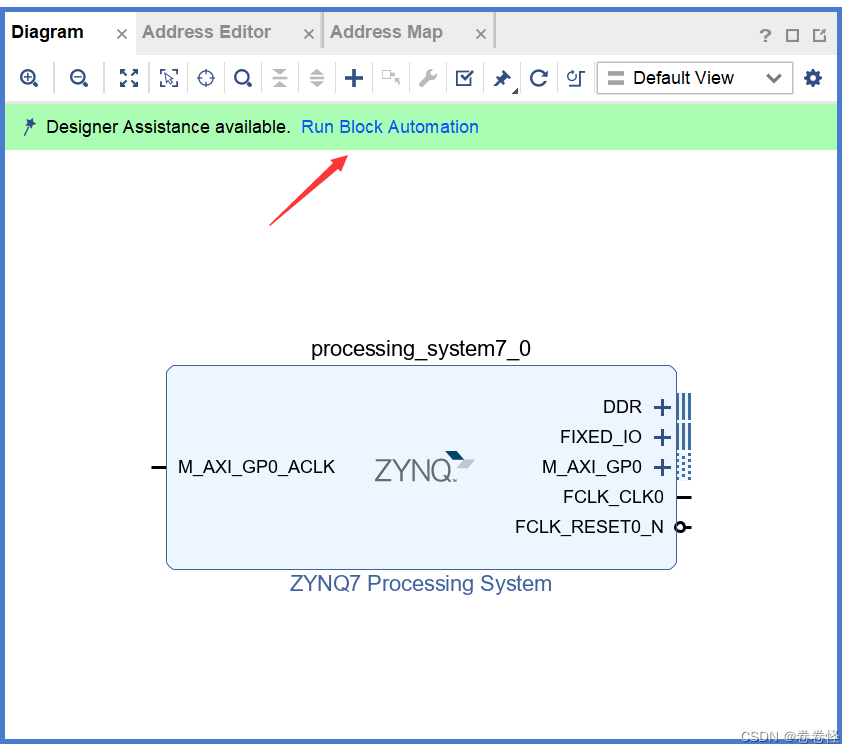

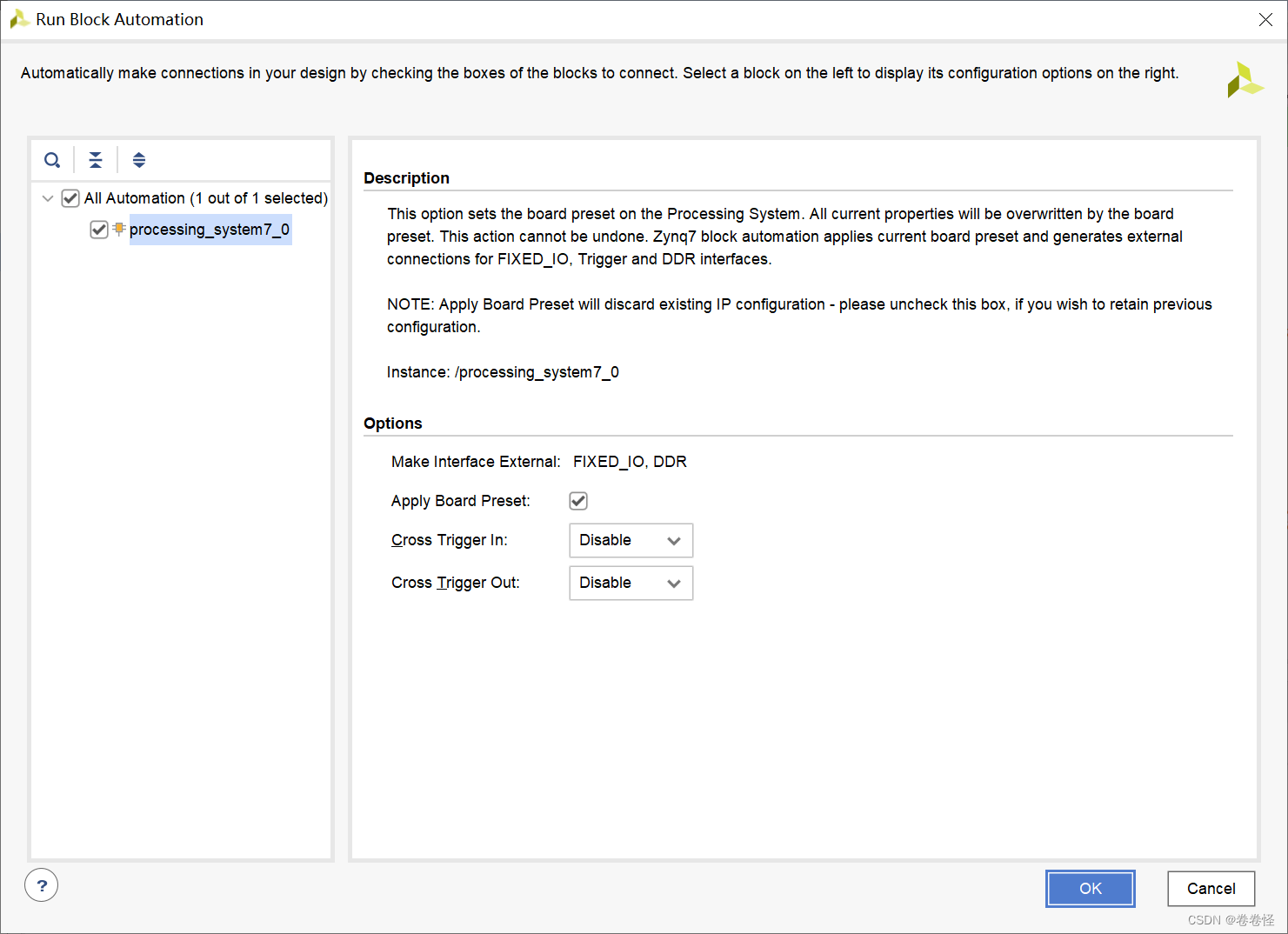

点击上图中箭头所指示的位置“Run Block Automation”,会弹出如下图所示的对话框

在该界面中可以选择自动连接 IP 模块的接口, 包括导出外部端口,甚至可以自动添加模块互联过

程中所需的 IP。 本次设计中只有一个 IP 模块, 在左侧确认勾选 processing_system7_0,然后点击“ OK”。

将FCLK_CLK0和M_AXI_GPO_ACLK连接起来。

部分接口介绍:

M_AXI_GP0:通用( General Purpose) AXI 接口,它包含了一组信号。 首字母 M 表示 PS 作为主机( Master), PL 中的外设作为从机( Slave)

M_AXI_GP0_ACLK :是M_AXI_GP0全局时钟信号,它是一个输入信号, M_AXI_GP0 接口的所有信号都是在这个全局时钟的上升沿采样的

FCLK_CLK0 :PS 输出的时钟信号, 它将作为 PL 中外设模块的时钟源。 这个时钟由 PS 中的 IO PLL产生, 频率范围可以从 0.1 到 250MHz, 在配置 ZYNQ7 PS 的时候, 该时钟默认为 50MHz。

FCLK_RESET0_N :由 PS 输出到 PL 的全局复位信号,低电平有效。

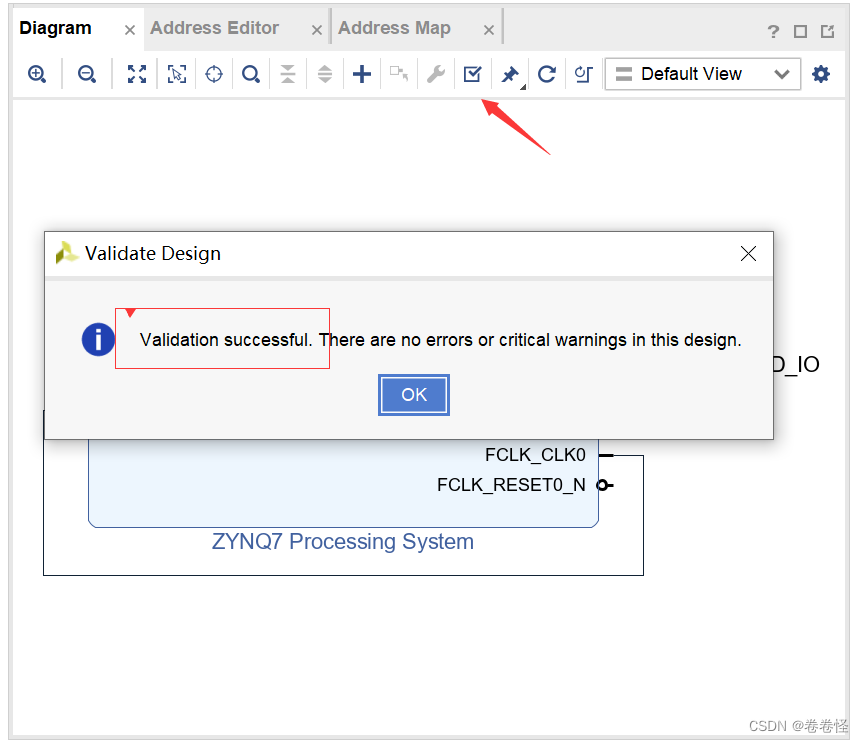

按快捷键 Ctrl+S 保存当前设计,验证当前设计。

如果验证结果报出错误或者警告,大家需要重新检查自己的设计。

如果验证结果报出错误或者警告,大家需要重新检查自己的设计。

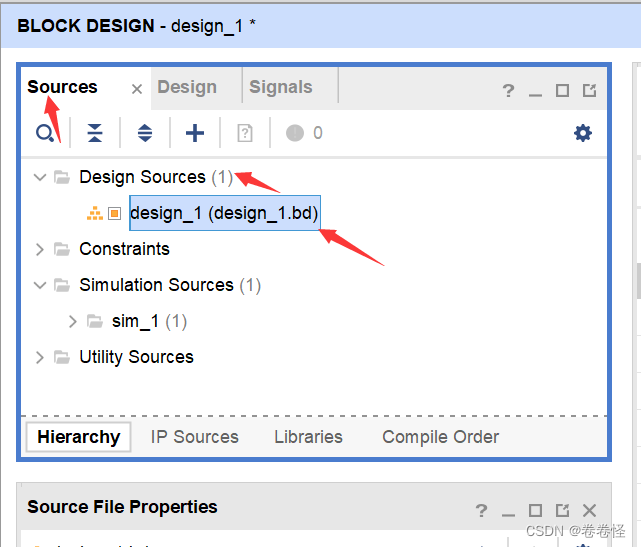

③生产顶层HDL模块

在 Sources 窗口中,选中 Design Sources 下的 .bd文件, 这就是刚刚完成的 Block Design 设计。

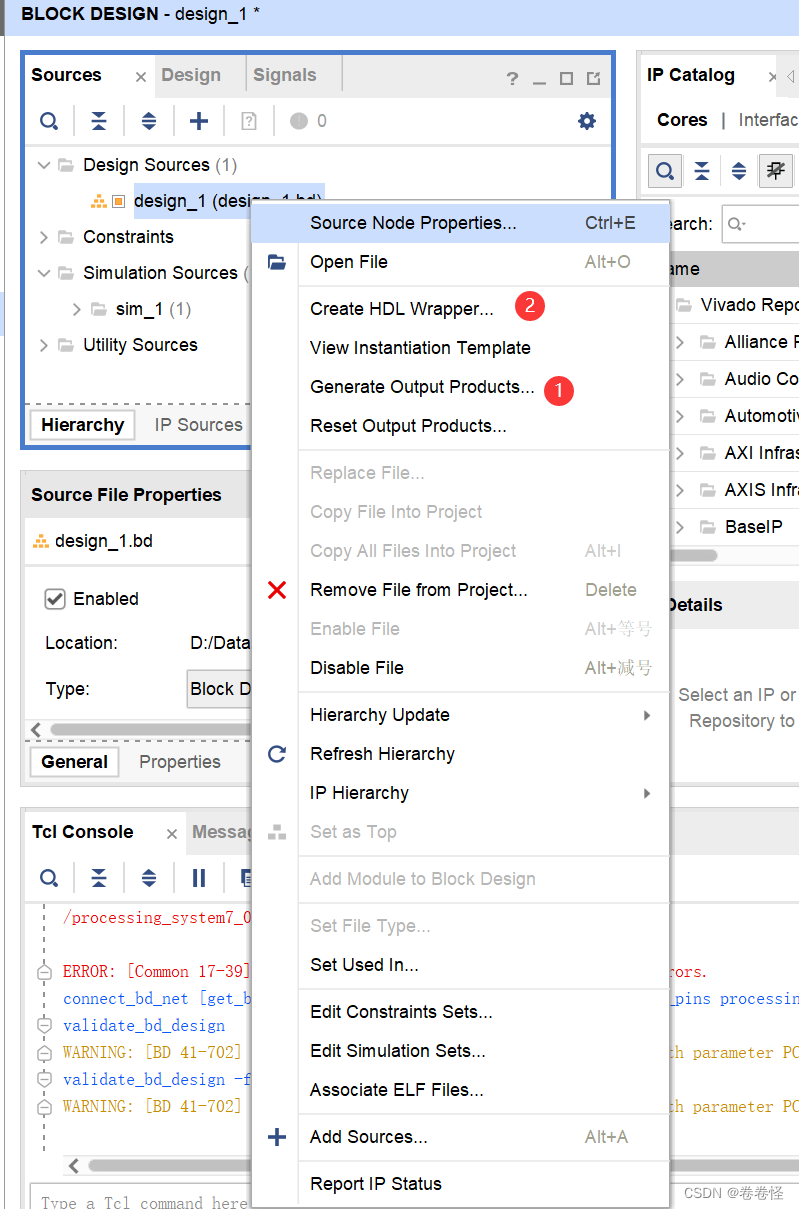

依次点击如下执行

在对话框中 Synthesis Options 选择 Global; Run Setings 用于设置生成过程中要使用的处理器的线程数,进行多线程处理, 保持默认或设置为个人电脑处理器最大可使用线程数都可以,一般选择最大可使用线程数的一般。然后点击“Generate”来生成设计的综合、实现和仿真文件。

在“ Generate”过程中会为设计生成所有需要的输出结果。 比如 Vivado 工具会自动生成处理系统的 XDC约束文件,因此不需要手动对 ZYNQ PS 引出的接口( DDR 和 FIXED_IO) 进行管脚分配。

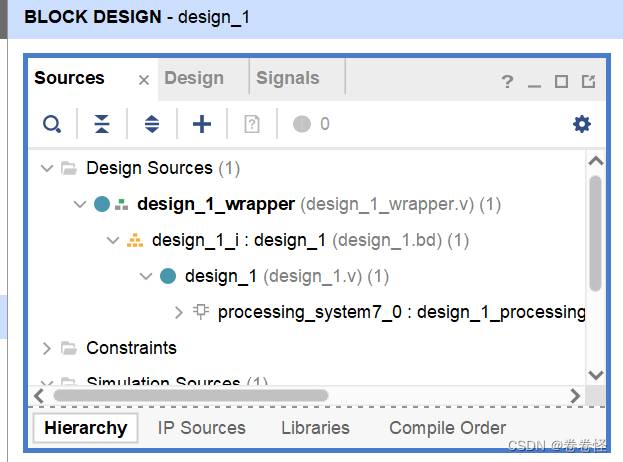

然后选择“Create HDL Wrapper”,在弹出的对话框中确认勾选“ Let Vivado manage wrapper and auto-update”, 然后点击“ OK”。如下图

.v 为创建的 Verilog 文件,当前模块为顶层模块。 该模块使用 Verilog HDL 对设计进行封装, 主要完成了对 block design 的例化。勾选了“ Let Vivado manage wrapper and auto-update”, 在修改了 Block Design 之后就不需要再重新生成顶层模块, Vivado 工具会自动更新该文件。

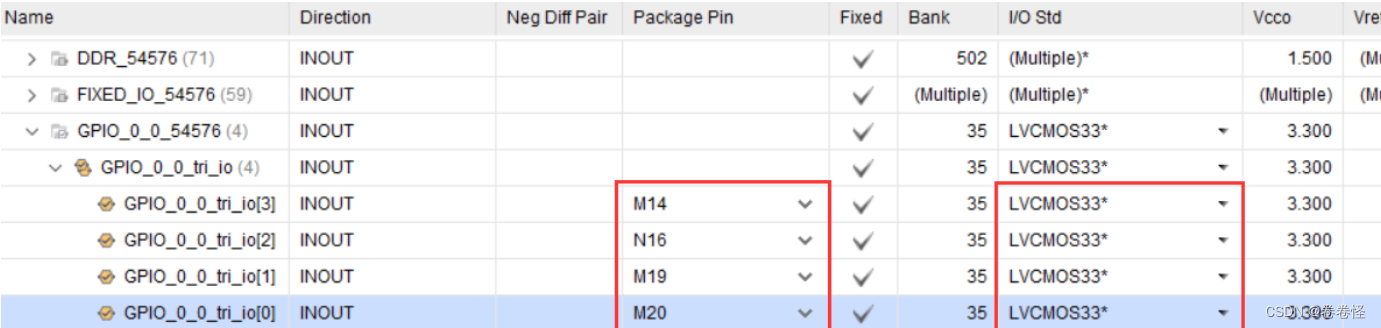

注意:若使用了PL的资源,比如说一些引脚,需要配置EMIO,并且为EMIO分配引脚,添加约束文件。对引脚进行约束配置:

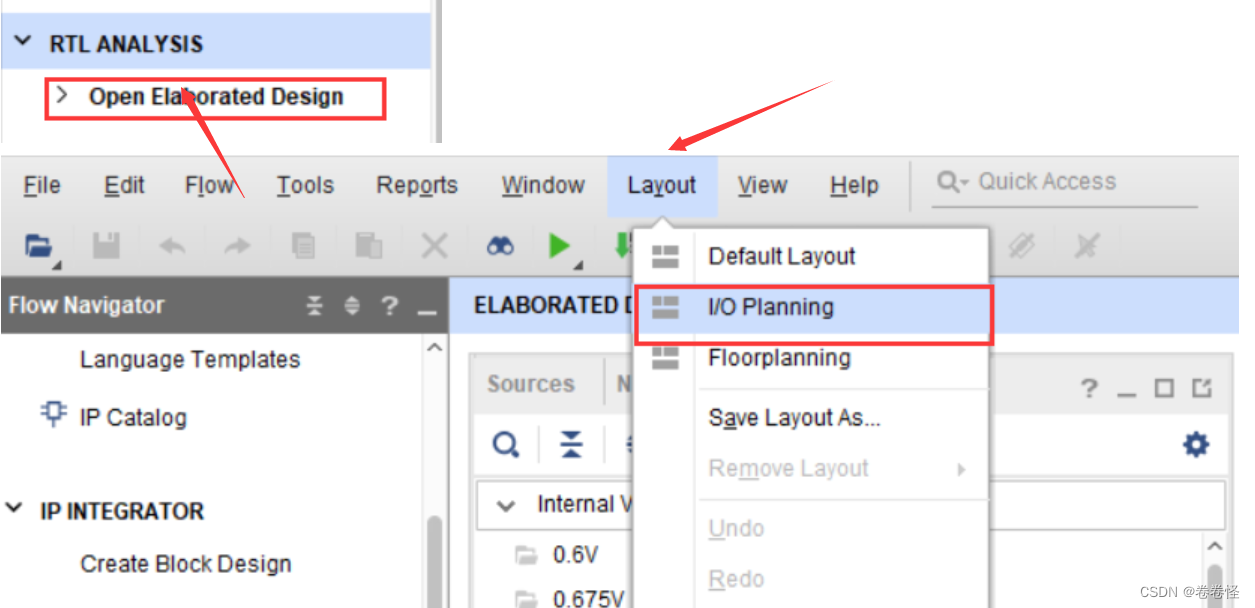

点击”Flow Navigator“窗口中的”Open Elaborated Design“按钮,会先进行分析与综合。Vivado会编译RTL源文件进行全面的语法检查,并且给出相应的Error和Warning。打开分析后(Elaborated)的设计后,Vivado会生成顶层原理图视图,并在默认view layout中显示设计。

根据自己开发板设置引脚编号和电平(此处也需要结合原理图确定)。设置完成后点击保存,并自行输入管脚约束文件的文件名。之后会记录相关笔记。对应本次实验来说不需要操作这里。

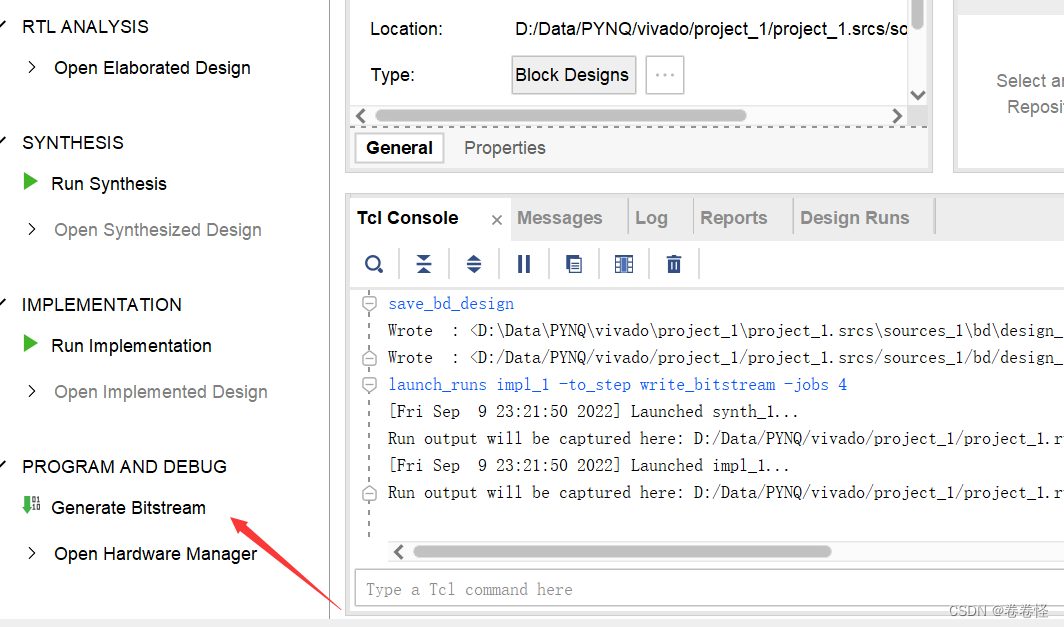

④生成 Bitstream 文件并导

如果设计中使用了 PL 的资源,则需要添加引脚约束并对该设计进行综合、实现并生成 Bitstream 文件。

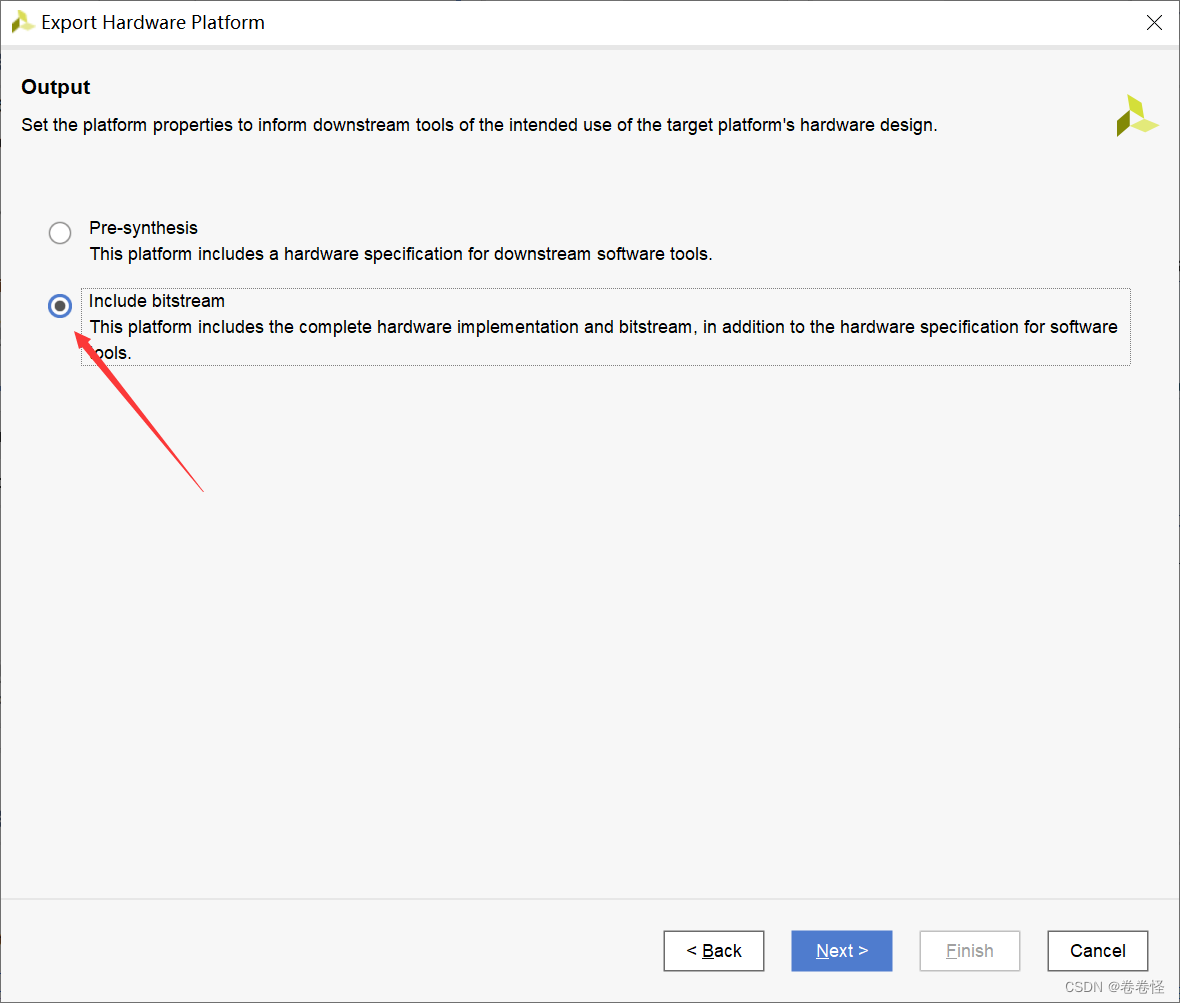

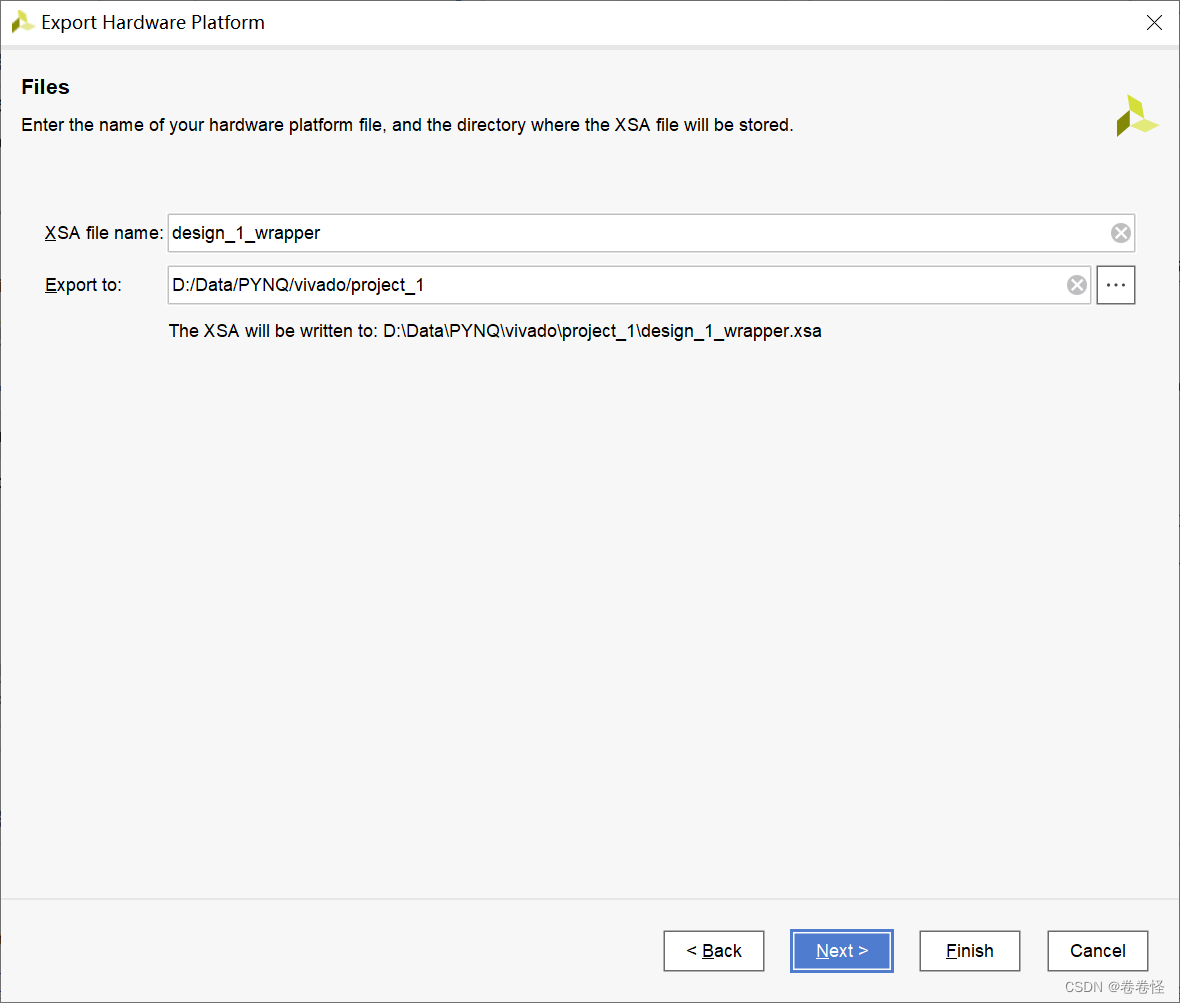

在菜单栏选择 File > Export > Export hardware

在弹出的对话框中,因为没有生成 bitstream 文件,所以无需勾选“ Include bitstream”,直接点击“ OK”按钮。

选择保存路径和名字,在 Export Hardware 的过程中, 工具会将硬件以一个 ZIP 压缩文件的形式导出到该工作空间中。

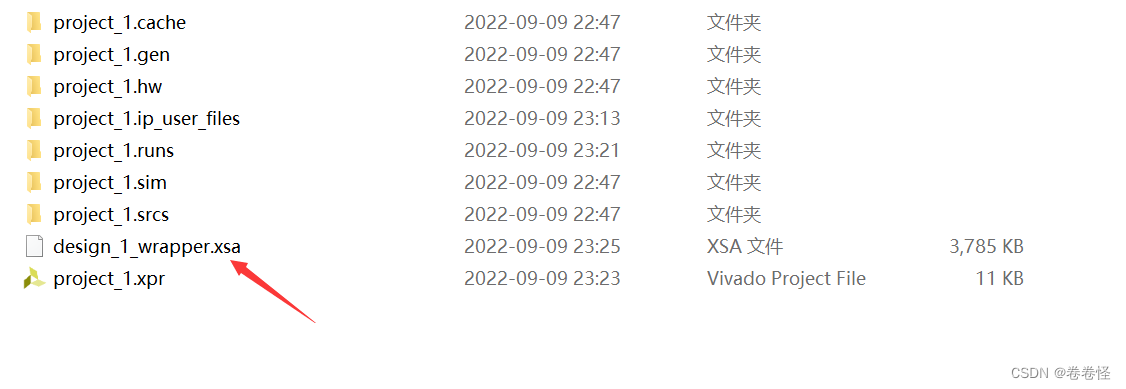

导出后,工程目录下会出现如下压缩包。

三、vitis工程

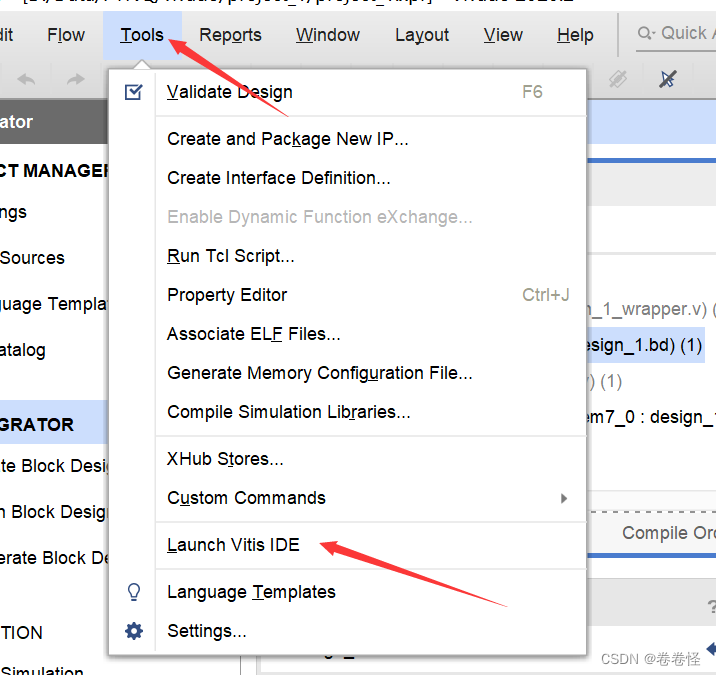

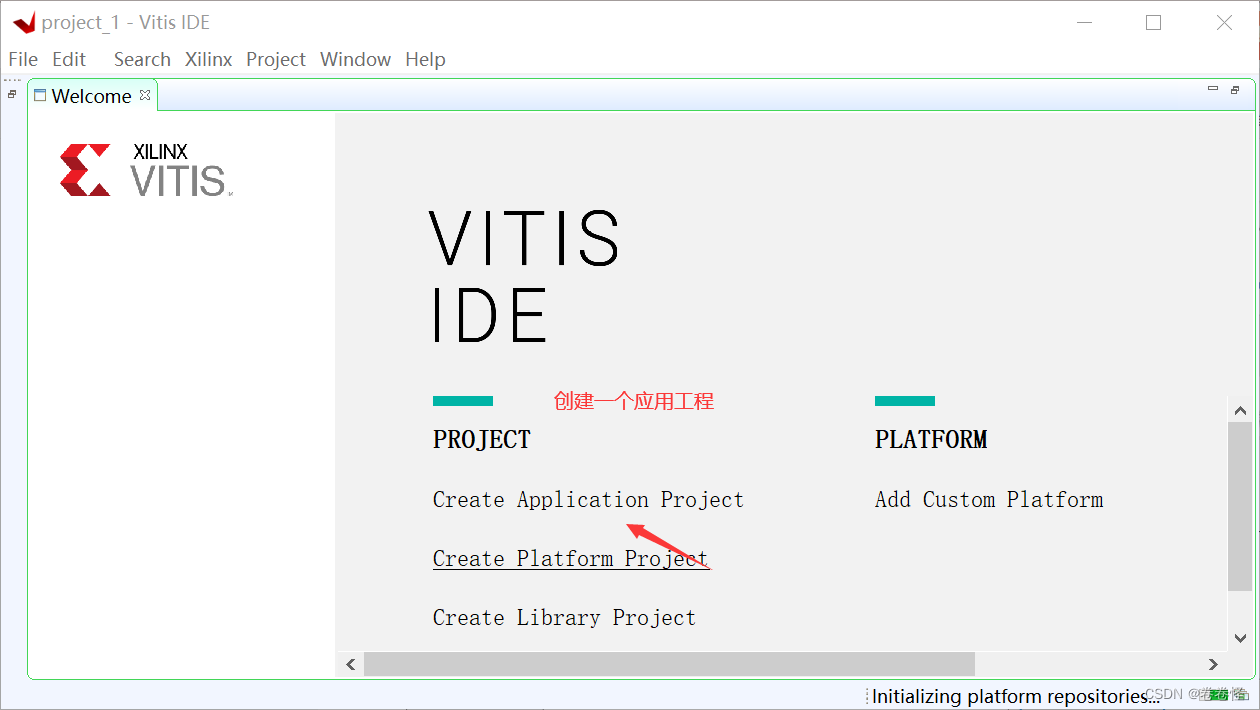

①启动vitis

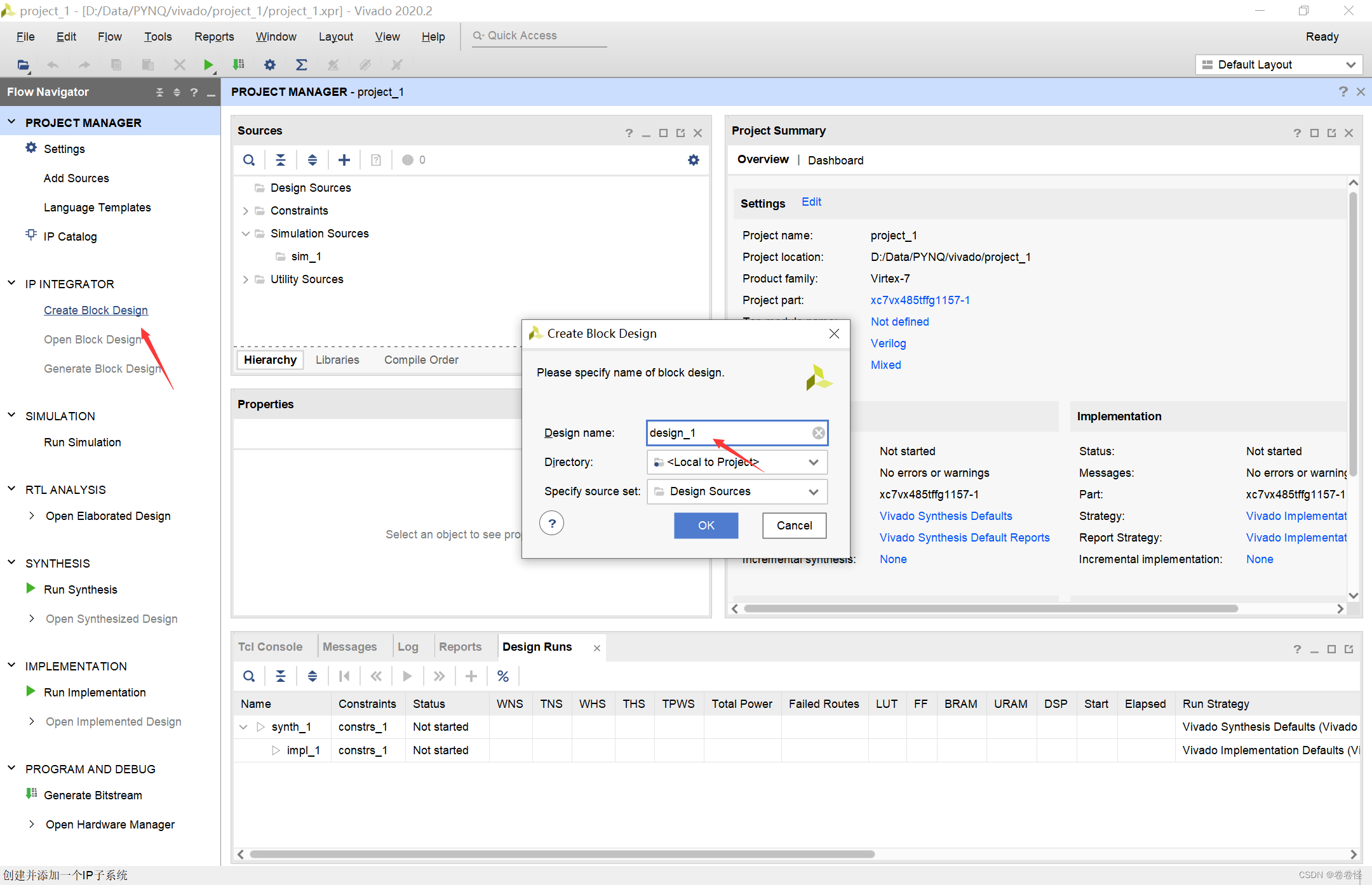

②创建工程

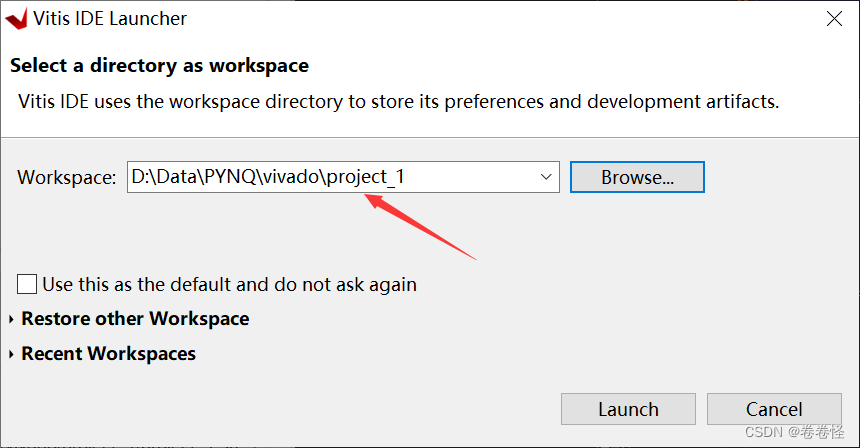

选择vivado工程目录

创建工程

选择刚刚那个xsa文件

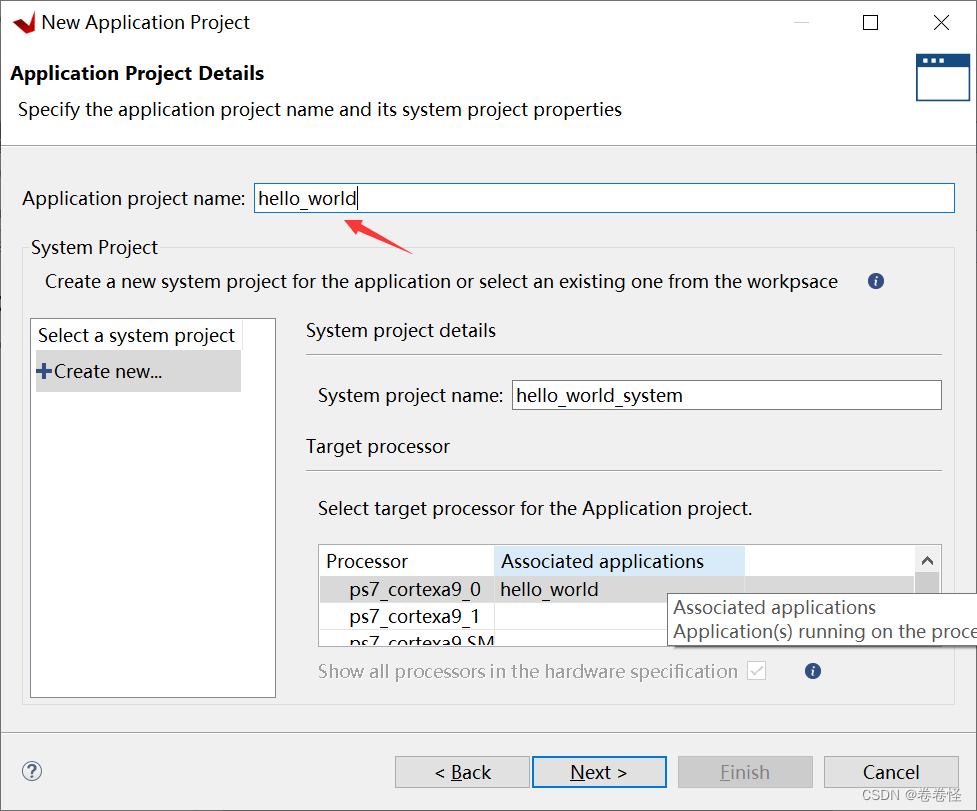

添加工程名字

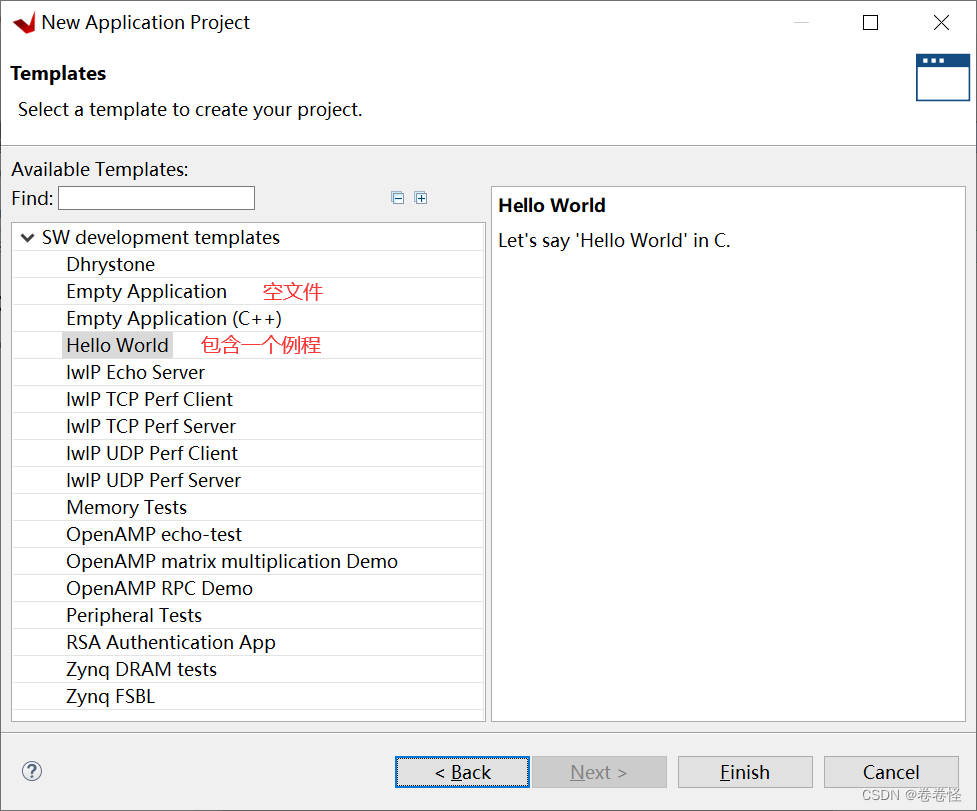

这里选择hello worlf作为演示实验,后面一般选择Empty Application。

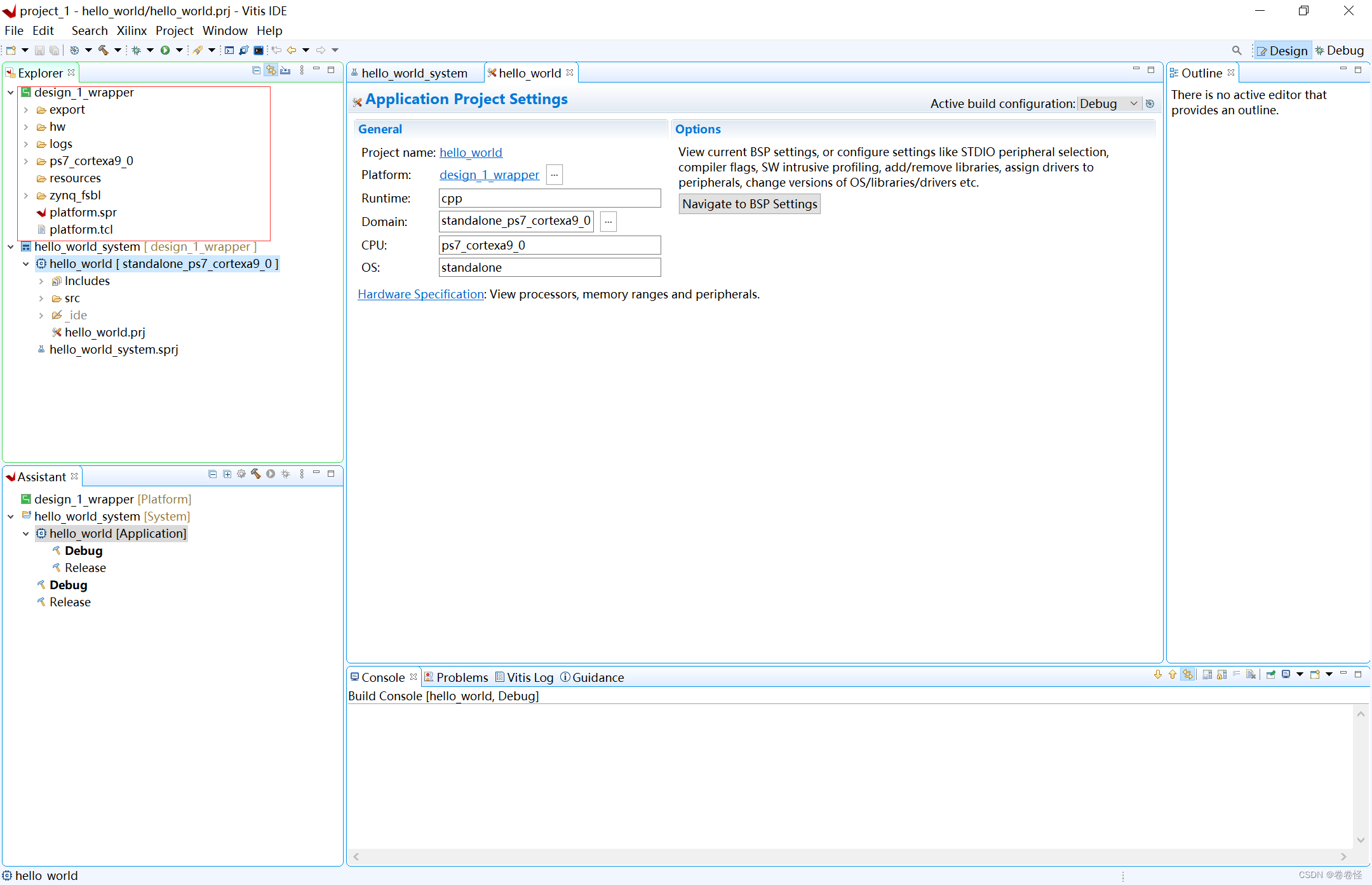

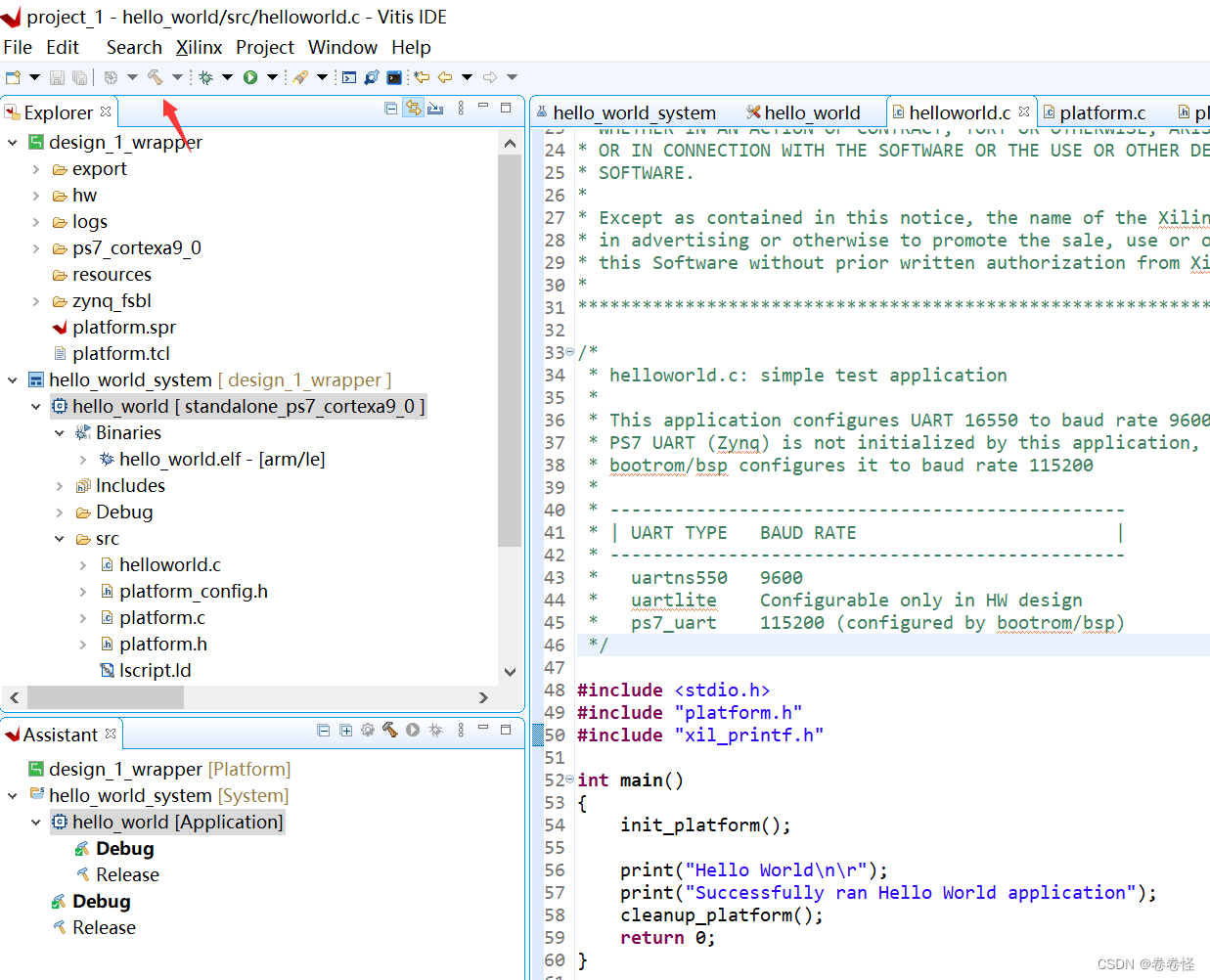

打开后工作区如下:

在启动 vitis之前,我们将硬件以一个 ZIP 压缩文件的形式导出到软件的工作空间。 在vitis启动时,该文件会自动解压, 可以在左侧看到解压后的所有文件。 其中红框部分包含了 Zynq SOC 处理系统的初始化代码,以及 DDR、时钟、 pll 和 MIO 的初始化设置信息。在初始化过程中,vitsi 使用这些信息去配置相应的模块, 使得应用程序能够在 PS 上运行。

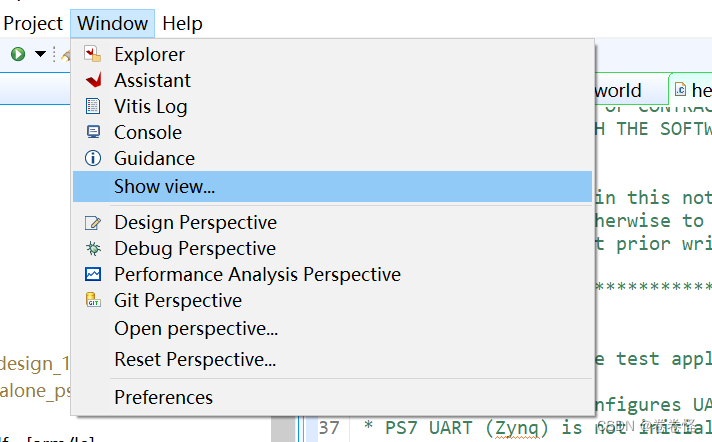

③编译与下载

编译整个工程

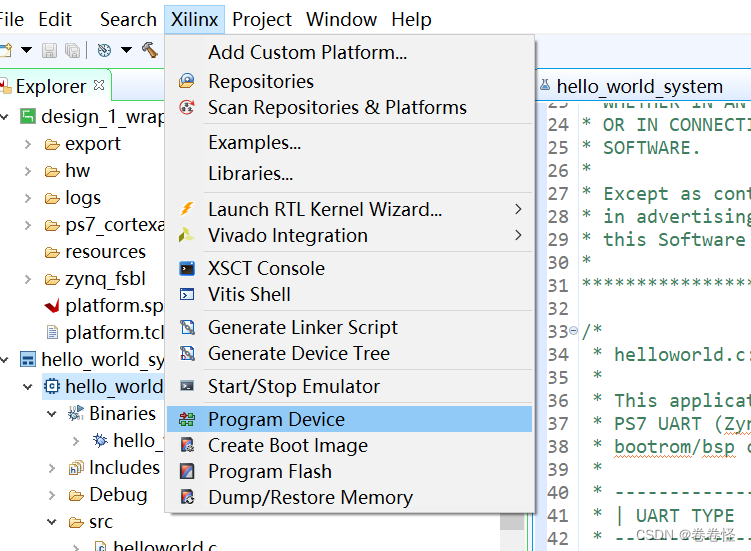

先下载PL部分,点击Program Device

点击Program即可。下载完成后,开发板的done指示灯会亮起。

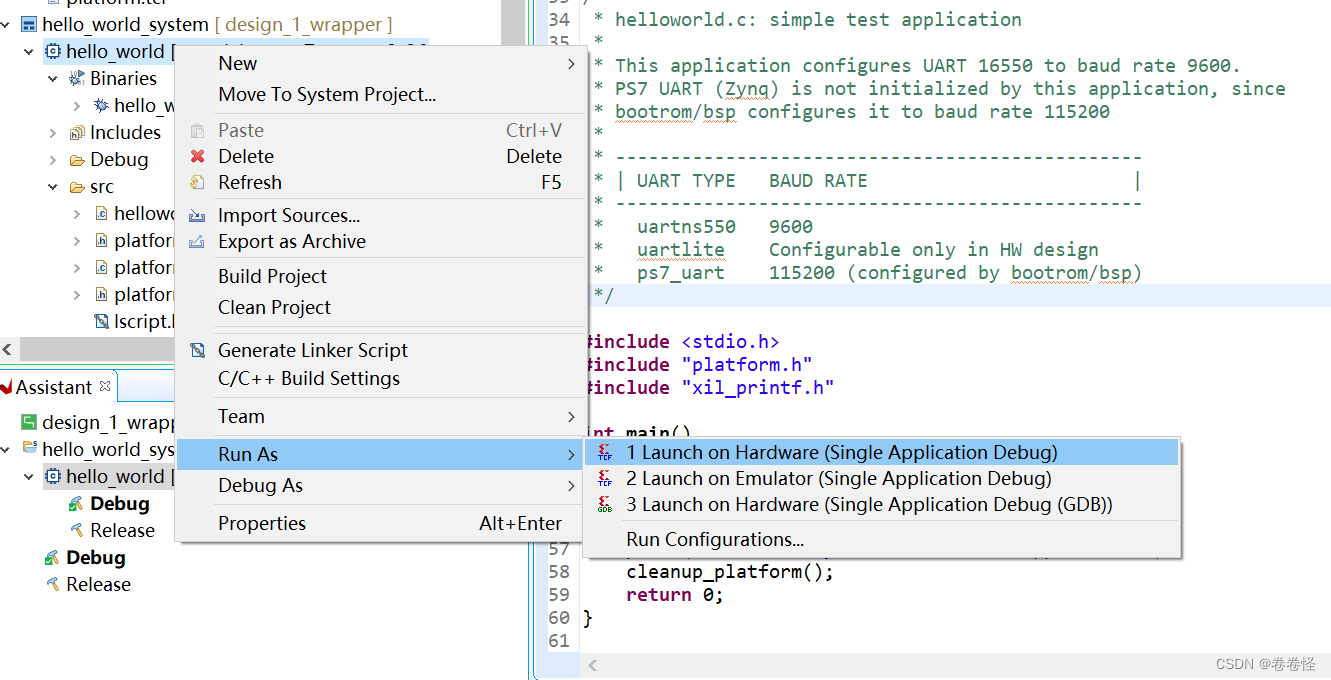

然后下载PS部分

点击工程名,点击Run As,然后,等待进度条下载完成。

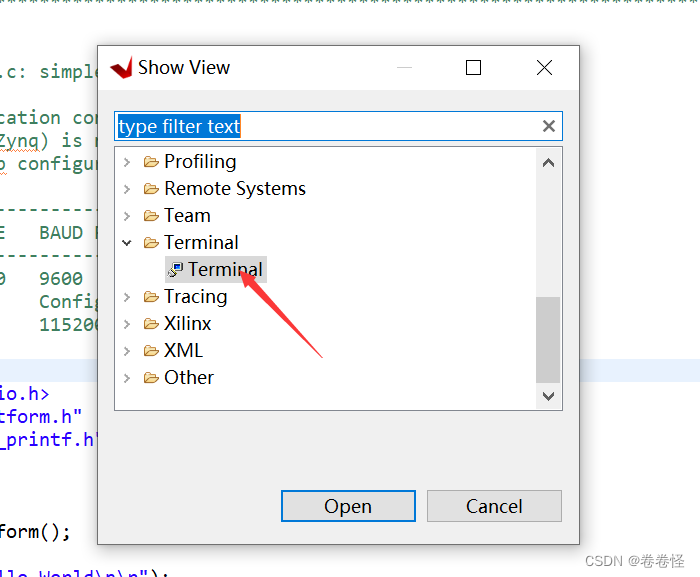

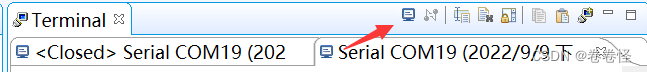

然后打开串口

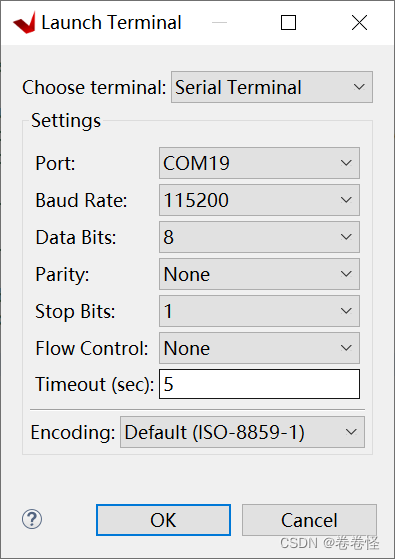

配置串口信息,这里配置信息是在vivado中要和uart配置的信息一致。

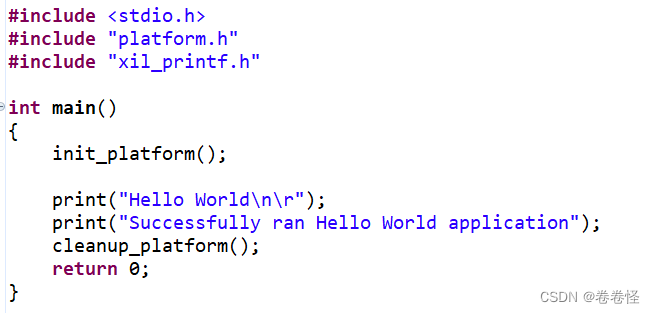

打开串口可以看到例程输出的两个print语句内容。

代码解析:

init_platform 函数的作用是使能 caches 和初始化 uart; cleanup_platform 函数的作用是取消使

能 caches。 实际上这两个函数在该工程中并没有启动任何作用,因为这两个函数是针对于特定平台如Microblaze 的,对于我们使用的 ZYNQ 平台而言是不起作用的,所以 main 函数中只需包含 print语句就可以了,出于平台的通用性和可移植性,此处保留这两个函数。

注意程序中打印字符串“ Hello World”使用的是 print()函数,而不是 C 语言里的 printf()函数。

print()函数是 Xilinx 定义的一个用于打印字符串的函数,调用该函数需要包含头文件“ xil_printf.h”。