ZYNQ 实际上是一个以处理器为核心的系统,PL 只是它的一个外设。Zynq-7000 系列的亮点在于它包含了完整的 ARM 处理器系统,且处理器系统中集成了内存控制器和大量的外设,使 Cortex-A9 处理器可以完全独立于可编程逻辑单元。而且实际上在 ZYNQ 中,PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电。

在前面我们介绍 SOPC 时提到过,FPGA 可以用来搭建嵌入式处理器,像 Xilinx 的 MicroBlaze 处理器或者 Altera 的 Nios II 处理器。像这种使用 FPGA 的可编程逻辑资源搭建的处理器我们称之为“软核”处理器,它的优势在于处理器的数量以及实现方式的灵活性。

而 ZYNQ 中集成的是一颗“硬核”处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的优势是它可以获得相对较高的性能。另外,ZYNQ 中的硬件处理器和软核处理器并不冲突,我们完全可以使用 PL 的逻辑资源搭建一个 Microblaze 软核处理器,来和 ARM 硬核处理器协同工作。

需要注意的是,Zynq 处理器系统里并非只有 ARM 处理器,还有一组相关的处理资源,形成了一个应用处理器单元(Application Processing Unit,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路等。

ZYNQ 处理器系统(PS)示意图如下所示,其中红色高亮区域为 APU。

1、APU

如上图所示是 APU 的简化框图。APU 主要是由两个 ARM 处理器核组成的,每个都关联了一些可计算的单元:

- 一个 NEONTM 媒体处理引擎(Media Processing Engine,MPE)和浮点单元(Floating Point Unit,FPU);

- 一个内存管理单元(Memory Management Unit,MMU);

- 一个一级 cache 存储器(分为指令和数据两个部分)。

APU 里还有一个二级 cache 存储器,再往下还有片上存储器(On Chip Memory,OCM),这些是两个 ARM 处理器共用的。

最后,由一个一致性控制单元(Snoop Control Unit,SCU)在 ARM 核和二级 cache 及 OCM 存储器之间形成了桥连接。SCU 还部分负责与 PL 对接,图中没有标出这个接口。

2、外部接口

如图 1.4.1 所示,Zynq PS 实现了众多接口,既有 PS 和 PL 之间的,也有 PS 和外部部件之间的。PS 和外部接口之间的通信主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)实现的,它提供了可以灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。当需要扩展超过 54 个引脚的时候可以通过扩展 MIO(Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连接之间的直接通路,而是通过共用了 PL 的 I/O 资源来实现的。

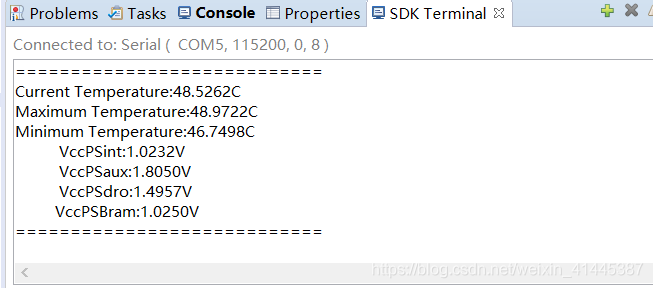

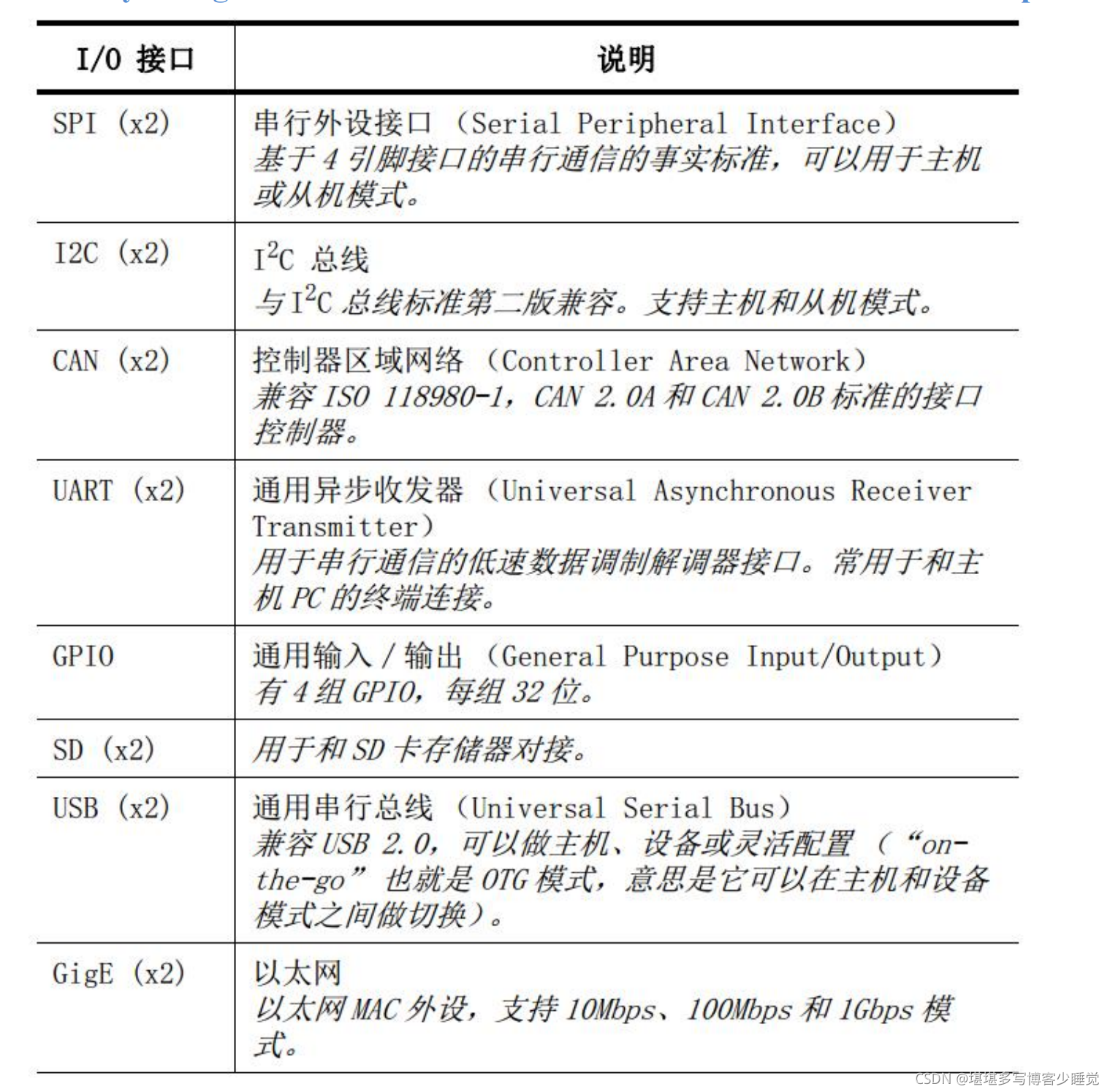

PS 中可用的 I/O 包括标准通信接口和通用输入/输出(General Purpose Input/Output,GPIO),GPIO 可以用做各种用途,包括简单的按钮、开关和 LED。如下图所示:

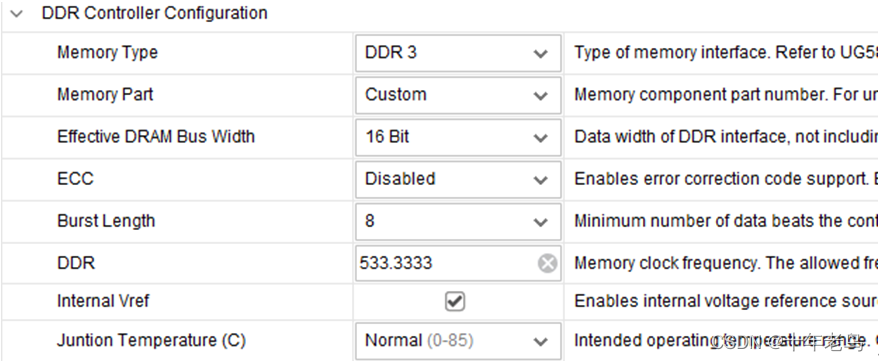

3、存储器接口

Zynq-7000 APSoC 上的存储器接口单元包括一个动态存储器控制器和几个静态存储器接口模块。动态存储器控制器可以用于 DDR3、DDR3L、DDR2 或 LPDDR2。静态存储器控制器支持一个 NAND 闪存接口、一个 Quad-SPI 闪存接口、一个并行数据总线和并行 NOR 闪存接口。

4、片上存储器

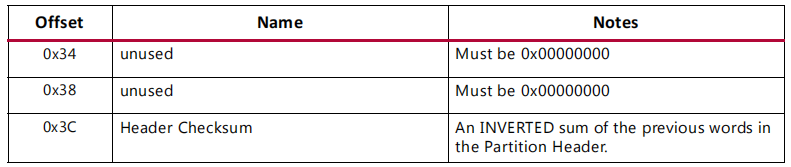

片上存储器包括 256kB 的 RAM(OCM)和 128kB 的 ROM(BootROM)。OCM 支持两个 64 位 AXI 从机接口端口,一个端口专用于通过 APU SCU 的 CPU/ACP 访问,而另一个是由 PS 和 PL 内其他所有的总线主机所共享的。BootROM 是 ZYNQ 芯片上的一块非易失性存储器,它包含了 ZYNQ 所支持的配置器件的驱动。BootROM 对于用户是不可见的,专门保留且只用于引导的过程。

5、AXI 接口

ZYNQ 将高性能 ARM Cotex-A 系列处理器与高性能 FPGA 在单芯片内紧密结合,为设计带来了如减小体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA 融合在一个芯片上之后,片内处理器与 FPGA 之间的互联通路就成了 ZYNQ 芯片设计的重中之重。如果 Cotex-A9 与FPGA 之间的数据交互成为瓶颈,那么处理器与 FPGA 结合的性能优势就不能发挥出来。

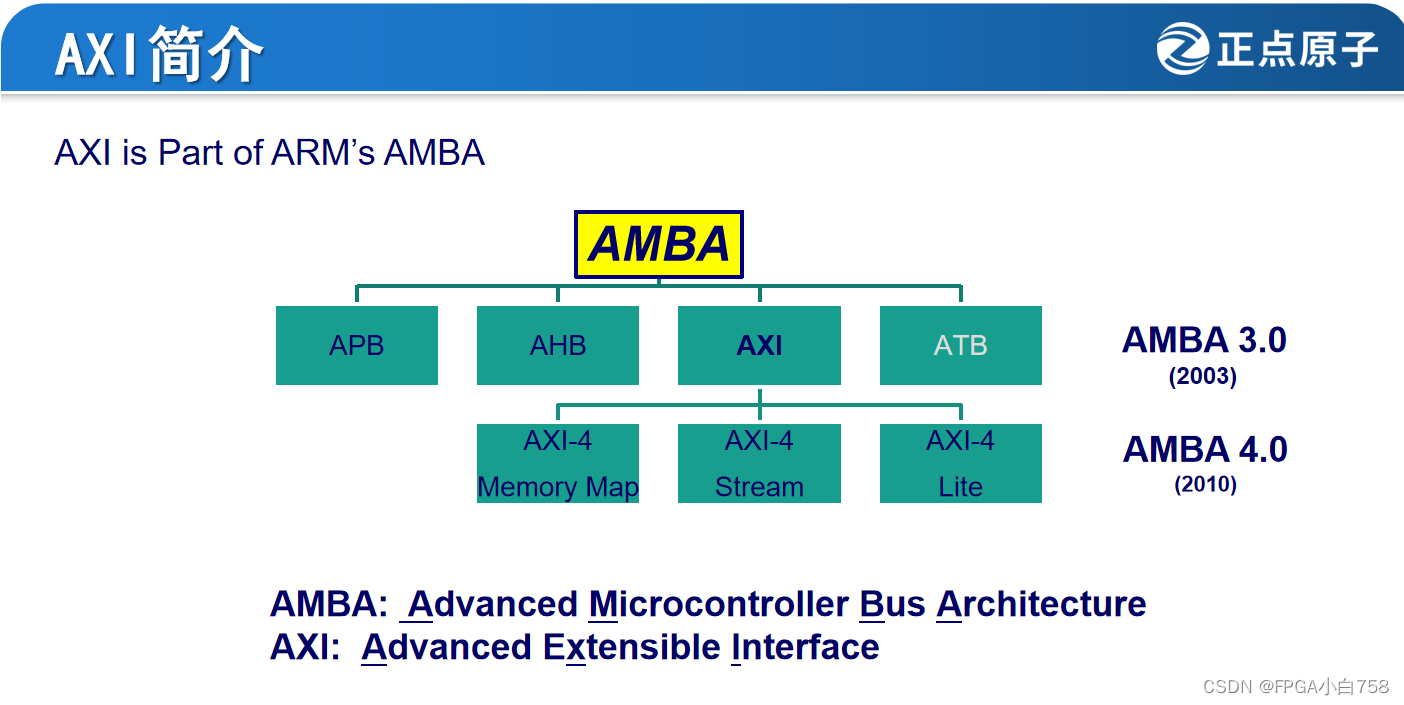

Xilinx 从 Spartan-6 和 Virtex-6 系列开始使用 AXI 协议来连接 IP 核。在 7 系列和 ZYNQ-7000 AP SoC 器件中,Xilinx 在 IP 核中继续使用 AXI 协议。AXI 的英文全称是Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。

AXI4 协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里我们首先解释一下存储映射(Meamory Map)这一概念。如果一个协议是存储映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是针对该存储空间的读写操作。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接 口等需要高速数据传输的场合。

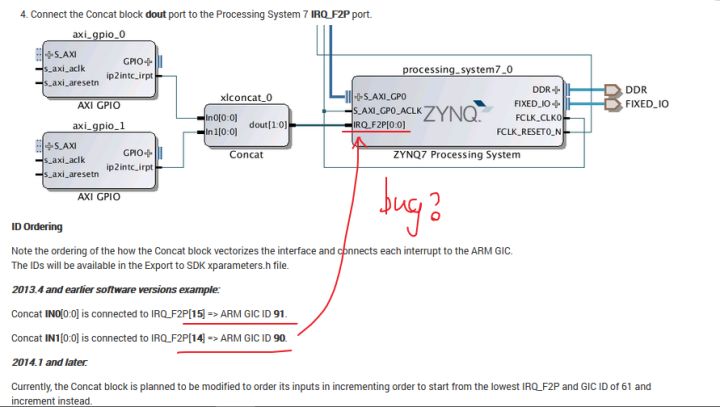

在 PS 和 PL 之间的主要连接是通过一组 9 个 AXI 接口,每个接口有多个通道组成。这些形成了 PS 内部的互联以及与 PL 的连接,如下图所示:

上图给出了每个接口的简述,标出了主机和从机(按照惯例,主机是控制总线并发起会话的,而从机是做响应的)。需要注意的是,接口命名的第一个字母表示的是 PS 的角色,也就是说,第一个字母 “M”表示 PS 是主机,而第一个字母“S”表示 PS 是从机。

上图中 PS 和 PL 之间的 9 个 AXI 接口可以分成三种类型:

1、通用 AXI(General Purpose AXI):一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

2、加速器一致性端口(Accelerator Coherency Port):在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL 的单元之间的一致性。PL 是做主机的。

3、高性能端口(High Performance Ports):四个高性能 AXI 接口,带有 FIFO 缓冲来提供“批量”读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机的。

上面的每条总线都是由一组信号组成的,这些总线上的会话是根据 AXI4 总线协议进行通信的。