1、基础知识

1.1 概念

SPI(Serial Peripheral Interface,串行外围设备接口),是Motorola公司提出的一种同步串行接口技术,是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据传输,广泛用于EEPROM、Flash、RTC(实时时钟)、ADC(数模转换器)、DSP(数字信号处理器)以及数字信号解码器上。SPI通信的速度很容易达到好几兆bps,所以可以用SPI总线传输一些未压缩的音频以及压缩的视频。

特点:

SPI设备之间通信必须由主设备控制从设备,主设备可通过片选实现控制多个从设备,从设备不能产生或控制时钟,只可主设备提供。

SPI是采用同步方式传输数据的。

SPI设备之间数据传输又称为数据交换,不管是读数据还是写数据都需要发送数据到从设备为其提供时钟,才能正常进行,在有些设备读取数据时可能需要先写入数据,此时一定要记得将写入时从设备响应的数据也读出来,后面才可读出对应需要的数据。

优点:

支持全双工操作,操作简单,数据传输速率较高。

缺点:

需要占用主机较多的口线,只支持单个主机,没有应答机制确认是否接收到数据,相对于IIC缺点来说是一个大的缺点。

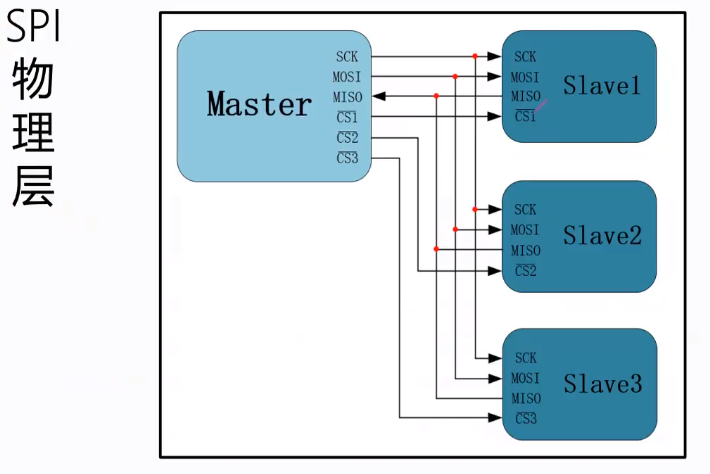

1.2 SPI物理层

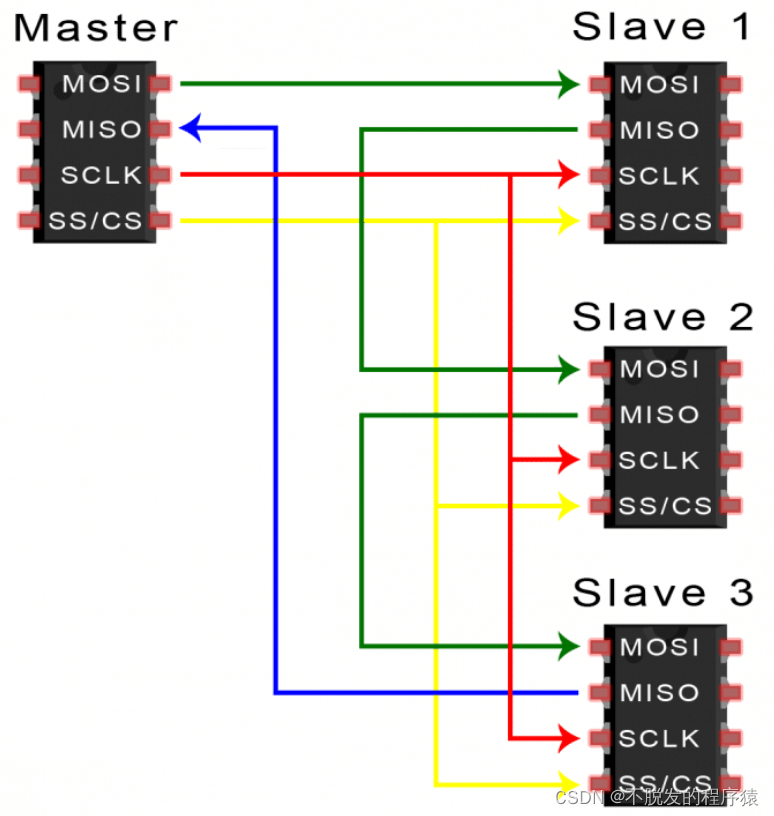

采用主从模式(Master-Slave)的控制方式,支持单Master多Slave。

SPI规定了两个SPI设备之间通信必须由主设备Master来控制从设备Slave。也就是说,如果FPGA是主机的情况下,不管是FPGA给芯片发送数据还是从芯片中接收数据,写Verilog逻辑的时候片选信号CS与串行时钟信号SCK必须由FPGA来产生。同时一个Master可以设置多个片选(Chip Select)来控制多个Slave。SPI协议还规定Slave设备的clock由Master通过SCK管脚提供给Slave,Slave本身不能产生或控制clock,没有clock则Slave不能正常工作。

注:一主一从

SCK(Serial Clock):SCK是串行时钟线,作用是Master向Slave传输时钟信号,控制数据交换的时机和速率,它由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,两个设备之间通讯时,通讯速率受限于低速设备。

MOSI(Master Out Slave in):在SPI Master上也被称为Tx-channel,作用是SPI主机给SPI从机发送数据,主机的数据从这条信号线输出,从机由这条信号线读入主机发送的数据,即这条线上数据的方向为主机到从机。

MISO(Master In Slave Out):在SPI Master上也被称为Rx-channel,作用是SPI主机接收SPI从机传输过来的数据,主机从这条信号线读入数据,从机的数据由这条信号线输出到主机,即在这条线上数据的方向为从机到主机。

CS/SS(Chip Select/Slave Select):从设备选择信号线,常称为片选信号线,也称为 NSS、SS。SPI 协议中没有设备地址,它使用 cs 信号线来寻址,当主机要选择从设备时,把该从设备的 cs 信号线设置为低电平,该从设备即被选中,即片选有效,接着主机开始与被选中的从设备进行 SPI 通讯。所以SPI通讯以 cs 线置低电平为开始信号,以 cs 线被拉高作为结束信号。

注:一主多从

SPI 协议使用 3 条总线及N条片选线,3 条总线分别为 SCLK、MOSI、MISO,片选线为CS,其中3条总线是多个从设备共用的,CS是每一个从机有一条。

1.3 SPI协议层

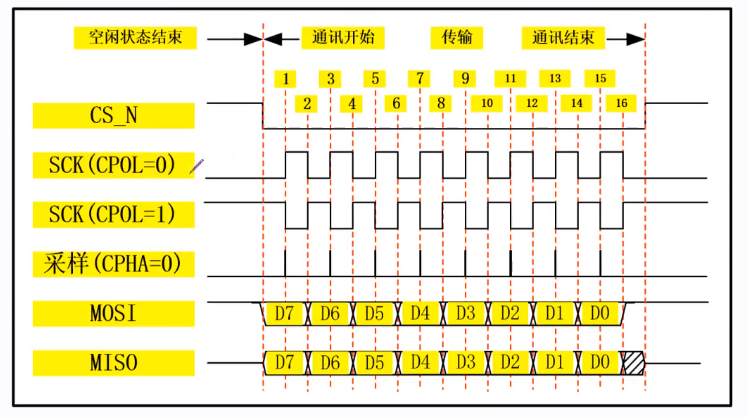

SPI总线在传输数据的同时也传输了时钟信号,所以SPI协议是一种同步(Synchronous)传输协议。Master会根据将要交换的数据产生相应的时钟脉冲,组成时钟信号,时钟信号通过时钟极性(CPOL)和时钟相位(CPHA)控制两个SPI设备何时交换数据以及何时对接收数据进行采样,保证数据在两个设备之间是同步传输的。

SPI总线传输一共有4中模式,这4种模式分别由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义,其中CPOL参数规定了SCK时钟信号空闲状态的电平,CPHA规定了数据是在SCK时钟的上升沿被采样还是下降沿被采样。

时钟极性 CPOL: 表示SPI 通讯设备处于空闲状态时,SCK信号线的电平信号(即 SPI 通讯开始前、CS 线为高电平时 SCLK的状态)。CPOL=0时, SCK在空闲状态时为低电平,CPOL=1 时,则相反。

时钟相位 CPHA:表示数据采样的时刻,当 CPHA=0 时,MOSI 或 MISO 数据线上的信号将会在 SCLK 时钟线的“奇数边沿”被采样。当 CPHA=1 时,数据线在 SCLK 的“偶数边沿”采样。

模式0:CPOL= 0,CPHA=0。SCK串行时钟线空闲是为低电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

模式1:CPOL= 0,CPHA=1。SCK串行时钟线空闲是为低电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式2:CPOL= 1,CPHA=0。SCK串行时钟线空闲是为高电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式3:CPOL= 1,CPHA=1。SCK串行时钟线空闲是为高电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

| SPI工作模式 | CPOL | CPHA | 空闲时的SCLK电平 | 采样时刻 |

|---|---|---|---|---|

| 0 | 0 | 0 | 低电平 | 奇数边沿 |

| 1 | 0 | 1 | 低电平 | 偶数边沿 |

| 2 | 1 | 0 | 高电平 | 奇数边沿 |

| 3 | 1 | 1 | 高电平 | 偶数边沿 |

SPI通信过程:

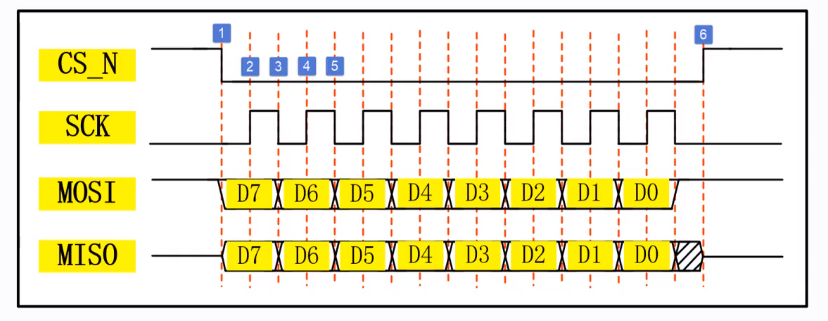

SPI总线协议是一种全双工的串行通信协议,数据传输时高位在前,低位在后。SPI协议规定一个SPI设备不能在数据通信过程中仅仅充当一个发送者(Transmitter)或者接受者(Receiver)。在片选信号CS为0的情况下,每个clock周期内,SPI设备都会发送并接收1 bit数据,相当于有1 bit数据被交换了。数据传输高位在前,低位在后(MSB first)。SPI主从结构内部数据传输示意图如下图所示:

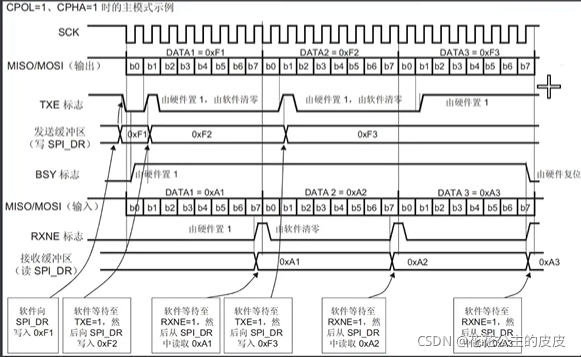

在对SPI核操作的控制寄存器进行设置之后即可启动数据传输。数据传输的启动是通过向数据寄存器SPDR中写入数据。对数据寄存器执行写操作实际上是往一个4项写队列中添加数据项。每次写操作即往队列中写入一个字节的数据。当SPI核被使能时,并且写缓冲区不为空,SPI核就是会自动往发送写队列中最旧的数据项。接收数据与发送数据同时进行;每当发送一个字节的数据,同时总会收到一个字节的数据。如果想要的接收一个字节的数据,需要往写缓冲区写入一个字节的冗余数据,这样做是为了让SPI核启动数据传输,在发送冗余数据的同时接收想要的数据,每完成接收一个字节的数据,这个字节会被移入读缓冲区。读缓冲区和写缓冲区是对立的,是一个独立的4项队列。对数据寄存器执行读操作,便会得到读队列中的数据项。