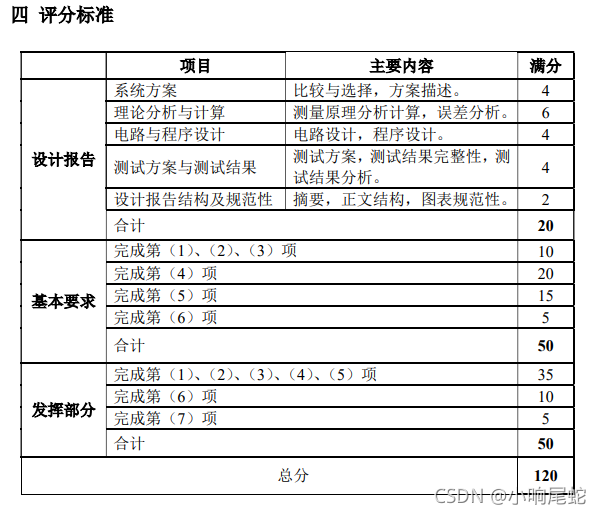

2015年电子设计竞赛题目-数字频率计题目解析

本期将讲解2015年电子设计竞赛数字频率计的硬件及软件实现方法

一、题目解读

通过阅读题目,总结出以下设计要点:

1、测频率。要求测量幅值从10mVrms到1Vrms,频率从1Hz到100MHz的正弦波的频率,频率测量的相对误差不大于

2、测时间间隔。两路方波,峰峰值从50mV到1V,频率从100Hz到1MHz,可以保证两路信号同频率,但是幅值和相位不同,测量相位差,时间间隔相对误差绝对值不大于

3、测占空比。一路脉冲波,峰峰值从50mV到1V,频率从1Hz到5MHz,占空比从10%到90%,测量信号的占空比,占空比相对误差绝对值不大于。

首先,要明确概念,何为方波,何为脉冲波,本人理解方波正负电平对阵,脉冲波只有正电平。其次,本题对硬件和软件要求都比较高,下文将主要讲解硬件部分,软件部分请参考:2015_数字频率计.zip_数字频率计-C++文档类资源-CSDN下载

二、硬件电路设计

1、测频电路设计

在测频部分对电路的要求如下:

(1)带宽要足够,100MHz能保持高增益。

(2)过驱恢复时间尽可能短,虽然在正弦波部分只要能捕获上升沿即可,但是过驱恢复时间必须小于10ns,否则将会出现丢波,而对于很对运放来说过驱恢复时间一般不在手册中给出,只能通过实验去测量。之前用的AD8009实测不能胜任100MHz正弦波的饱和放大,而OPA691在10倍放大倍数下过驱恢复时间在6ns以内,可以使用。

(3)需要比较器。虽然实测FPGA对直接输入的正弦波也可以测量频率,但是在饱和放大后波形可能会畸变导致测得频率发生改变,所以需要一级比较器进行整形。这里选用TLV3501

(4)需要电平提升电路。喂给FPGA的电平要合适。

综上所述,设计出的电路结构文字叙述如下:

信号→阻抗匹配→OPA691进行10倍放大,±2.5V供电→阻抗匹配→OPA691进行5倍放大,±2.5V供电→阻抗匹配→TLV3501进行迟滞比较,±2.5V供电→阻抗匹配→THS3201进行电平提升,±5V供电(最后一级主要是因为手头有THS3201所以选用,其他运放也可以,但是注意电平提升电路必须直接耦合,不能用隔直电路)

2、测时间间隔电路

做两路测频电路即可

3、测占空比电路

占空比的测量也可以用饱和放大的方法,但是过驱恢复时间要求很短,否则需要对不同幅值进行软件定标,并进行线性插值,实现起来很麻烦,而且效果未知。因此这一集采用了程控闭环放大,使信号不饱和其输出幅度一样。

程控闭环放大的实现方法较多,比如自动增益电路不需要软件介入(带二极管的需要慎重),本文采用AD检测输出信号幅值,并VCA821进行压控,从而构成闭环。

电路的总体结构如下:

调试笔记:

占空比测量:

本来是打算用性能貌似更加优秀的OPA695饱和放大试一下,但是芯片貌似坏了,后面补上测量

因为OPA691的过驱恢复时间和输入信号幅值有关(和占空比关系不大),所以可以采用定标法测量,但是采用了另一种思路;

利用VCA821作为前级,增益范围初始设定为-20dB到20dB,10mV设定增益为20dB,VCA821输出为50mV;1V设定增益为-20dB,VCA821输出为50mV。VCA821的增益电阻RG为75Ω,RF为402Ω。后级跟OPA691八倍,OPA691八倍,AD8009八倍。在调试过程中发现当输入信号达到450mV时,输出出现一个平台,约为14mV,且随着输入信号幅度增大平台时间越长。后来发现是VCA821输入信号范围与RG有关,需要根据输入信号范围选择RG,最终确定RG为200Ω,最大增益为8倍左右。然后增大后级增益,一使得最后输入到FPGA的信号不变,调试成功。然后遇到的问题是VCA821输出偏置过大,输出信号的最小值大于FPGA能识别的低电平,然后参考器件手册中给出的调节偏置电压的方法,通过两个电位器调节,效果很明显,而且还可以通过调节电位器抵消后级的偏置电压。现在还差的就是闭环控制的形成,通过AD采样信号,自动选择增益。对了,VCA821单极输出过程,发现方波的高电平有一个很嘈杂的“帽子”,原因是控制电压不稳,通过在控制电压上加滤波电容得到改善。

最终电路实物图如下: