nRF24L01模块

官网链接: https://www.nordicsemi.com/Products/nRF24-series

常见的无线收发模块, 工作在2.4GHz频段, 适合近距离遥控和数据传输.

nRF24L01是一个能兼顾距离和数据速率的无线模块, 在空旷环境下,2M速率15米, 1M速率30米, 250K速率能达到50米. 和蓝牙相比距离更远, 和ESP8266这类以太网WiFi相比环境适应力更强.

参数

- 2.4GHz ISM频段

- 250Kbps, 1Mbps, 2Mbps三种空中传输速率

- 输出功率为 0dBm时发射功耗为11.3mA

- 空中传输速率为2Mbps时接收功耗为13.5mA

- Power down模式功耗低至900nA, Standby-I模式功耗低至26uA

- 1.9-3.6V的电压工作范围

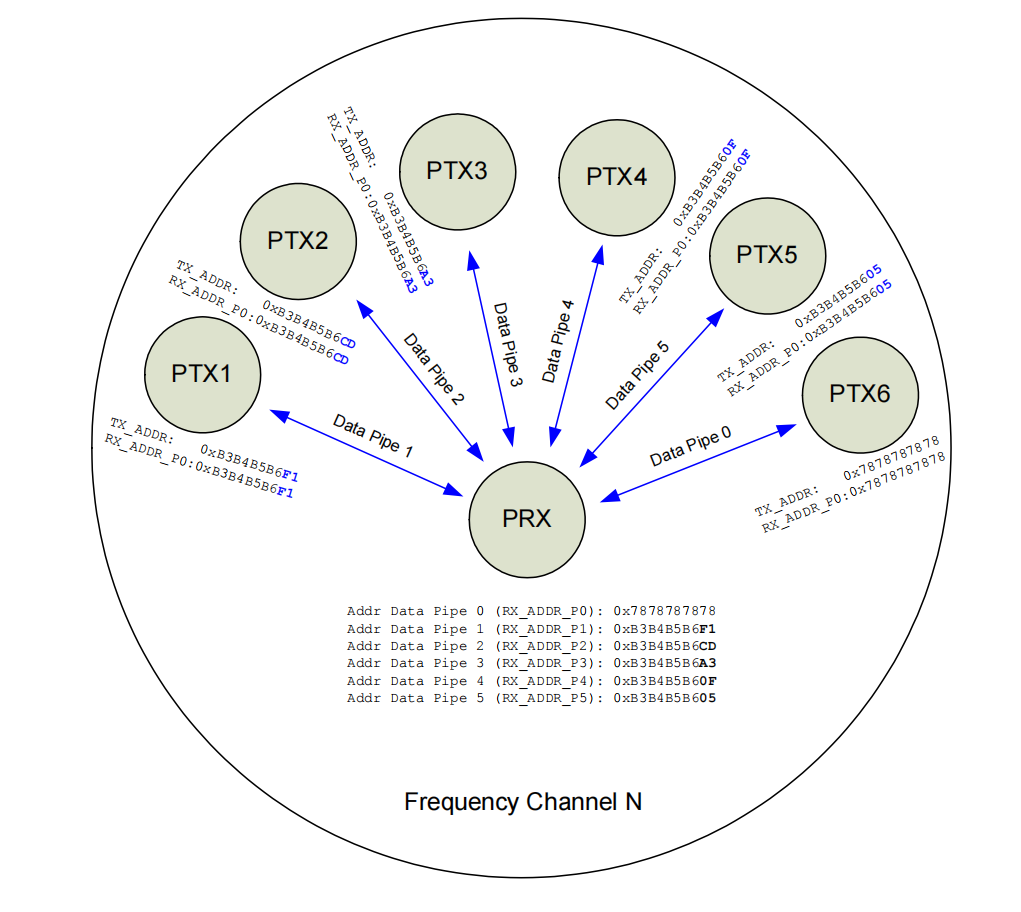

- 支持6个接收通道(地址)

- IO口能承受5V电压

- ±60ppm 16MHz晶体振荡器

- 4×4mm QFN封装

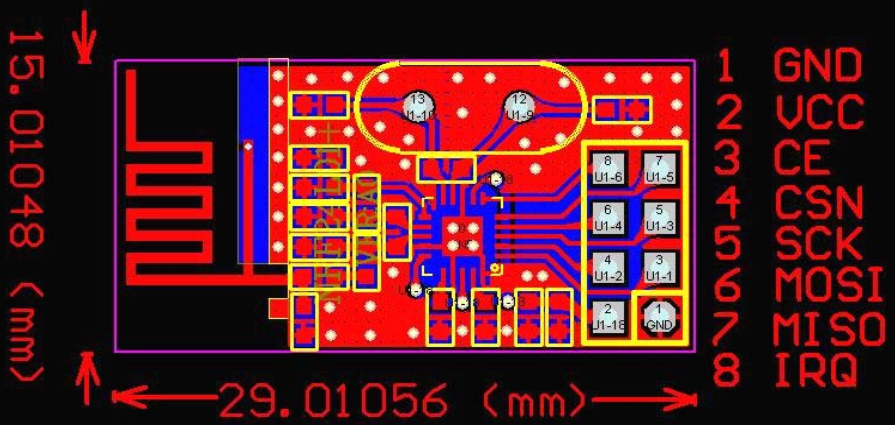

nRF24L01 模块PIN布局

元件面朝自己,天线朝左(晶振在上), 右侧PIN脚的定义为:

| IRQ | MISO |

| MOSI | CSK |

| CSN | CE |

| VCC | GND |

PIN脚定义

| CE | 数字信号输入 | Chip Enable, RX和TX模式选择 |

| CSN | 数字信号输入 | SPI chip select, 低电平使能 |

| SCK | 数字信号输入 | SPI serial clock |

| MOSI | 数字信号输入 | 从机数据输入 |

| MISO | 数字信号输出 | 从机数据输出, 有三种状态选项 |

| IRQ | 数字信号输出 | 可屏蔽中断脚, 低电平使能 |

| VDD | 电源 | 1.9 - 3.6V |

| VSS | 电源 | 接地 (0V) |

PIN: IRQ

正常状态为高电位, 只有当STATUS寄存器的以下三个位被置位(拉高)时会拉低电压输出, 要清除中断, 需要相应地往这三个位写入1.

- RX_DR(Received Ready)

- TX_DS (Data Sent)

- MAX_RT(Transmit Failed After Max Retransmits)

可以通过寄存器地址0x00分别对这三种中断进行屏蔽

The nRF24L01 has an active low IRQ pin. The IRQ pin has three sources: it is activated when TX_DS (Transmit Data Sent), RX_DR (Receive Data Ready) or MAX_RT (Max Retransmit) bit are set high by the Enhanced ShockBurst in the STATUS register. The IRQ pin resets when MCU writes ‘1’ in the STATUS register on the bit associated to the IRQ active source. As example, we can suppose that a MAX_RT events happens. So, we will detect an IRQ transition from high to low and checking STATUS register we will found that MAX_RT bit is high. So we should take necessary actions and than set MAX_RT to high in the STATUS register to clear IRQ.To detect IRQ we can use EXT driver from ChibiOS/HAL. This driver launches a callback when detects a transition (on rising, falling or both edge according to its configuration), anyway, we will discuss this callback in detail later.状态之间的转移

- Power Down 模式

在该模式下, nRF24L01+的功耗最小, 不能进行发送或者接收. 但是所有寄存器的值保持不变, SPI处于有效状态, 允许对寄存器, TX/RX FIFO进行操作, PWR_UP(此位在CONFIG寄存器中)清0即进入该状态. - Standby-I 模式

将PWR_UP置1, 即进入Standby-I模式, 该模式既降低了nRF24L01+的平均功耗, 同时又保持尽可能短的启动时间, 将CE置1然后后清0, 就可以进入TX/RX模式, 然后又返回到Standby-I模式. - Standby-II 模式

当nRF24L01+设置为接收机(PTX), 并且CE=1, TX FIFO为空时即进入该模式. 相比Standby-I模式, 这种模式相对耗电, 一旦发送FIFO有新数据, 就会立即将数据打包发送出去. - TX 模式, 进入该模式需要 PWR_UP=1, PRIM_RX=0, TX FIFO不为空, CE=1脉冲宽度超过10us

- RX 模式, 进入该模式需要 PWR_UP=1, PRIM_RX=1, CE=1

工作流程

发送流程

- MCU通过SPI对NRF24L01进行基本配置, 配置自动应答通道使能, 设置自动重发次数不为0(在此设置可以重发数据包)设置为发送模式, 还有其他配置等等

- MCU把要发送的数据和接收数据设备的地址通过SPI写入NRF24L01

- 这里有一个坑需要注意, 发送状态下, 发送的目标地址 TX_ADDR 必须与RX_ADDR_P0相同!! 这个地址将用于接受对方返回的ACK, 如果RX_ADDR_P0填的不对, 对方依然能收到数据, 但是本地会多次重试后产生MAX_RT中断

- CE引脚置高, 启动发送

- 此时有两种情况

- 在有限时间内收到应答信号, 则TX_DS置高(发送数据成功标志位), 并引发IRQ中断(引脚IRQ置低), 并清除TX buff(发送缓冲寄存器, 自行写代码清除), IRQ中断需要写状态寄存器进行复位(因为此处IRQ由TX_DS引发, 将TX_DS复位即可使IRQ复位)

- 重发数据次数超过设定值, 则MAX_RT置高(达到最多重发次数标志位), 并引发IRQ中断(引脚IRQ置低), 不清除TX buff, IRQ中断需要写状态寄存器进行复位(因为此处IRQ由MAX_RT引发,将MAX_RT复位即可使IRQ复位)

- 接收到应答信号产生中断或者达到最大重发次数产生中断后,NRF24L01继续发下一包数据

- 当TX buff为空时, 进入待机模式二(当CE为高, TX buff为空时进入待机模式二), NRF24L01的工作模式图表在后面. 只要在适当时候拉高CE进行发送即可, 配置NRF24L01时CE置低)

接收流程

- 与发送模式一样, 一开始MCU通过SPI对NRF24L01进行基本配置, 设置数据通道自动应答使能(在EN_AA寄存器进行设置, 即收到数据后自动向主机发送应答信号), 还有进行接收数据通道使能(在EN_RXADDR寄存器配置), 即选择六个接收通道的某一通道来接收数据, 设置为接收模式, 以及其他配置.

- 拉高CE引脚(CE置高), 启动接收状态

- 接收到一个有效数据包后, 数据存储在RX buff, 并产生RX_DR中断(RX_DR为接收数据成功标志位, 接收成功置1), 中断和发送模式一样, 需要复位

- 接收设备自动向发送设备发送确认信号(这步是自动的)

- 设置CE引脚为低, NRF24L01进入待机模式一

- MCU通过SPI读取NRF24L01收到的数据

总结

- 发送过程

- MCU通过SPI对NRF24L01进行基本配置,配置好NRF24L01

- MCU将要发送的数据与接收数据设备的地址写入NRF24L01

- CE引脚置高,启动发送

- 接收过程

- MCU通过SPI对NRF24L01进行基本配置,配置好NRF24L01

- CE引脚置高,启动接收

- MCU对 NRF24L01进行数据读取

NRF24L01的USB串口调试设备

淘宝上有配套出售的一种USB转接卡, 用于将NRF24L01通过USB到电脑, 此时NRF24L01相对于电脑成为一个串口设备, 通过AT命令进行通信.

- 所有命令均为大写

- 标点符号必须英文状态下的半角标点

- 无空格

- 不可更改的参数

- 地址长度必须为5位

- 数据长度必须是32个字节

- 发射功率为0dbm

- 如果用上位机和这个USB转接卡进行调试的话, 要注意这里有个坑: 用户可用的字节为1-31个, 第0位不可用, 这个字节系统保留, 用于记录传输的数据包长度. 例如: 串口发送

abc(ASCII码, 3 bytes), 实际传输3abc(第0个字节就为3), 接收端根据第0字节中的数来判断收到的数据包长度, 再通过串口TX输出给电脑的就是abc.

相关的命令有

- AT? 系统信息查询

- AT+BAUD=n n为1,2,3,4,5,6,7分别对应4800,9600,14400,19200,38400,115200的波特率

- AT+RATE=n n为1,2,3分别对应250Kbps ,1Mbps,2Mbps的传输速率

- AT+RXA=0x??,0x??,0x??,0x??,0x?? 0x??为十六进制本机地址, 英文逗号分隔

- AT+TXA=0x??,0x??,0x??,0x??,0x?? 目标地址, 其他同上

- AT+FREQ=2.xxxG 2. xxx为要设定的频率, 范围2.400GHz-2.525GHz, 超过范围无效, 小数点后面为三位数字, 不足三位需补零, 大写字母G不可缺少

- AT+CRC=n n等于8或者16, 设置8位或16位CRC校验

- 发送消息 直接往串口输出, 且不符合上面命令格式的, 都会发送到目标地址

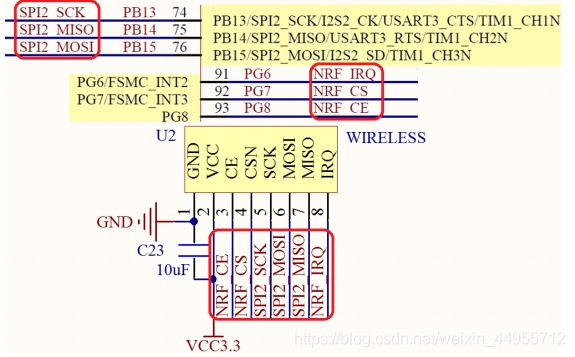

STM32F103C8T6

接线方式

| STM32 | nRF24L01 |

|---|---|

| PA4 SPI1_NSS | N/A |

| PA5 SPI1_SCK | SCK |

| PA6 SPI1_MISO | MISO |

| PA7 SPI1_MOSI | MOSI |

| PB13 | IRQ |

| PB14 | CE |

| PB15 | CSN |

代码示例

Github项目: https://github.com/IOsetting/stm32f103-nrf24l01

常量定义

// SPI(nRF24L01) commands

#define NRF24L01_CMD_REGISTER_R 0x00 // Register read

#define NRF24L01_CMD_REGISTER_W 0x20 // Register write

#define NRF24L01_CMD_ACTIVATE 0x50 // (De)Activates R_RX_PL_WID, W_ACK_PAYLOAD, W_TX_PAYLOAD_NOACK features

#define NRF24L01_CMD_RX_PLOAD_WID_R 0x60 // Read RX-payload width for the top R_RX_PAYLOAD in the RX FIFO.

#define NRF24L01_CMD_RX_PLOAD_R 0x61 // Read RX payload

#define NRF24L01_CMD_TX_PLOAD_W 0xA0 // Write TX payload

#define NRF24L01_CMD_ACK_PAYLOAD_W 0xA8 // Write ACK payload

#define NRF24L01_CMD_TX_PAYLOAD_NOACK_W 0xB0 //Write TX payload and disable AUTOACK

#define NRF24L01_CMD_FLUSH_TX 0xE1 // Flush TX FIFO

#define NRF24L01_CMD_FLUSH_RX 0xE2 // Flush RX FIFO

#define NRF24L01_CMD_REUSE_TX_PL 0xE3 // Reuse TX payload

#define NRF24L01_CMD_LOCK_UNLOCK 0x50 // Lock/unlock exclusive features

#define NRF24L01_CMD_NOP 0xFF // No operation (used for reading status register)// SPI(nRF24L01) register address definitions

#define NRF24L01_REG_CONFIG 0x00 // Configuration register

#define NRF24L01_REG_EN_AA 0x01 // Enable "Auto acknowledgment"

#define NRF24L01_REG_EN_RXADDR 0x02 // Enable RX addresses

#define NRF24L01_REG_SETUP_AW 0x03 // Setup of address widths

#define NRF24L01_REG_SETUP_RETR 0x04 // Setup of automatic re-transmit

#define NRF24L01_REG_RF_CH 0x05 // RF channel

#define NRF24L01_REG_RF_SETUP 0x06 // RF setup

#define NRF24L01_REG_STATUS 0x07 // Status register

#define NRF24L01_REG_OBSERVE_TX 0x08 // Transmit observe register

#define NRF24L01_REG_RPD 0x09 // Received power detector

#define NRF24L01_REG_RX_ADDR_P0 0x0A // Receive address data pipe 0

#define NRF24L01_REG_RX_ADDR_P1 0x0B // Receive address data pipe 1

#define NRF24L01_REG_RX_ADDR_P2 0x0C // Receive address data pipe 2

#define NRF24L01_REG_RX_ADDR_P3 0x0D // Receive address data pipe 3

#define NRF24L01_REG_RX_ADDR_P4 0x0E // Receive address data pipe 4

#define NRF24L01_REG_RX_ADDR_P5 0x0F // Receive address data pipe 5

#define NRF24L01_REG_TX_ADDR 0x10 // Transmit address

#define NRF24L01_REG_RX_PW_P0 0x11 // Number of bytes in RX payload in data pipe 0

#define NRF24L01_REG_RX_PW_P1 0x12 // Number of bytes in RX payload in data pipe 1

#define NRF24L01_REG_RX_PW_P2 0x13 // Number of bytes in RX payload in data pipe 2

#define NRF24L01_REG_RX_PW_P3 0x14 // Number of bytes in RX payload in data pipe 3

#define NRF24L01_REG_RX_PW_P4 0x15 // Number of bytes in RX payload in data pipe 4

#define NRF24L01_REG_RX_PW_P5 0x16 // Number of bytes in RX payload in data pipe 5

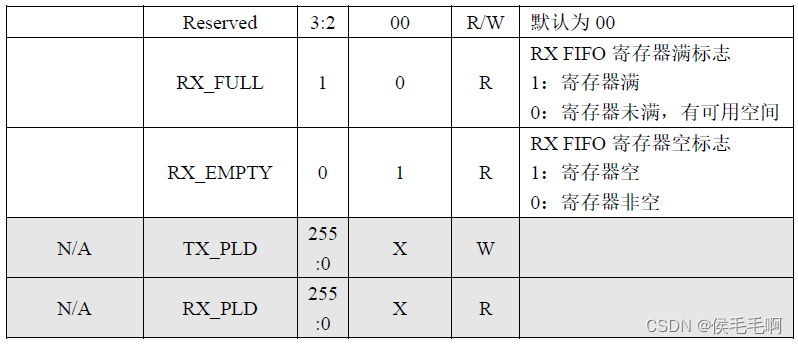

#define NRF24L01_REG_FIFO_STATUS 0x17 // FIFO status register

#define NRF24L01_REG_DYNPD 0x1C // Enable dynamic payload length

#define NRF24L01_REG_FEATURE 0x1D // Feature register// Register bits definitions

#define NRF24L01_CONFIG_PRIM_RX 0x01 // PRIM_RX bit in CONFIG register

#define NRF24L01_CONFIG_PWR_UP 0x02 // PWR_UP bit in CONFIG register

#define NRF24L01_FEATURE_EN_DYN_ACK 0x01 // EN_DYN_ACK bit in FEATURE register

#define NRF24L01_FEATURE_EN_ACK_PAY 0x02 // EN_ACK_PAY bit in FEATURE register

#define NRF24L01_FEATURE_EN_DPL 0x04 // EN_DPL bit in FEATURE register

#define NRF24L01_FLAG_RX_DREADY 0x40 // RX_DR bit (data ready RX FIFO interrupt)

#define NRF24L01_FLAG_TX_DSENT 0x20 // TX_DS bit (data sent TX FIFO interrupt)

#define NRF24L01_FLAG_MAX_RT 0x10 // MAX_RT bit (maximum number of TX re-transmits interrupt)// Register masks definitions

#define NRF24L01_MASK_REG_MAP 0x1F // Mask bits[4:0] for CMD_RREG and CMD_WREG commands

#define NRF24L01_MASK_CRC 0x0C // Mask for CRC bits [3:2] in CONFIG register

#define NRF24L01_MASK_STATUS_IRQ 0x70 // Mask for all IRQ bits in STATUS register

#define NRF24L01_MASK_RF_PWR 0x06 // Mask RF_PWR[2:1] bits in RF_SETUP register

#define NRF24L01_MASK_RX_P_NO 0x0E // Mask RX_P_NO[3:1] bits in STATUS register

#define NRF24L01_MASK_DATARATE 0x28 // Mask RD_DR_[5,3] bits in RF_SETUP register

#define NRF24L01_MASK_EN_RX 0x3F // Mask ERX_P[5:0] bits in EN_RXADDR register

#define NRF24L01_MASK_RX_PW 0x3F // Mask [5:0] bits in RX_PW_Px register

#define NRF24L01_MASK_RETR_ARD 0xF0 // Mask for ARD[7:4] bits in SETUP_RETR register

#define NRF24L01_MASK_RETR_ARC 0x0F // Mask for ARC[3:0] bits in SETUP_RETR register

#define NRF24L01_MASK_RXFIFO 0x03 // Mask for RX FIFO status bits [1:0] in FIFO_STATUS register

#define NRF24L01_MASK_TXFIFO 0x30 // Mask for TX FIFO status bits [5:4] in FIFO_STATUS register

#define NRF24L01_MASK_PLOS_CNT 0xF0 // Mask for PLOS_CNT[7:4] bits in OBSERVE_TX register

#define NRF24L01_MASK_ARC_CNT 0x0F // Mask for ARC_CNT[3:0] bits in OBSERVE_TX register// Register masks definitions

#define NRF24L01_MASK_REG_MAP 0x1F // Mask bits[4:0] for CMD_RREG and CMD_WREG commands#define NRF24L01_ADDR_WIDTH 5 // RX/TX address width

#define NRF24L01_PLOAD_WIDTH 32 // Payload width基础方法

初始化

static void NRF24L01_SPI_Init()

{GPIO_InitTypeDef GPIO_InitStruct;if(NRF24L01_SPIx == SPI1) {// A5, A6, A7RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_AFIO,ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1,ENABLE);GPIO_InitStruct.GPIO_Pin = GPIO_Pin_5 | GPIO_Pin_6 | GPIO_Pin_7;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOA, &GPIO_InitStruct);} else if(NRF24L01_SPIx == SPI2) {// B13, B14, B15RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_AFIO,ENABLE);RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI2,ENABLE);GPIO_InitStruct.GPIO_Pin = GPIO_Pin_13 | GPIO_Pin_14 | GPIO_Pin_15;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOB, &GPIO_InitStruct);}SPI_InitTypeDef SPI_InitStruct;SPI_InitStruct.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_8;SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge;SPI_InitStruct.SPI_CPOL = SPI_CPOL_Low;SPI_InitStruct.SPI_CRCPolynomial = 7;SPI_InitStruct.SPI_DataSize = SPI_DataSize_8b;SPI_InitStruct.SPI_Direction= SPI_Direction_2Lines_FullDuplex;SPI_InitStruct.SPI_FirstBit = SPI_FirstBit_MSB;SPI_InitStruct.SPI_Mode = SPI_Mode_Master;SPI_InitStruct.SPI_NSS = SPI_NSS_Soft;SPI_Init(NRF24L01_SPIx, &SPI_InitStruct);SPI_Cmd(NRF24L01_SPIx, ENABLE);

}void NRF24L01_Init(void)

{GPIO_InitTypeDef GPIO_InitStruct;RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB, ENABLE);// CE CSN InitializeGPIO_InitStruct.GPIO_Pin = NRF24L01_GPIO_CE | NRF24L01_GPIO_CSN;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_Out_PP;GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(NRF24L01_GPIOx, &GPIO_InitStruct);// IRQ InitializeGPIO_InitStruct.GPIO_Pin = NRF24L01_GPIO_IRQ;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_IPU;GPIO_Init(NRF24L01_GPIOx, &GPIO_InitStruct);NRF24L01_SPI_Init();CSN(1);

}单次读写SPI(所有交互的基础操作)

/**

* Basic SPI operation: Write to SPIx and read

*/

static u8 SPI_Write_Then_Read(u8 data)

{while(SPI_I2S_GetFlagStatus(NRF24L01_SPIx, SPI_I2S_FLAG_TXE) == RESET);SPI_I2S_SendData(NRF24L01_SPIx, data);while(SPI_I2S_GetFlagStatus(NRF24L01_SPIx, SPI_I2S_FLAG_RXNE)==RESET);return SPI_I2S_ReceiveData(NRF24L01_SPIx);

}单个字节的读写

/**

* Read a 1-bit register

*/

u8 NRF24L01_Read_Reg(u8 reg)

{u8 value;CSN(0);SPI_Write_Then_Read(reg);value = SPI_Write_Then_Read(NRF24L01_CMD_NOP);CSN(1);return value;

}/**

* Write a 1-byte register

*/

u8 NRF24L01_Write_Reg(u8 reg, u8 value)

{u8 status;CSN(0);if (reg < NRF24L01_CMD_REGISTER_W) {// This is a register accessstatus = SPI_Write_Then_Read(NRF24L01_CMD_REGISTER_W | (reg & NRF24L01_MASK_REG_MAP));SPI_Write_Then_Read(value);} else {// This is a single byte command or future command/registerstatus = SPI_Write_Then_Read(reg);if ((reg != NRF24L01_CMD_FLUSH_TX) && (reg != NRF24L01_CMD_FLUSH_RX) && (reg != NRF24L01_CMD_REUSE_TX_PL) && (reg != NRF24L01_CMD_NOP)) {// Send register valueSPI_Write_Then_Read(value);}}CSN(1);return status;

}多个字节的读写

/**

* Read a multi-byte register

* reg - register to read

* buf - pointer to the buffer to write

* len - number of bytes to read

*/

u8 NRF24L01_Read_To_Buf(u8 reg, u8 *buf, u8 len)

{CSN(0);u8 status = SPI_Write_Then_Read(reg);while (len--) {*buf++ = SPI_Write_Then_Read(NRF24L01_CMD_NOP);}CSN(1);return status;

}/**

* Write a multi-byte register

* reg - register to write

* buf - pointer to the buffer with data

* len - number of bytes to write

*/

u8 NRF24L01_Write_From_Buf(u8 reg, u8 *buf, u8 len)

{CSN(0);u8 status = SPI_Write_Then_Read(reg);while (len--) {SPI_Write_Then_Read(*buf++);}CSN(1);return status;

}RX和TX模式配置

/**

* Common configurations of RX and TX, internal function

*/

void _NRF24L01_Config(u8 *tx_addr)

{// TX AddressNRF24L01_Write_From_Buf(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_TX_ADDR, tx_addr, NRF24L01_ADDR_WIDTH);// RX P0 Payload WidthNRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_RX_PW_P0, NRF24L01_PLOAD_WIDTH);// Enable Auto ACKNRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_EN_AA, 0x3f);// Enable RX channelsNRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_EN_RXADDR, 0x3f);// RF channel: 2.400G + 0.001 * xNRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_RF_CH, 40);// 000+0+[0:1Mbps,1:2Mbps]+[00:-18dbm,01:-12dbm,10:-6dbm,11:0dbm]+[0:LNA_OFF,1:LNA_ON]// 01:1Mbps,-18dbm; 03:1Mbps,-12dbm; 05:1Mbps,-6dbm; 07:1Mbps,0dBm// 09:2Mbps,-18dbm; 0b:2Mbps,-12dbm; 0d:2Mbps,-6dbm; 0f:2Mbps,0dBm, NRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_RF_SETUP, 0x03);// 0A:delay=250us,count=10, 1A:delay=500us,count=10NRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_SETUP_RETR, 0x0a);

}/**

* Switch NRF24L01 to RX mode

*/

void NRF24L01_RX_Mode(u8 *rx_addr, u8 *tx_addr)

{CE(0);_NRF24L01_Config(tx_addr);// RX Address of P0NRF24L01_Write_From_Buf(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_RX_ADDR_P0, rx_addr, NRF24L01_ADDR_WIDTH);/**REG 0x00: 0)PRIM_RX 0:TX 1:RX1)PWR_UP 0:OFF 1:ON2)CRCO 0:8bit CRC 1:16bit CRC3)EN_CRC Enabled if any of EN_AA is high4)MASK_MAX_RT 0:IRQ low 1:NO IRQ5)MASK_TX_DS 0:IRQ low 1:NO IRQ6)MASK_RX_DR 0:IRQ low 1:NO IRQ7)Reserved 0*/NRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_CONFIG, 0x0f); //RX,PWR_UP,CRC16,EN_CRCCE(1);

}/**

* Switch NRF24L01 to TX mode

*/

void NRF24L01_TX_Mode(u8 *rx_addr, u8 *tx_addr)

{CE(0);_NRF24L01_Config(tx_addr);// On the PTX the **TX_ADDR** must be the same as the **RX_ADDR_P0** and as the pipe address for the designated pipe// RX_ADDR_P0 will be used for receiving ACKNRF24L01_Write_From_Buf(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_RX_ADDR_P0, tx_addr, NRF24L01_ADDR_WIDTH);NRF24L01_Write_Reg(NRF24L01_CMD_REGISTER_W + NRF24L01_REG_CONFIG, 0x0e); //TX,PWR_UP,CRC16,EN_CRCCE(1);

}接收和发送操作

/**

* Hold till data received and written to rx_buf

*/

u8 NRF24L01_RxPacket(u8 *rx_buf)

{u8 status, result = 0;while(IRQ);CE(0);status = NRF24L01_Read_Reg(NRF24L01_REG_STATUS);printf("Interrupted, status: %02X\r\n", status);if(status & NRF24L01_FLAG_RX_DREADY) {NRF24L01_Read_To_Buf(NRF24L01_CMD_RX_PLOAD_R, rx_buf, NRF24L01_PLOAD_WIDTH);for (int i = 0; i < 32; i++) {printf("%02X ", RX_BUF[i]);}result = 1;NRF24L01_ClearIRQFlag(NRF24L01_FLAG_RX_DREADY);}CE(1);return result;

}/**

* Send data in tx_buf and wait till data is sent or max re-tr reached

*/

u8 NRF24L01_TxPacket(u8 *tx_buf, u8 len)

{u8 status = 0x00;CE(0);len = len > NRF24L01_PLOAD_WIDTH? NRF24L01_PLOAD_WIDTH : len;NRF24L01_Write_From_Buf(NRF24L01_CMD_TX_PLOAD_W, tx_buf, len);CE(1);while(IRQ != 0); // Waiting send finishCE(0);status = NRF24L01_Read_Reg(NRF24L01_REG_STATUS);printf("Interrupted, status: %02X\r\n", status);if(status & NRF24L01_FLAG_TX_DSENT) {printf("Data sent: ");for (u8 i = 0; i < len; i++) {printf("%02X ", tx_buf[i]);}printf("\r\n");NRF24L01_ClearIRQFlag(NRF24L01_FLAG_TX_DSENT);} else if(status & NRF24L01_FLAG_MAX_RT) {printf("Sending exceeds max retries\r\n");NRF24L01_FlushTX();NRF24L01_ClearIRQFlag(NRF24L01_FLAG_MAX_RT);}CE(1);return status;

}如果需要使用中断读取, 读方法要改成非阻塞的方式, 就是上面的RX方法去掉了while IRQ的等待.

/**

* Read received data and written to rx_buf, No blocking.

*/

u8 NRF24L01_IRQ_Handler(u8 *rx_buf)

{u8 status, result = 0;CE(0);status = NRF24L01_Read_Reg(NRF24L01_REG_STATUS);printf("Reg status: %02X\r\n", status);if(status & NRF24L01_FLAG_RX_DREADY) {NRF24L01_Read_To_Buf(NRF24L01_CMD_RX_PLOAD_R, rx_buf, NRF24L01_PLOAD_WIDTH);for (int i = 0; i < 32; i++) {printf("%02X ", RX_BUF[i]);}result = 1;NRF24L01_FlushRX();NRF24L01_ClearIRQFlag(NRF24L01_FLAG_RX_DREADY);} else if(status & NRF24L01_FLAG_TX_DSENT) {printf("Data sent\r\n");NRF24L01_FlushTX();NRF24L01_ClearIRQFlag(NRF24L01_FLAG_TX_DSENT);} else if(status & NRF24L01_FLAG_MAX_RT) {printf("Sending exceeds max retries\r\n");NRF24L01_FlushTX();NRF24L01_ClearIRQFlag(NRF24L01_FLAG_MAX_RT);}CE(1);return result;

}一个非常好用的配置打印函数

/**

* Dump nRF24L01 configuration

*/

void NRF24L01_DumpConfig(void) {uint8_t i,j;uint8_t aw;uint8_t buf[5];// CONFIGi = NRF24L01_Read_Reg(NRF24L01_REG_CONFIG);printf("[0x%02X] 0x%02X MASK:%02X CRC:%02X PWR:%s MODE:P%s\r\n",NRF24L01_REG_CONFIG,i,i >> 4,(i & 0x0c) >> 2,(i & 0x02) ? "ON" : "OFF",(i & 0x01) ? "RX" : "TX");// EN_AAi = NRF24L01_Read_Reg(NRF24L01_REG_EN_AA);printf("[0x%02X] 0x%02X ENAA: ",NRF24L01_REG_EN_AA,i);for (j = 0; j < 6; j++) {printf("[P%1u%s]%s",j,(i & (1 << j)) ? "+" : "-",(j == 5) ? "\r\n" : " ");}// EN_RXADDRi = NRF24L01_Read_Reg(NRF24L01_REG_EN_RXADDR);printf("[0x%02X] 0x%02X EN_RXADDR: ",NRF24L01_REG_EN_RXADDR,i);for (j = 0; j < 6; j++) {printf("[P%1u%s]%s",j,(i & (1 << j)) ? "+" : "-",(j == 5) ? "\r\n" : " ");}// SETUP_AWi = NRF24L01_Read_Reg(NRF24L01_REG_SETUP_AW);aw = (i & 0x03) + 2;printf("[0x%02X] 0x%02X EN_RXADDR=%03X (address width = %u)\r\n",NRF24L01_REG_SETUP_AW,i,i & 0x03,aw);// SETUP_RETRi = NRF24L01_Read_Reg(NRF24L01_REG_SETUP_RETR);printf("[0x%02X] 0x%02X ARD=%04X ARC=%04X (retr.delay=%uus, count=%u)\r\n",NRF24L01_REG_SETUP_RETR,i,i >> 4,i & 0x0F,((i >> 4) * 250) + 250,i & 0x0F);// RF_CHi = NRF24L01_Read_Reg(NRF24L01_REG_RF_CH);printf("[0x%02X] 0x%02X (%.3uGHz)\r\n",NRF24L01_REG_RF_CH,i,2400 + i);// RF_SETUPi = NRF24L01_Read_Reg(NRF24L01_REG_RF_SETUP);printf("[0x%02X] 0x%02X CONT_WAVE:%s PLL_LOCK:%s DataRate=",NRF24L01_REG_RF_SETUP,i,(i & 0x80) ? "ON" : "OFF",(i & 0x80) ? "ON" : "OFF");switch ((i & 0x28) >> 3) {case 0x00:printf("1M");break;case 0x01:printf("2M");break;case 0x04:printf("250k");break;default:printf("???");break;}printf("pbs RF_PWR=");switch ((i & 0x06) >> 1) {case 0x00:printf("-18");break;case 0x01:printf("-12");break;case 0x02:printf("-6");break;case 0x03:printf("0");break;default:printf("???");break;}printf("dBm\r\n");// STATUSi = NRF24L01_Read_Reg(NRF24L01_REG_STATUS);printf("[0x%02X] 0x%02X IRQ:%03X RX_PIPE:%u TX_FULL:%s\r\n",NRF24L01_REG_STATUS,i,(i & 0x70) >> 4,(i & 0x0E) >> 1,(i & 0x01) ? "YES" : "NO");// OBSERVE_TXi = NRF24L01_Read_Reg(NRF24L01_REG_OBSERVE_TX);printf("[0x%02X] 0x%02X PLOS_CNT=%u ARC_CNT=%u\r\n",NRF24L01_REG_OBSERVE_TX,i,i >> 4,i & 0x0F);// RPDi = NRF24L01_Read_Reg(NRF24L01_REG_RPD);printf("[0x%02X] 0x%02X RPD=%s\r\n",NRF24L01_REG_RPD,i,(i & 0x01) ? "YES" : "NO");// RX_ADDR_P0NRF24L01_Read_To_Buf(NRF24L01_REG_RX_ADDR_P0,buf,aw);printf("[0x%02X] RX_ADDR_P0 \"",NRF24L01_REG_RX_ADDR_P0);for (i = 0; i < aw; i++) printf("%X ",buf[i]);printf("\"\r\n");// RX_ADDR_P1NRF24L01_Read_To_Buf(NRF24L01_REG_RX_ADDR_P1,buf,aw);printf("[0x%02X] RX_ADDR_P1 \"",NRF24L01_REG_RX_ADDR_P1);for (i = 0; i < aw; i++) printf("%X ",buf[i]);printf("\"\r\n");// RX_ADDR_P2printf("[0x%02X] RX_ADDR_P2 \"",NRF24L01_REG_RX_ADDR_P2);for (i = 0; i < aw - 1; i++) printf("%X ",buf[i]);i = NRF24L01_Read_Reg(NRF24L01_REG_RX_ADDR_P2);printf("%X\"\r\n",i);// RX_ADDR_P3printf("[0x%02X] RX_ADDR_P3 \"",NRF24L01_REG_RX_ADDR_P3);for (i = 0; i < aw - 1; i++) printf("%X ",buf[i]);i = NRF24L01_Read_Reg(NRF24L01_REG_RX_ADDR_P3);printf("%X\"\r\n",i);// RX_ADDR_P4printf("[0x%02X] RX_ADDR_P4 \"",NRF24L01_REG_RX_ADDR_P4);for (i = 0; i < aw - 1; i++) printf("%X ",buf[i]);i = NRF24L01_Read_Reg(NRF24L01_REG_RX_ADDR_P4);printf("%X\"\r\n",i);// RX_ADDR_P5printf("[0x%02X] RX_ADDR_P5 \"",NRF24L01_REG_RX_ADDR_P5);for (i = 0; i < aw - 1; i++) printf("%X ",buf[i]);i = NRF24L01_Read_Reg(NRF24L01_REG_RX_ADDR_P5);printf("%X\"\r\n",i);// TX_ADDRNRF24L01_Read_To_Buf(NRF24L01_REG_TX_ADDR,buf,aw);printf("[0x%02X] TX_ADDR \"",NRF24L01_REG_TX_ADDR);for (i = 0; i < aw; i++) printf("%X ",buf[i]);printf("\"\r\n");// RX_PW_P0i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P0);printf("[0x%02X] RX_PW_P0=%u\r\n",NRF24L01_REG_RX_PW_P0,i);// RX_PW_P1i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P1);printf("[0x%02X] RX_PW_P1=%u\r\n",NRF24L01_REG_RX_PW_P1,i);// RX_PW_P2i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P2);printf("[0x%02X] RX_PW_P2=%u\r\n",NRF24L01_REG_RX_PW_P2,i);// RX_PW_P3i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P3);printf("[0x%02X] RX_PW_P3=%u\r\n",NRF24L01_REG_RX_PW_P3,i);// RX_PW_P4i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P4);printf("[0x%02X] RX_PW_P4=%u\r\n",NRF24L01_REG_RX_PW_P4,i);// RX_PW_P5i = NRF24L01_Read_Reg(NRF24L01_REG_RX_PW_P5);printf("[0x%02X] RX_PW_P5=%u\r\n",NRF24L01_REG_RX_PW_P5,i);

}STM32F401CCU6

STM32F4可用的SPI口

| SPI1 | SPI2 | SPI3 | SPI4 | |||||

|---|---|---|---|---|---|---|---|---|

| NSS | PA4 | PA15 | PB12 | PB9 | PA15 | PA4 | PE4 | PE11 |

| SCK | PA5 | PB3 | PB13 | PB10 | PC10 | PB3 | PE2 | PE12 |

| MISO | PA6 | PB4 | PB14 | PC2 | PC11 | PB4 | PE5 | PE13 |

| MOSI | PA7 | PB5 | PB15 | PC3 | PC12 | PB5 | PE6 | PE14 |

连接方式与STM32F103相同. 唯一区别是初始化方式

static void NRF24L01_SPI_Init()

{GPIO_InitTypeDef GPIO_InitStructure;if(NRF24L01_SPIx == SPI1) {RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1, ENABLE);// SCK:PA5, MISO:PA6, MOSI:PA7 or PB3, PB4, PB5GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5|GPIO_Pin_6|GPIO_Pin_7;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF;GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP;GPIO_Init(GPIOA, &GPIO_InitStructure);GPIO_PinAFConfig(GPIOA, GPIO_PinSource5, GPIO_AF_SPI1);GPIO_PinAFConfig(GPIOA, GPIO_PinSource6, GPIO_AF_SPI1);GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_SPI1);RCC_APB2PeriphResetCmd(RCC_APB2Periph_SPI1, ENABLE); // reset SPI1RCC_APB2PeriphResetCmd(RCC_APB2Periph_SPI1, DISABLE);// stop reset SPI1} else if(NRF24L01_SPIx == SPI2) {// B13, B14, B15RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOB, ENABLE);RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI2, ENABLE);} else { // SPI3,4,5,6RCC_APB1PeriphResetCmd(RCC_APB1Periph_SPI3, ENABLE);}SPI_InitTypeDef SPI_InitStructure;SPI_StructInit(&SPI_InitStructure); // set default settings SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_8;SPI_InitStructure.SPI_CPHA = SPI_CPHA_1Edge; // data sampled at first edgeSPI_InitStructure.SPI_CPOL = SPI_CPOL_Low; // clock is low when idleSPI_InitStructure.SPI_CRCPolynomial = 7;SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b; // one packet of data is 8 bits wideSPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex; // set to full duplex mode, seperate MOSI and MISO linesSPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB; // data is transmitted MSB firstSPI_InitStructure.SPI_Mode = SPI_Mode_Master; // transmit in master mode, NSS pin has to be always highSPI_InitStructure.SPI_NSS = SPI_NSS_Soft; // set the NSS management to internal and pull internal NSS highSPI_Init(NRF24L01_SPIx, &SPI_InitStructure);SPI_Cmd(NRF24L01_SPIx, ENABLE);}void NRF24L01_Init(void)

{RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOB, ENABLE);GPIO_InitTypeDef GPIO_InitStructure;GPIO_InitStructure.GPIO_Pin = NRF24L01_GPIO_CE|NRF24L01_GPIO_CSN;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT;GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL;GPIO_Init(NRF24L01_GPIOx, &GPIO_InitStructure);// IRQ InitializeGPIO_InitStructure.GPIO_Pin = NRF24L01_GPIO_IRQ;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN;GPIO_Init(NRF24L01_GPIOx, &GPIO_InitStructure);NRF24L01_SPI_Init();/*CSN is high initially (active low).CE is low initially (active high).*/CSN(1);printf("## nRF24L01 Initialized ##\r\n");

}在STM32F401CCU6上, 使用中断进行接收的例子

void EXTILine13_Config(void)

{RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOB, ENABLE);/* Enable SYSCFG clock */RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);GPIO_InitTypeDef GPIO_InitStructure;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN;GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL;GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13;GPIO_Init(GPIOB, &GPIO_InitStructure);/* Connect EXTI Line13 to PG13 pin */SYSCFG_EXTILineConfig(EXTI_PortSourceGPIOB, EXTI_PinSource13);EXTI_InitTypeDef EXTI_InitStructure;EXTI_InitStructure.EXTI_Line = EXTI_Line13;EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling;EXTI_InitStructure.EXTI_LineCmd = ENABLE;EXTI_Init(&EXTI_InitStructure);NVIC_InitTypeDef NVIC_InitStructure;NVIC_InitStructure.NVIC_IRQChannel = EXTI15_10_IRQn;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x01; NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x01;NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);

}void EXTI15_10_IRQHandler(void) {printf("EXTI15_10_IRQHandler\r\n");/* Make sure that interrupt flag is set */if (EXTI_GetITStatus(EXTI_Line13) != RESET) {NRF24L01_IRQ_Handler(RX_BUF);/* Clear interrupt flag */EXTI_ClearITPendingBit(EXTI_Line13);}

}int main(void)

{Systick_Init();USART1_Init();NRF24L01_Init();NRF24L01_DumpConfig();while(NRF24L01_Check() != 0) {printf("nRF24L01 check failed\r\n");Systick_Delay_ms(2000);}printf("nRF24L01 check succeeded\r\n");printf("nRF24L01 in RECEIVE mode\r\n");NRF24L01_RX_Mode(RX_ADDRESS, TX_ADDRESS);LED_Init();EXTILine13_Config();while(1) {}

}STC89C52

51单片机的连接方式

sbit CE = P1^5;

sbit CSN= P1^4;

sbit SCK= P1^3;

sbit MOSI= P1^2;

sbit MISO= P1^1;

sbit IRQ = P1^0;常量定义

// SPI(nRF24L01) commands

#define READ_REG 0x00 // Define read command to register

#define WRITE_REG 0x20 // Define write command to register

#define RD_RX_PLOAD 0x61 // Define RX payload register address

#define WR_TX_PLOAD 0xA0 // Define TX payload register address

#define FLUSH_TX 0xE1 // Define flush TX register command

#define FLUSH_RX 0xE2 // Define flush RX register command

#define REUSE_TX_PL 0xE3 // Define reuse TX payload register command

#define NOP 0xFF // Define No Operation, might be used to read status register// SPI(nRF24L01) registers(addresses)

#define CONFIG 0x00 // 'Config' register address

#define EN_AA 0x01 // 'Enable Auto Acknowledgment' register address

#define EN_RXADDR 0x02 // 'Enabled RX addresses' register address

#define SETUP_AW 0x03 // 'Setup address width' register address

#define SETUP_RETR 0x04 // 'Setup Auto. Retrans' register address

#define RF_CH 0x05 // 'RF channel' register address

#define RF_SETUP 0x06 // 'RF setup' register address

#define STATUS 0x07 // 'Status' register address

#define OBSERVE_TX 0x08 // 'Observe TX' register address

#define CD 0x09 // 'Carrier Detect' register address

#define RX_ADDR_P0 0x0A // 'RX address pipe0' register address

#define RX_ADDR_P1 0x0B // 'RX address pipe1' register address

#define RX_ADDR_P2 0x0C // 'RX address pipe2' register address

#define RX_ADDR_P3 0x0D // 'RX address pipe3' register address

#define RX_ADDR_P4 0x0E // 'RX address pipe4' register address

#define RX_ADDR_P5 0x0F // 'RX address pipe5' register address

#define TX_ADDR 0x10 // 'TX address' register address

#define RX_PW_P0 0x11 // 'RX payload width, pipe0' register address

#define RX_PW_P1 0x12 // 'RX payload width, pipe1' register address

#define RX_PW_P2 0x13 // 'RX payload width, pipe2' register address

#define RX_PW_P3 0x14 // 'RX payload width, pipe3' register address

#define RX_PW_P4 0x15 // 'RX payload width, pipe4' register address

#define RX_PW_P5 0x16 // 'RX payload width, pipe5' register address

#define FIFO_STATUS 0x17 // 'FIFO Status Register' register address基础方法

void init_io(void)

{CE = 0; // 待机CSN = 1; // SPI禁止SCK = 0; // SPI时钟置低IRQ = 1; // 中断复位LED = 1; // 关闭指示灯

}void delay_ms(uchar x)

{uchar i, j;i = 0;for(i=0; i<x; i++) {j = 250;while(--j);j = 250;while(--j);}

}uchar SPI_RW(uchar byte)

{uchar i;for(i=0; i<8; i++) {MOSI = (byte & 0x80); // byte最高位输出到MOSIbyte <<= 1; // 左移一位SCK = 1; // 拉高SCK,nRF24L01从MOSI读入1位数据,同时从MISO输出1位数据byte |= MISO; // 读MISO到byte最低位SCK = 0; // SCK置低}return byte;

}uchar SPI_RW_Reg(uchar reg, uchar value)

{uchar status;CSN = 0; // CSN置低,开始传输数据status = SPI_RW(reg); // 选择寄存器,同时返回状态字SPI_RW(value); // 然后写数据到该寄存器CSN = 1; // CSN拉高,结束数据传输return(status); // 返回状态寄存器

}uchar SPI_Read(uchar reg)

{uchar reg_val;CSN = 0; // CSN置低,开始传输数据SPI_RW(reg); // 选择寄存器reg_val = SPI_RW(0); // 然后从该寄存器读数据CSN = 1; // CSN拉高,结束数据传输return(reg_val); // 返回寄存器数据

}uchar SPI_Read_Buf(uchar reg, uchar * pBuf, uchar bytes)

{uchar status, i;CSN = 0; // CSN置低,开始传输数据status = SPI_RW(reg); // 选择寄存器,同时返回状态字for(i=0; i<bytes; i++)pBuf[i] = SPI_RW(0); // 逐个字节从nRF24L01读出CSN = 1; // CSN拉高,结束数据传输return(status); // 返回状态寄存器

}uchar SPI_Write_Buf(uchar reg, uchar * pBuf, uchar bytes)

{uchar status, i;CSN = 0; // CSN置低,开始传输数据status = SPI_RW(reg); // 选择寄存器,同时返回状态字for(i=0; i<bytes; i++)SPI_RW(pBuf[i]); // 逐个字节写入nRF24L01CSN = 1; // CSN拉高,结束数据传输return(status); // 返回状态寄存器

}参考资料

- 这是一个综合的介绍 https://www.playembedded.org/blog/a-radio-frequency-transceiver-library-nrf24l01-and-chibiosrt/

- SPI初始化和方法, 与目录中的

NRF24L01_STM32_code和STM32F103-Example结合着看, 模块部分都是正点原子的代码https://blog.csdn.net/weixin_45555616/article/details/110501179 - 另一篇带源码的说明https://www.cnblogs.com/whlook/p/5967156.html

- 这篇对24L01的工作机制有描述https://www.cnblogs.com/mr-bike/p/3520141.html

- https://github.com/elmot/nrf24l01-lib/blob/master/nrf24l01/nrf24.h

- 用外部中断处理IRQhttps://github.com/r2aiv/NRF24L01-1/blob/master/inc/nrf24l01.hhttps://stackoverflow.com/questions/25932299/stm32-rising-and-falling-button-interrupt-detection

- 8051操作nRF24L01 https://blog.csdn.net/fzf1996/article/details/90601375

- 8051 https://blog.csdn.net/wzk456/article/details/78948122

- 8051 http://www.51hei.com/bbs/dpj-92127-1.html

- 8051 http://www.51hei.com/bbs/dpj-135749-1.html

- STM32F4的库文件 https://github.com/MaJerle/stm32f429/blob/master/00-STM32F429_LIBRARIES/tm_stm32f4_nrf24l01.c

- https://stm32f4-discovery.net/2014/06/library-17-nrf24l01-stm32f4xx/

- https://github.com/knielsen/stm32f4_wireless_bootloader/blob/master/wireless_bootloader.c

- https://github.com/AmberHan/STM32F4_Send/blob/main/终端设备A1/HARDWARE/NRF24L01/24l01.c