数字系统的测试与可测试设计(DFT)

- 背景介绍

- 1 Defects

- 1.1 名词解释

- 1.2 缺陷种类

- 1.2.1 Physical Defects物理缺陷

- 1.2.2 Shorting Defects

- 1.2.2.1 Gate-Oxide-Shorts

- 1.2.2.2 Bridge

- 1.2.2.1 Open

- 1.2.2.1 Post-fabrication failures

- 2 Fault Modelling(故障模型)

- 2.1 Behavioural level fault model

- 2.2 Functional level fault model

- 2.3 Structural level fault model

- 2.3.1 SAF

- 2.3.2 SSAF

- 2.3.3 MSAF

- 2.3.4 Bridging fault models

- 2.4 Programmable Logic Arrays (PLA) Faults

- 2.5 Switch Level Fault

- 2.5.1 与非门、或非门MOS管电路

- 2.5.2 Stuck-Open fault Model

- 2.5. 3 Stuck-short fault Model

- 2.5.4 建模

- 2.6 Geometric Level fault Model

- 2.7 其他模型

- 2.8 等效故障

- 2.8.1 简单的等效故障

- 2.8.2 例子

- 2.9 功能等效

- 2.10 Fault Dominance

- 2.11 检查点

- 3 D算法

- 4 可测试性设计

- 4.1 扫描设计技术(SCAN PATH)

- 4.2 边界扫描

背景介绍

可测性设计即通过在芯片设计过程中引入测试逻辑,并利用这部分测试逻辑完成测试向量的自动生成,从而达到快速筛选量产芯片的目的。在设计中,通过在芯片初始输入端给定特定的值来测试芯片初始输出端的输出值是否与期望值相符来确定内部电路是否可以正常工作。

具体工作内容包括:

- 在芯片设计前期参与DFT架构规划

- 在RTL级别设计测试电路

- 在验证阶段验证测试电路

- 在综合阶段实现测试逻辑的插入

- 在测试阶段提供无时序问题的仿真测试向量

- 在ATE阶段协助ATE工程师调试测试向量,尽快帮助芯片Bring up,并帮助Slilcon learing及fauilure analysis。

1 Defects

1.1 名词解释

-

defects:中文翻译为缺陷,缺陷是在实际硬件和设计之间的差异。

以一个2输入与门为例:

假如b和GND之间短路了,那这个短路就是defect,缺陷。

-

fault:因为defect引起的电路的表现称为fault,故障。

因为短路,引起b的输入一直为0,这就是fault。

-

errors:因为缺陷引起的不正确的结果就成为error,错误。

因为短路,所以在ab输入为11的时候,c的输出为0,正确的情况应该是1,这就是error。

需要注意的是,error不是一直存在的,只要a和b的输入任一为0 ,这样c的输出的就是0,这时候error就消失了 -

Failure Mechanisms: 故障机制,描述了产生缺陷的过程。

确定一个缺陷是有什么原因引起的很重要:

比如:- 氧化层击穿

- 电迁移

- 接触不良

等。这些机制与制造过程中的变化有关:

- 实际环境中的随机波动,例如,用于扩散和氧化的气体湍流。

- 炉子控制不正确。

- 材料的物理和化学参数的变化,例如,光刻胶的密度和粘度的波动。水和气体污染物。

-

可测性设计故障模型

为了检测到芯片电路中的故障,1959年Eldred提出了故障模型的概念,即一个试着捕获物理缺陷对电路行为的逻辑功能的影响的结构模型。从那之后,固定型故障模型被用来生成高效的测试向量集

1.2 缺陷种类

1.2.1 Physical Defects物理缺陷

- 多余或者缺少材料

可能是由于掩模,晶圆表面或加工化学品上的灰尘颗粒引起的,比如光刻胶。

在光刻过程中,这些颗粒会导致某些地方会没有曝光到,从而导致:- 多余的材料或材料的不必要蚀刻

- 在多晶硅,活性或金属层中造成短路和开路

- Gate-Oxide-Shorts

这是一种比较常见的缺陷,主要原因有以下几点:- Si和SiO2界面处的氧气不足

- 化学污染

- 场氧化过程中的氮化物开裂

- 晶体缺陷

- 薄氧化层的均匀生长图案中的缺陷

- 薄氧化膜中的颗粒污染

-------------------------------------生产操作流程中-------------------------------------------- - 由于按比例缩放特征尺寸而没有按比例缩放电源电压而导致的电场应力

- 静电放电(ESD)

- 由热电子引入的电荷陷阱

- 时变介电击穿(TDDB)效应

- Electromigration:

互连中的主要故障机制之一。

1.2.2 Shorting Defects

比较可能发生短路的地方,不同的地方会有不同的名字:

-

金属线与VDD或VSS之间

-

子网之间作为 bridging defects(桥接缺陷)

-

以及作为Gate-Oxide-Shorts(GOS)到达晶体管的源极,漏极或沟道区域

-

通过寄生晶体管泄漏和有缺陷的pn结

故障行为的类型取决于:

- 短路的位置(栅极到通道与栅极到源极/漏极)

- 受影响的晶体管的类型(n或p)

- 短路电阻和电阻驱动晶体管的状态

1.2.2.1 Gate-Oxide-Shorts

1.2.2.2 Bridge

1.2.2.1 Open

1.2.2.1 Post-fabrication failures

IC可能会在其生命周期的不同阶段发生故障:

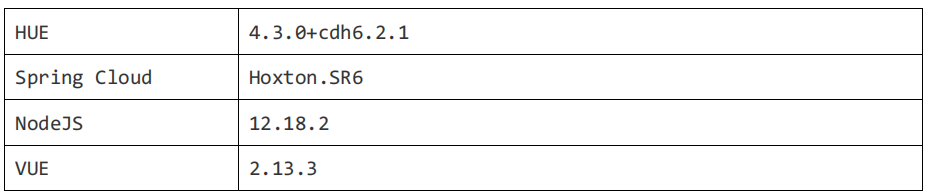

2 Fault Modelling(故障模型)

为了检测到芯片电路中的故障,1959年Eldred提出了故障模型的概念,即一个试着捕获物理缺陷对电路行为的逻辑功能的影响的结构模型。从那之后,固定型故障模型被用来生成高效的测试向量集

2.1 Behavioural level fault model

实际上就是用VHDL或者Verilog语言描述出故障模型,这类模型跟实际电路和生产制造的关系不大,常用于仿真测试中。

2.2 Functional level fault model

常用于模块之间的故障模型:

比如选择器,译码器,RAM等

对于某些类型的模块可能非常有效,并且可以以很少的工作量直接生成测试集。

2.3 Structural level fault model

故障模型( fault model )是用逻辑模型来表示物理缺陷的结果。

2.3.1 SAF

粘固故障模型(Stuck-At fault model),简称SAF模型仍然是当今最流行的故障模型。

因为成本的问题,测试SAF的规则是不可以用内部探针,只能用输入、输出端口对IC进行测试。

由于故障,导致A接口引脚一直为0,称为 A s-a-0 or A/0,相反,称为 A s-a-1 or A/1。

SAF例子

使用2输入与非门实现2输入XOR功能

在这个电路中有12个测试点,因此,对应有24个故障模型

2.3.2 SSAF

做测试时,假设芯片中只有单个SAF(Single SAF,简称SSAF)。

对于SSAF模型,假设电路中有K个测试点,那么他的故障模型就有2K种。

当然,芯片中有可能会出现多个故障的情况,但要同时测试芯片的多个故障将大大增加测试的时间,使用SSAF模型的假设可以减少测试时间和测试向量。

SSAF例子

2.3.3 MSAF

上面讲了当个SAF,那肯定会有多个SAF(Multiple Stuck-at fault model,简称MSAF)。

这时候,当电路有K个测试点,那么故障就有

个,其中不考虑所有线路故障。

当然,这里使用SAF模型可以检测到大部分的MSAF故障。

2.3.4 Bridging fault models

桥接故障模型是由于两根或更多根导线一起短路引起的,如下图:

为了检测“与”桥接,桥接中涉及的线路之一被复制为0,而其他则被复制为1。

2.4 Programmable Logic Arrays (PLA) Faults

在PLA中建模了三种类型的故障:

- Stuck-at faults on inputs and outputs.

- Cross-point faults – 这些发生在产品线与输入或输出线交叉的点

基于它们对乘积项立方体的影响(如卡诺图所示),AND平面中缺少的交叉点称为生长缺陷。 AND平面中的额外交叉点称为收缩故障。 - Bridging faults

2.5 Switch Level Fault

2.5.1 与非门、或非门MOS管电路

NAND

nor

在这个模型中,我们考虑两种类型的开关级故障模型:

- Stuck-open fault(断路故障):晶体管永不导通

- Stuck-short fault(短路故障):晶体管始终导通(源极和漏极短路)

2.5.2 Stuck-Open fault Model

由于某些故障,晶体管永久不导通,门输出可能取决于其先前状态(组合电路可能会表现出顺序行为),因此,单个测试模式无法区分故障,因此需要一系列模式(2模式测试),将给定的单个固定故障测试集的测试向量重新排列以满足2模式测试。

当A = 0和B = 0时,如果没有故障,输出F将为1,

出现故障时,输出为浮动状态,输出为浮动状态,并且F处的电压将取决于负载电容器中存储的电荷

我们应用两种模式

• A=1 and B=0 to initialise F=0

• A=0 and B=0 to sensitize the fault

完整的测试由两个向量10→00组成,它们产生一个输出

正常电路中为0→1,故障电路中为0→0

2.5. 3 Stuck-short fault Model

晶体管由于某些故障而永久导通,这时检查输出的逻辑值还不够,因为可能会导致输出达到某个不确定的水平。 并且高电流将从VDD流向GND,

要检测这种类型的故障,我们需要监视电流,称为𝐼𝐷𝐷𝑄 𝑡𝑒𝑠𝑡𝑖𝑛g。

Consider T1 Stuck at short fault

•当A = 1且B = 0时,在没有故障的情况下输出F将为0(下拉网络导通)

•在出现故障时,上拉网络也开始导通,导致高电流从VDD到GND

•输出F不确定(表示为X)

2.5.4 建模

电源节点(VDD接地)之间的晶体管的每个串联互连都被与门取代,

并行互连被“或”门(通过反转的pMOS输入)代替,

输出是由具有给定真值表的BUS网络产生的,

-

stuck-open Fault:

- pmos 晶体管就假设 s-a-1

- nmos 假设 s-a-0

-

stuck-short Fault

- pmos 晶体管就假设 s-a-0

- nmos 假设 s-a-1

2.6 Geometric Level fault Model

Stuck-short fault Model:

➢ 电路描述在布局级别指定

作为不同层上的矩形形状的集合

➢ 故障模型是临时的,可以直接从布局中得出

Example: bridging fault between a pair of lines that are running parallel to each other

➢ 一些功能故障模型依赖于几何信息

PLA fault model, memory fault model, etc.

2.7 其他模型

2.8 等效故障

布尔电路的两个故障称为Fault Equivalence(等效故障),如果它们对电路进行转换,以使两个故障电路具有相同的输出功能。等效故障也称为不可区分的,并且具有完全相同的测试集。

2.8.1 简单的等效故障

2.8.2 例子

2.9 功能等效

在某些电路中,有时候相同的故障模型会导致相同的结果,对于输出结果相同的故障模型,只需考虑一种,如下:

2.10 Fault Dominance

如果某个故障F1的所有测试都检测到另一个故障F2,则称F2占主导地位。

如果检测到F2的所有测试集𝑇𝐹1是测试集𝑇𝐹1的子集,则故障F1将主导另一个故障F2。

如果两个故障相互主导,则它们是等效的.

例如,“与非”门输入A的SA1测试(F2)也会在输出上检测到SA0(F1)(对于输入B同样如此)。因此,可以从列表中删除Z-SA0。

Fault Dominance Examples:

2.11 检查点

组合电路的主要输入和扇出分支称为检查点

检查点定理:一个测试设备,可以检测组合电路的所有检查点上的所有单个(多个)固定故障,也可以检测该电路中的所有单个(多个)固定故障。

3 D算法

D算法是由IBM提出测试SAF的,是比较广泛的使用来探测SAF的一种算法。

在D算法里,有五个符号,分别是

其中,𝐷表示在无故障(正常)条件下为逻辑1,在故障条件下为逻辑0的节点。

D(上划线)则表示无故障(正常)条件下为逻辑0,在故障条件下为逻辑1的节点,

X是一个不确定值。

使用D算法主要有3个步骤:

- 先将故障传播到其中一个输出,

- 然后反向传播到输入获得一致的输入分配

- 如果冲突了就后退

说道D算法,里面有四种写法:

-

. SC

门(或任何电路元件)的单覆盖(SC)是真值表的一种紧凑形式。(显示卡诺图基本素蕴涵的最小输入信号分配集)

-

. Primitive D-Cube of Failure (PDCF)

指定最小输入条件,以在门输出处产生错误

-

Propagation D-Cube:

以2输入与门为例

- D-intersection

4 可测试性设计

4.1 扫描设计技术(SCAN PATH)

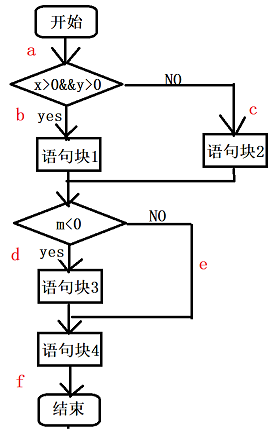

这是一个时序电路,

使用扫描,同步时序电路在两种模式下工作:(正常模式和测试模式)

在测试模式下:

通过用一个可扫描的等效物替换设计中所有的存储器元件,然后把这些扫描单元连接为扫描链,利用多个时钟脉冲将特定的输入值一拍一拍打入到扫描链上所有的时序触发器,同时在扫描输出端通过多个时钟脉冲得到这些触发器的测试响应。将得到测测试响应值与工具给定的期望响应值对比可以帮助快速找到发生缺陷的位置,实现对量产芯片的筛选。这一方法通过控制和观察设计中所有存储元件的值,从而使得时序电路的测试向量生成和仿真变得和组合逻辑一样简单。

4.2 边界扫描

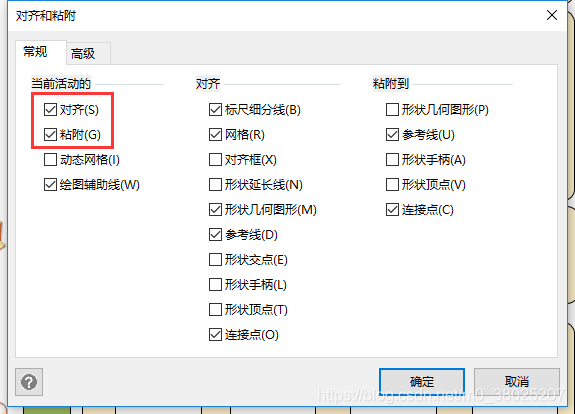

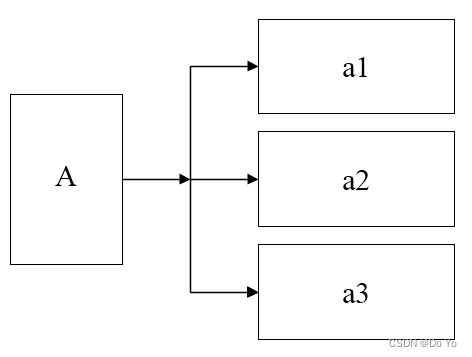

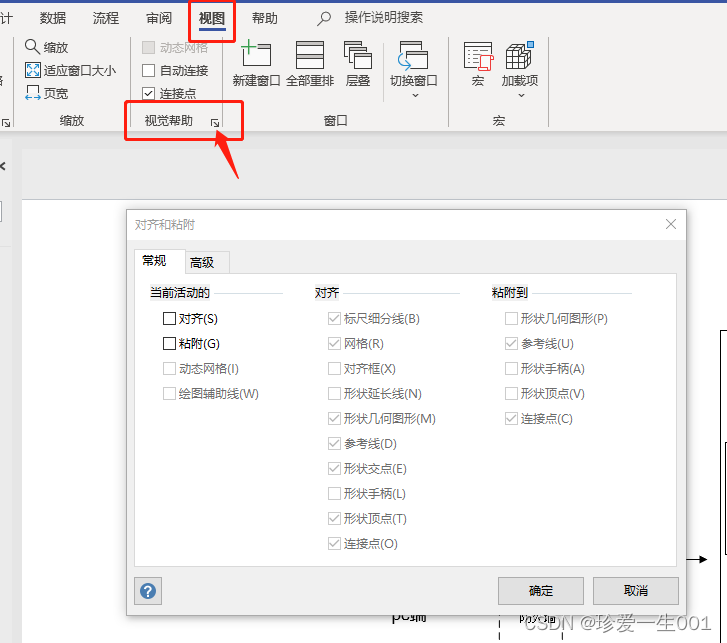

上图给出了多个器件相连接的JTAG测试:系统的测试总线TCK和TMS共享给电路中所有需要测试的器件,这些信号由TAP控制器统一控制,第一个器件的输入端作为整个测试的整体输入端,前级器件的输出作为后级器件的输入,最后一个器件的输出端作为整个测试的整体输出端,通过这种方式将所有待测器件的引脚连接起来,测试者可以通过给定输入端特定的输入值并为各输出端设定对应的期望值,通过比较输出端实际测到的值是否与期望值相符来确定电路是否存在缺陷,达到测试芯片的目的。