https://blog.csdn.net/vivid117/article/details/100187137

pmos,nmos宽长比https://blog.csdn.net/qq_34070723/article/details/89291200

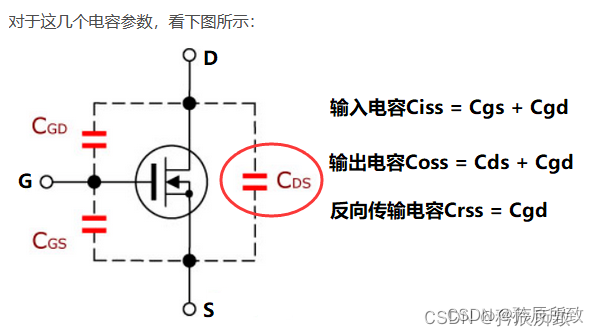

cmos宽长比:

1.CMOS的宽长比

关于COMS原理及结构图可以参考[1]COMS原理及门电路设计.

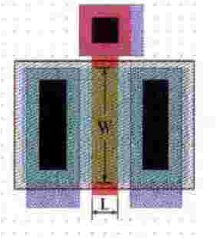

栅在源漏方向的长度称作栅的长L,垂直方向称为栅的宽W,如图1中NMOS的版图。

图1

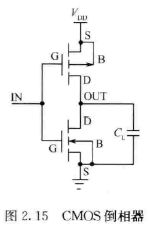

以MOS管的倒向器为例,其PMOS与NMOS的宽长比满足公式:

其中uN与uP指相应的载流子迁移率,倒向器的载流子迁移率中若uN/uP=2.5即PMOS的宽长比是NMOS的2.5倍.(图2.15中是看不出来的),事实上宽长比涉及的公式比较多,但作为设计工程师只需要理解到我说的就可以了。

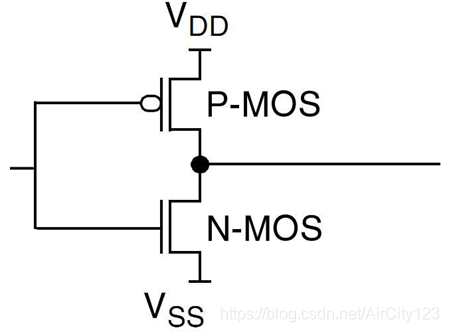

图2.16中的与非门中,根据频率要求和有关参数计算获得等效倒相器的NMOS和PMOS的宽长比和,考虑到M3和M4是串联结构,为保持下降时间不变(倒向器的电阻不变),M3和M4的等效电阻必须缩小一半,即它们的宽长比必须比倒相器中的NMOS的宽长比增加一倍(等效电阻与宽长比成反比),由此得到,而M1和M2是并联,宽长比却不是变为一半,原因是并联的只要一个导通其的电阻就和倒向器的一样了,所以是。同理,或非门的M1,M2是2倍,M3,M4是1倍[2]。

问题:为什么一个标准的倒相器中 P 管的宽长比要比 N 管的宽长比大?

和载流子有关, P 管是空穴导电, N 管是电子导电, 电子的迁移率大于空穴, 同样的电场下, N 管的电流大于 P 管, 因此要增大 P 管的宽长比, 使之对称, 这样才能使得两者上升时间下降时间相等、 高低电平的噪声容限一样、 充电放电的时间相等。

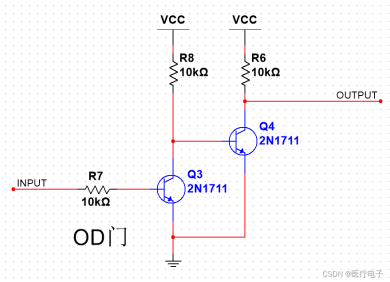

一、OD门介绍

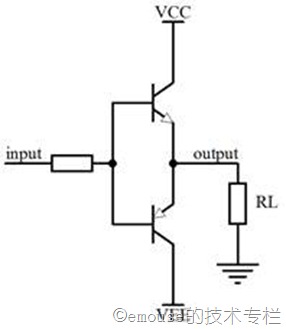

OC(Open Collector)门,又称集电极开路,OD(Open Drain)漏极开路,通过名称就可以判断,OC门是针对三极管来说的,而OD门是针对MOS管而言的。

管子的栅极和输入连接,源极接公共端,漏极悬空(开路)什么也没有接,因此使用时需要接一个适当阻值的电阻到电源,才能使这个管子正常工作,这个电阻就叫上拉电阻。

线与逻辑:即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

通常CMOS门电路都有反相器作为输出缓冲电路,如上图所示,如果将两个CMOS与非门G1和G2的输出端连接在一起,并设G1的输出处于高电平,TN1截止,TP1导通;而G2的输出处于低电平,TN2导通,TP2截止,这样从G1的TP1端到G2的TN2端将形成一低阻通路,从而产生很大的电流,很有可能导致器件的损毁,并且无法确定输出是高电平还是低电平。

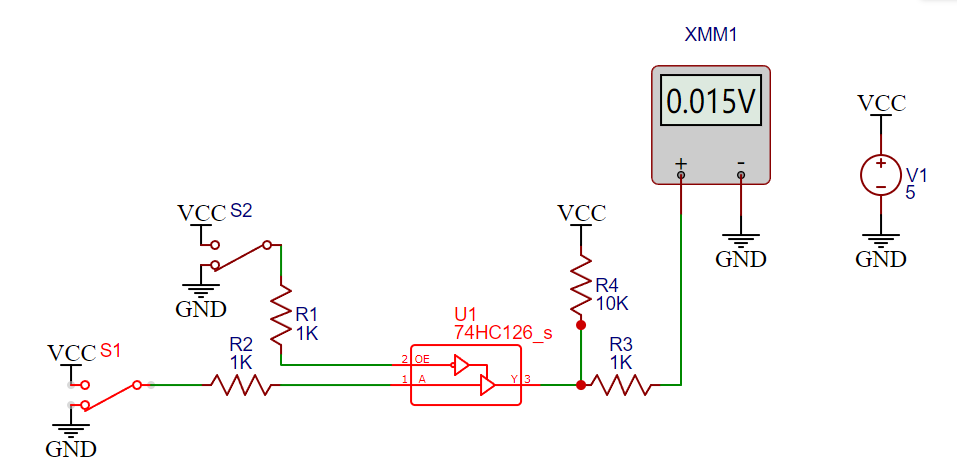

漏极开路门(OD门)是指CMOS门电路的输出只有NMOS管,并且它的漏极是开路的。使用OD门时必须在漏极和电源VDD之间外接一个上拉电阻(pull-up resister)RP。如图2所示为两个OD与非门实现线与,将两个门电路输出端接在一起,通过上拉电阻接电源。

可以看出,OD门就是将反相器的上面的pmos管拿掉了而已。任何一个nmos管导通,L电平被拉低,L=0;

当两个与非门的输出全为1时,输出为1;只要其中一个输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)'(CD)'。

上拉电阻对OD门动态性能的影响:

当其他门电路作为OD门的负载时,OD门称为驱动门,其后所接的门电路称为负载门。由于驱动门的输出电容、负载门的输入电容以及接线电容的存在,上拉电阻势必影响OD门的开关速度,RP的值越小,负载电容的充电时间常数也越小,因而开关速度越快。但上拉电阻不能任意的减小,它必须保证OD门输出端的电流不能超过允许的最大值IOL(max)。对于74HC/74HCT系列CMOS电路,IOL(max)=4 mA,因此RP必须大于VDD/IOL(max)=5 V/4 mA = 1.25kΩ 。与普通CMOS电路相比,RP的值比PMOS管导通电阻大,因而,OD门从低电平到高电平的转换速度比普通CMOS门慢。

二、OD门应用

OD门:为了满足输出电平的转换,吸收大负载电流(上拉电阻作用)以及线与逻辑,将MOS改为漏极开路。

1)OD输出的与非门结构图如下:

OD门工作必须接上拉电阻RL到电源上。

2)可以将多个OD门输出端直接相连,实现线与逻辑,即将输出并联使用,可以实现线与或用作电平转换和驱动。

如下图所示:

Y1、Y2中任何一个为低电平,输出都为低电平,同时为高时,输出才为高电平。

三、传输门

CMOS传输门:利用P沟道MOS管和N沟道MOS管互补的特性连接如下图

T1是N沟道增强型MOS管,T2是P沟道增强型MOS管。T1和T2的源极和漏极分别相连作为传输门的输入端和输出端。C和C’是互补的控制信号。

CMOS传输门的应用:

1)传输门和反相器构成异或门电路:

A=1,B=0,TG1截止,TG2导通,Y=B’=1

A=0,B=1,TG1导通,TG2截止,Y=B=1

A=0,B=0,TG1导通,TG2截止,Y=B=0

A=1,B=1,TG1截止,TG2导通,Y=B‘=0

2)D锁存器和触发器

基于RS锁存器的D锁存器:图4.4-4中相对于同步RS锁存器就是把输入连在一起成为D,同样clk高电平期间输出Q=D,clk低电平输出保持;缺点就是在clk高电平期间输入的任何变化都会被输出, 可能造成一个时钟周期内锁存器的输出状态多次翻转, 即 “空翻” 问题。

传输门结构的D锁存器:图4.4-5的D锁存器功能与图4.4-4相同,但电路结构简单,所需器件少,因而在数字集成电路设计中使用较多。当clk高电平期间,上面的传输门导通,下面的的传输门断开, 输人信号 D 被传送到输出端; 当clk低电平期间, 上面的传输门断开, 下面的传输门导通, 交叉耦合反相器构成双稳态电路保持电路状态, 而输入信号D同输出端隔离。

为了解决锁存器 “空翻” 的问题, 可以采用主从结构的触发器 , 通过将两个锁存器串联在一起, 分别用两个反相时钟控制 , 触发器在时钟有效沿的短期时间 “ 窗口” 采样数据。

图 4.4-6 中所示为基于传输门结构的 D 触发器, 由两个图 4.4-5 中所示的 D 锁存器构成 , 前一个为主锁存器, 时钟低电平期间为透明,而后一个为从锁存器 , 时钟高电平期间为透明, 即两者时钟反相。clk低电平期间,TG1和TG4导通,输入信号D传到A,clk变为高电平时,TG2和TG3导通,从A传到输出Q,因此该触发器可以 ,在时钟的上升沿采样数据, 并在整个时钟周期内保持数据, 即保证了输出在一个时钟周期内只能变化一次, 避免了锁存器的 “ 空翻” 现象。

为了保证触发器能够采样到正确的输入数据, 必须使得输入数据 D 在时钟有效沿到来之前和之后的一段时间内都保持稳定, 这两段时间分别定义为触发器的建立时间和保持时间,在图 4.4-7 中为ts和tn。 此外, 时钟有效沿到来后一段时间, 触发器输出采样数据, 这个时间定义为触发器的延迟时间, 图 4.4-7 中为tp。在图 4.4-6 中为经过传输门 TG3 和反相器到输出端 Q 的延迟。 这三个时间为触发器的主要时序参数。

锁存器(latch) 和触发器(flip-flop) 区别?

电平敏感的存储器件称为锁存器。 可分为高电平锁存器和低电平锁存器, 用于不同时钟之间的信号同步。

边沿敏感的是触发器。 分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。 前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

传输门构成锁存器:

四、 三态门

1)高阻态:

三态门除了高低电平,还有第三个状态——高阻态。

高阻态:电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

三态门常用在IC的输出端,也称为输出缓冲器

2)下图是CMOS三态输出反相器的结构:

当EN’=0时,Y=A’:

A=1,G4、G5的输出为高电平,T1截止、T2导通,Y=0;

A=0,G4、G5的输出为低电平,T1导通、T2截止,Y=1;

当EN’=1时,不管A为高低状态,G4输出高电平,G5输出低电平,T1和T2同时截止,输出呈现高阻态。

3)三态门的应用:

减少各单元之间的连线数目:

数据的双向传输:

4)还有几种常见的三门结构:

图一:

三态非门,当~ EN为1时,最上面的PMOS和最下面的NMOS管截止,无论A取什么状态,输出为高阻态,反之输出为 Y= ~ A

图二:

利用一个与非门,得到三态缓冲门,当~EN为高电平时,最上面的PMOS管截止,输出为高阻态,反之,输出为 Y=A

图三:

三态非门,在反相器后面加一个传输门,当~EN为低电平,传输门导通,输出 Y = ~A,反之传输门截止,输出高阻态。如果想要EN高电平有效,交换传输门上下端子的反相器即可。

图四:

利用一个与非门,得到三态缓冲门,当~EN为高电平时,最上面的PMOS管截止,输出为高阻态,反之,输出为 Y=A

五、竞争与冒险

定义1:在组合逻辑中,由于门的输入信号通路中经过了不同的延时, 导致到达该门得时间不一致叫竞争。

在理想情况下F的输出应该是一直稳定的0输出,但是实际上每个门电路从输入到输出是一定会有时间延迟的,这个时间通常叫做电路的开关延迟。而且制作工艺、门的种类甚至制造时微小的工艺偏差,都会引起这个开关延迟时间的变化。实际上如果算上逻辑门的延迟的话,那么F最后就会产生毛刺。

定义2:我们将门电路两个输入信号同时向相反的逻辑电平跳变( 一个从 1 变为 0,另一个从 0 变为 1)的现象称为竞争。

由于竞争而使电路输出发生瞬时错误的现象叫做冒险。(也就是由于竞争产生的毛刺叫做冒险)。

如何判断?

如果逻辑函数在一定条件下可以化简成 Y=A+A’或 Y=AA’则可以判断存在竞争冒险现象(只是一个变量变化的情况)。

如何消除?

解决方法: 1: 输出加滤波电容, 消除毛刺的影响; 2: 加选通信号, 避开毛刺; 3: 增加冗余项消除逻辑冒险。