文章目录

- 前言

- 一、IP核的介绍

- 二、VIO核

- 1.作用

- 2.调用方法

- 总结

前言

提示:本篇文章所使用的软件为Vivado2018.3:

以四选一数据选择器为例,使用verilog hdl语言以及Vivado自带的VIO,IP来实现功能

提示:以下是本篇文章正文内容,下面案例可供参考

一、IP核的介绍

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。软核就是RTL代码,方便修改。固核是综合后的网表,不宜修改。硬核就是经过完整后端设计的掩模,基本不能修改。

简单来说,就是相当于嵌入式开发调用的库文件。下面以VIO核为介绍,简单阐述IP的调用方法

二、VIO核

1.作用

VIO:Virtual input output,即虚拟IO。

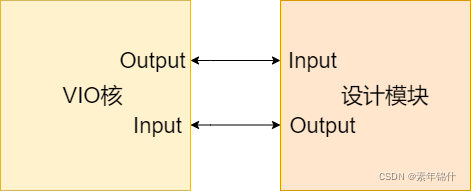

主要用作虚拟IO使用;VIO的输出可以控制模块的输入,VIO的输入可以显示模块的输出值。 即在设置VIO的输入和输出时,将实际应用中的输入设置成VIO核中的输出,将实际应用中的输出设置成VIO核中的输入。

连接如下图:

代码如下(示例):

2.调用方法

1).添加源文件。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/04/07 14:46:17

// Design Name: MoWenQi

// Module Name: MUX4_MWQ

// Project Name:

// Target Devices:

// Tool Versions:

// Description: 基于verilog hdl调用VIO核的四选一多路器

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module MUX4_MWQ(input sys_clk ); //定义一个输入时钟信号reg[3:0] out; //定义四位的一个输出wire[1:0] a, b, c, d; //定义四个2位的输入wire[1:0] sel; //定义一个两位的sel使能端always @(*) //always模块中的任何一个输入信号或电平发生变化时,该语句下方的模块将被执行。包括电平触发和时沿触发begin //自上而下,按照顺序逐个对分支表达式进行判断,如果这一分支表达式等于控制表达式的值,就执行其对应操作;均不相等时,执行default操作;case(sel) //判断条件为sel的值2'b00: out=a; //当sel为 00 时 把a的值赋值给out2'b01: out=b; //当sel为 01 时 把b的值赋值给out2'b10: out=c; //当sel为 10 时 把c的值赋值给out2'b11: out=d; //当sel为 11 时 把d的值赋值给outdefault: out=2'bx; //武上述条件时,把out赋值x不确定态endcaseend

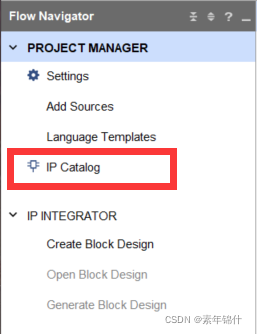

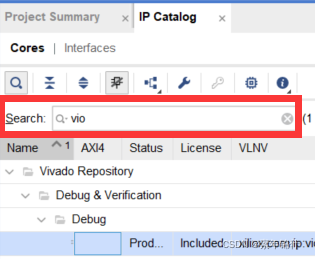

endmodule2).点击IP Catalog-搜索VIO进行添加(完成初始化配置)

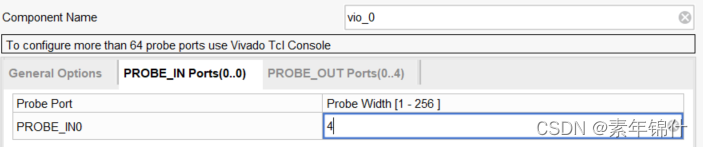

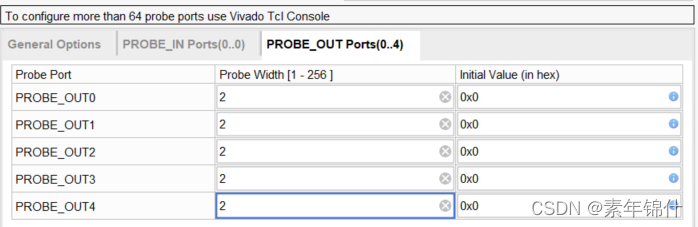

3)对输入输出个数和位宽的配置

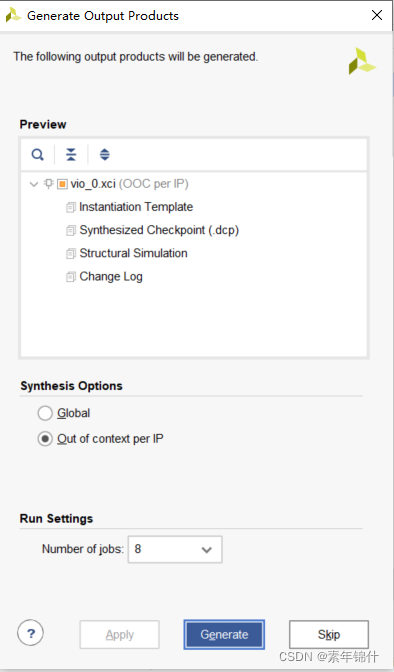

点击生成

4)例化

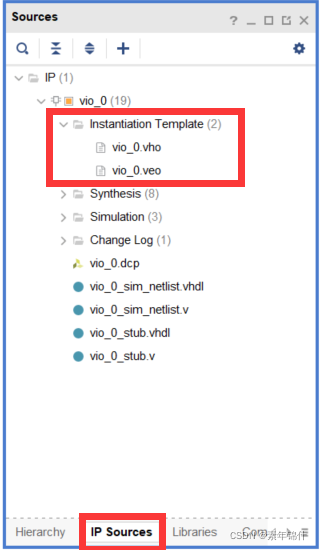

点击IP Sources-打开vio-0.evo文件

找到vio_0.evo文件中大概57行,拷贝到源文件中,将()里面的名称改成源文件的名称

vio_0 your_instance_name (.clk(clk), // input wire clk.probe_in0(probe_in0), // input wire [3 : 0] probe_in0.probe_out0(probe_out0), // output wire [1 : 0] probe_out0.probe_out1(probe_out1), // output wire [1 : 0] probe_out1.probe_out2(probe_out2), // output wire [1 : 0] probe_out2.probe_out3(probe_out3), // output wire [1 : 0] probe_out3.probe_out4(probe_out4) // output wire [1 : 0] probe_out4

);

再进行,分析综合,布局布线

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/04/07 14:46:17

// Design Name: MoWenQi

// Module Name: MUX4_MWQ

// Project Name:

// Target Devices:

// Tool Versions:

// Description: 基于verilog hdl调用VIO核的四选一多路器

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module MUX4_MWQ(input sys_clk ); //定义一个输入时钟信号reg[3:0] out; //定义四位的一个输出wire[1:0] a, b, c, d; //定义四个2位的输入wire[1:0] sel; //定义一个两位的sel使能端always @(*) //always模块中的任何一个输入信号或电平发生变化时,该语句下方的模块将被执行。包括电平触发和时沿触发begin //自上而下,按照顺序逐个对分支表达式进行判断,如果这一分支表达式等于控制表达式的值,就执行其对应操作;均不相等时,执行default操作;case(sel) //判断条件为sel的值2'b00: out=a; //当sel为 00 时 把a的值赋值给out2'b01: out=b; //当sel为 01 时 把b的值赋值给out2'b10: out=c; //当sel为 10 时 把c的值赋值给out2'b11: out=d; //当sel为 11 时 把d的值赋值给outdefault: out=2'bx; //武上述条件时,把out赋值x不确定态endcaseendvio_0 MUX4_MWQ (.clk(sys_clk), // input wire clk.probe_in0(out), // input wire [3 : 0] probe_in0.probe_out0(a), // output wire [1 : 0] probe_out0.probe_out1(b), // output wire [1 : 0] probe_out1.probe_out2(c), // output wire [1 : 0] probe_out2.probe_out3(d), // output wire [1 : 0] probe_out3.probe_out4(sel) // output wire [1 : 0] probe_out4

);

endmodule添加约束文件,进行管脚分配

create_clock -period 20.00 -name clk [get_ports sys_clk]set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports sys_clk]总结

后面测试部分等拿到板子再仿真测试