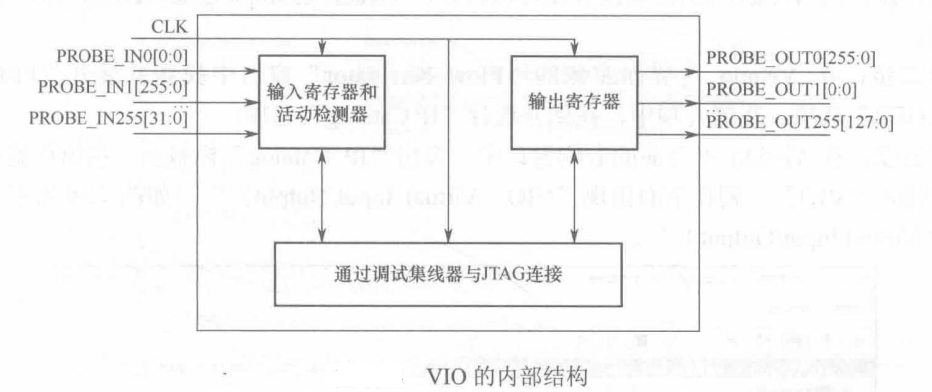

虚拟输入输出(Virtual Input Output,VIO)核是一个可定制的IP核,它可用于实时监视和驱动内部FPGA的信号,如图所示。

可以定制VIO的输入和输出端口的数量与宽度,用于和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核进行实时交互时,需要使用Vivado逻辑分析特性。

接下来将介绍VIO的原理及应用,内容主要包括设计原理、添加VIO核、生成比特流文件和下载并调试设计。

设计原理

设计以下源码的工程,并添加VIO核:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/08/22 23:44:58

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module top(input clk,input a,input b,output reg [5:0] z);

reg [5:0]z_tmp;

wire [5:0] z_vio;

reg a_tmp,b_tmp;

wire a_in,b_in;

wire sel;

wire a_vio,b_vio;

assign a_in=sel ? a : a_vio;

assign b_in=sel ? b : b_vio;

assign z_vio=z;vio_0 Inst_vio (.clk(clk), // input wire clk.probe_in0(z), // input wire [5 : 0] probe_in0.probe_out0(sel), // output wire [0 : 0] probe_out0.probe_out1(a_vio), // output wire [0 : 0] probe_out1.probe_out2(b_vio) // output wire [0 : 0] probe_out2

);

always @(posedge clk)

begina_tmp<=a_in;b_tmp<=b_in;

end

always @(*)

beginz_tmp[0]=a_tmp & b_tmp;z_tmp[1]=~(a_tmp & b_tmp);z_tmp[2]=a_tmp | b_tmp;z_tmp[3]=~(a_tmp | b_tmp);z_tmp[4]=a_tmp ^ b_tmp;z_tmp[5]=a_tmp ~^ b_tmp;

end

always @(posedge clk)

begin

z<=z_tmp;

end endmodule

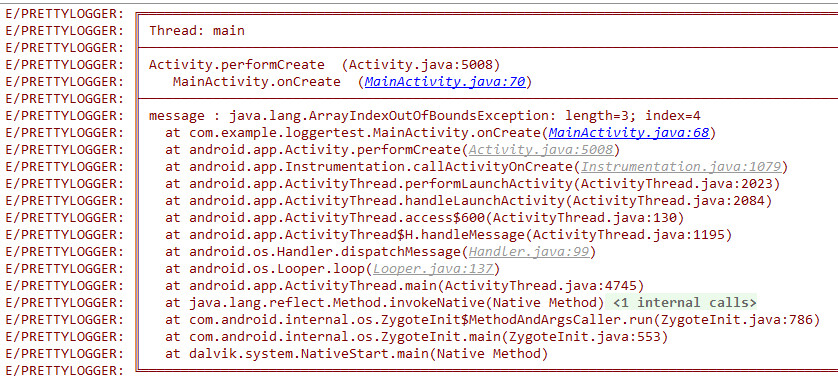

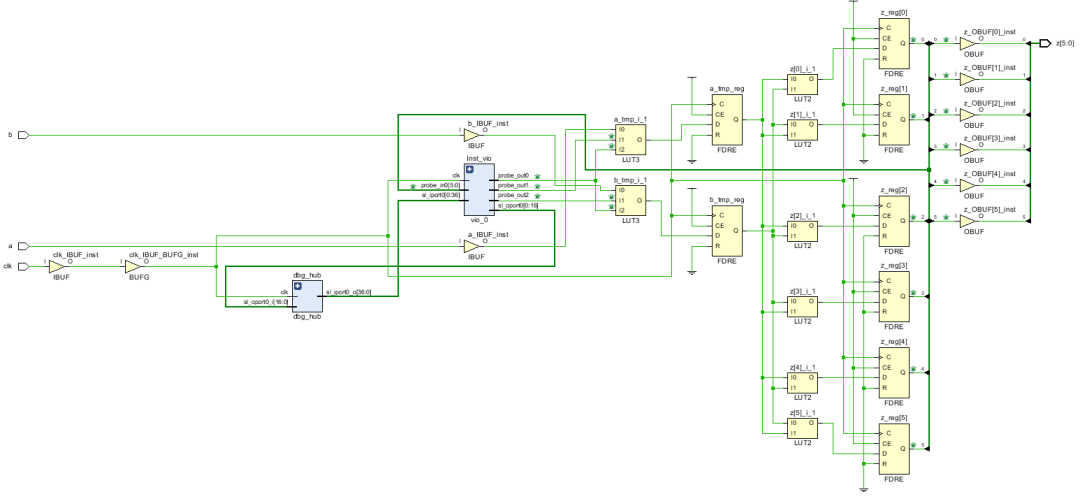

添加VIO后的整体设计如下:

如上图所示,在该设计中添加一个vio核,该IP提供3个输出端口,其中probe_out0端口用于选择进入寄存器a_tmp_reg和寄存器b_tmp_reg的信号。当probe_out0输出1时,将外部端口a和b提供的信号分别连接到寄存器a_tmp_reg和寄存器b_tmp_reg;当probe_out0输出0时,将vio输出端口probe_outl和probe_out2信号连接到寄存器a_tmP_reg和b_tmp_reg。这样就可以通过vio提供的端口来控制整个FPGA的设计。此外,FPGA设计的最终输出z可以连接到vio模块的probe_in0输入端口。

添jia VIO核

本节将添加VIO核,主要步骤如下所示。

第一步:用Vivado集成开发环境打开需要添加的工程。

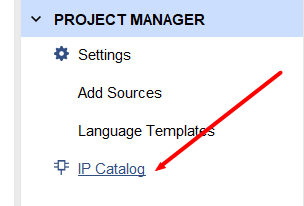

第二步:在Vivado主界面左侧的“Flow Navigator”窗口中找到并展开PROJECT MANAGER选项。在展开项中,找到并选择“IP Catalog”选项。

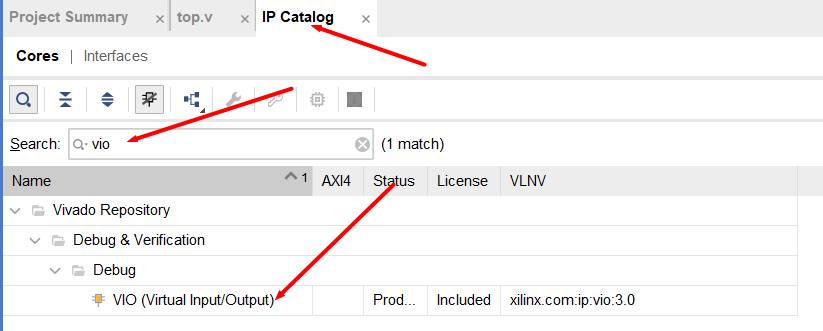

第三步:在Vivado主界面的右侧窗口中,弹出“IP Catalog”标签页。在该标签页的搜索框中输入“VIO”,则在下面出现“VIO(Virtual Input/Output)”,如图所示,双击“VIO(Virtual Input/Output)”。

第四步:弹出“Customize IP-VIO(VirtualInput/Output)”对话框。

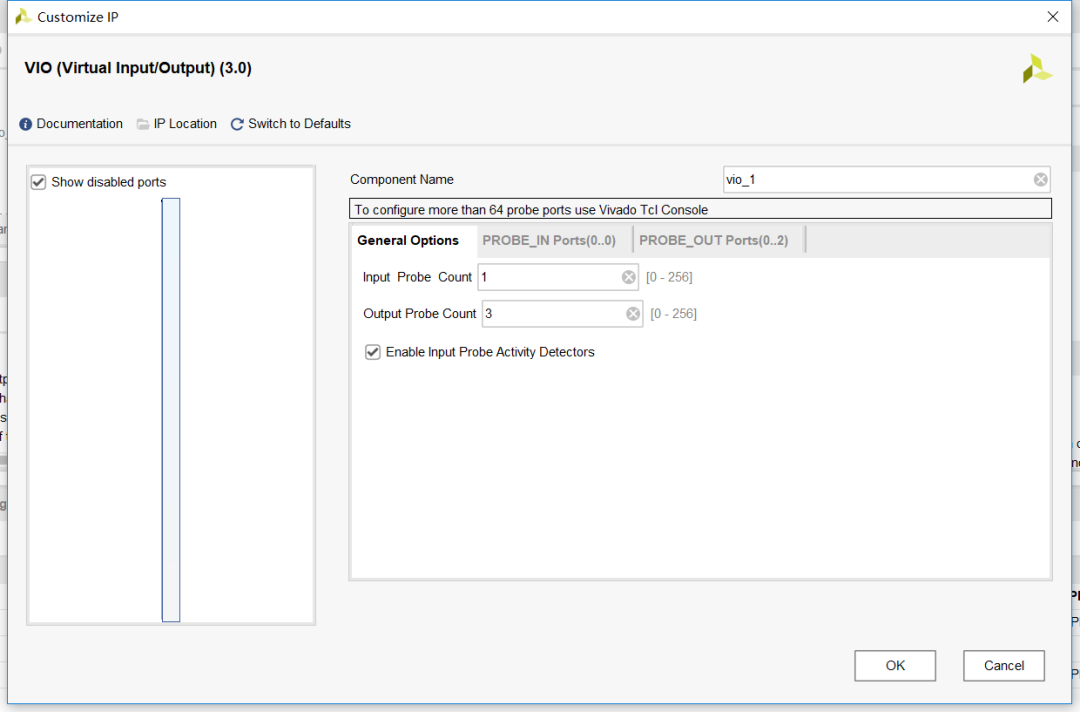

(1)单击“General Options”标签,如图所示,在该标签页中,按如下参数进行设置。

Input ProbeCount:1。

Output ProbeCount:3。

勾选 Enable Input Probe Activity Detectors前面的复选框。

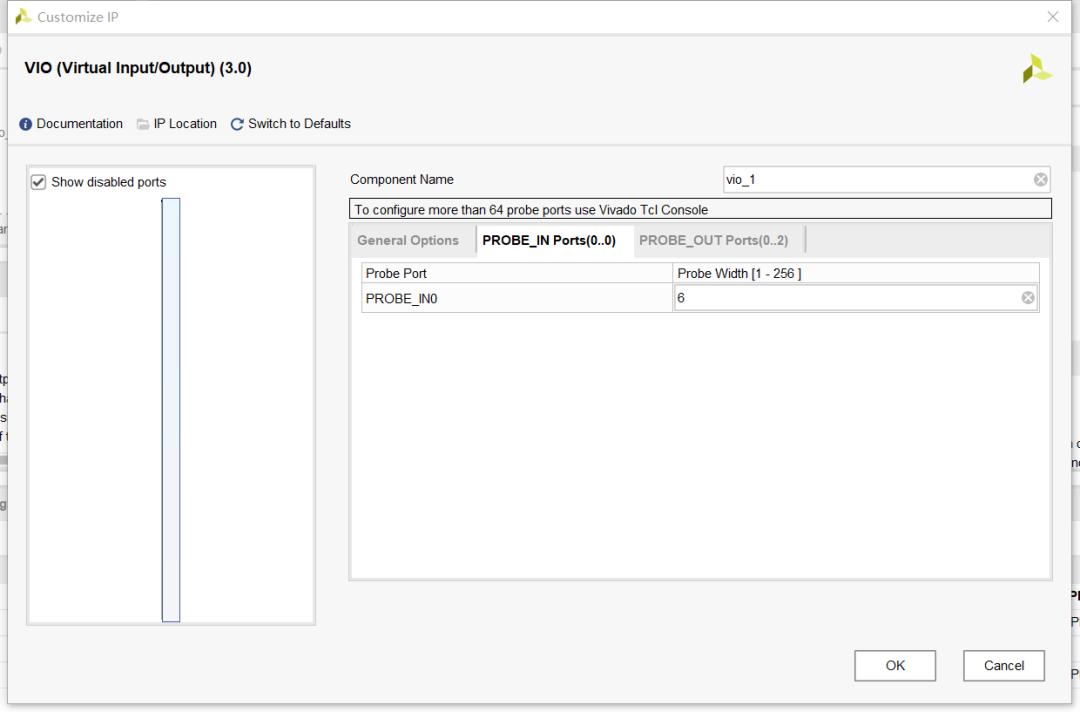

(2)单击“PROBE_IN Ports(0..0)”标签,如图所示,在该标签页中,按如下参数进行设置

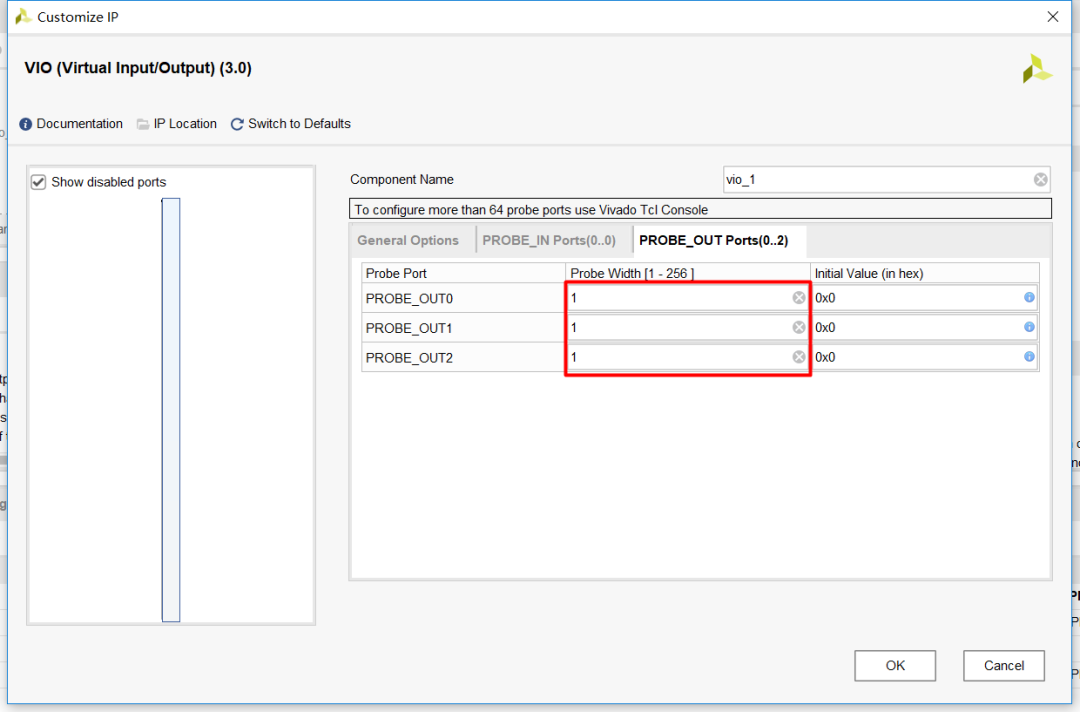

(3)单击“PROBE_OUTPorts(0..2)”标签,如图所示,在该标签页中,按如下参数进行设置。

第五步:单击【OK】按钮,退出“Customize IP”对话框。

第六步:弹出“Generate Output Products”对话框。

第七步:单击【Generate】按钮,退出“Generate Output Products”对话框。

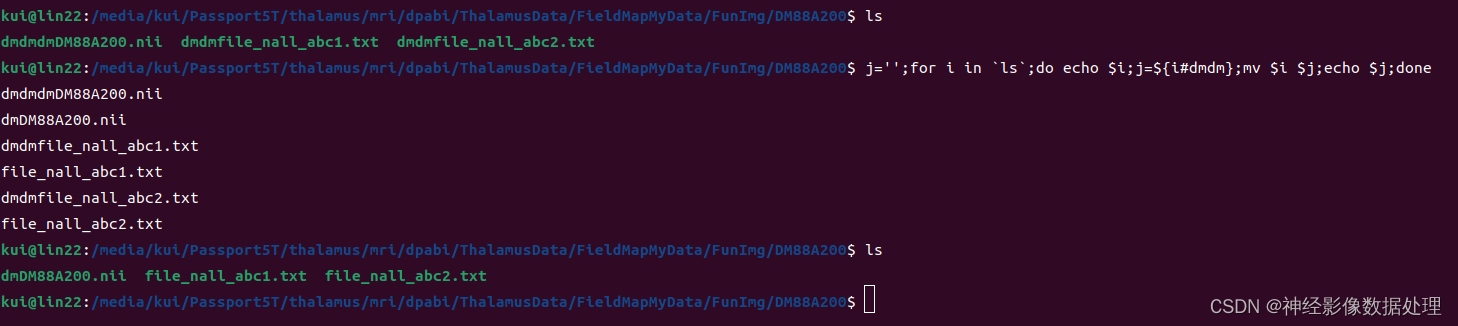

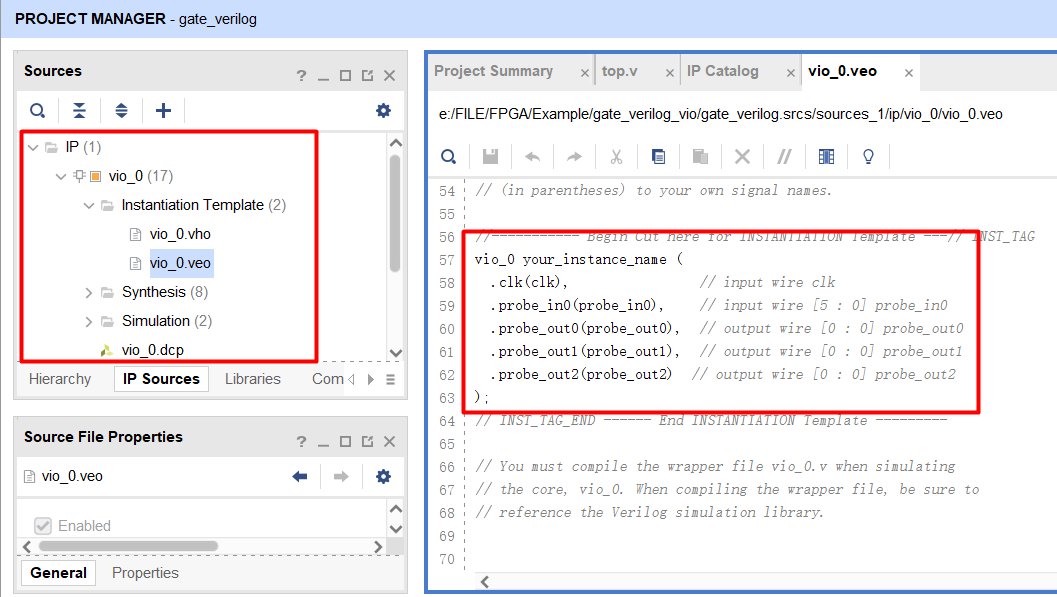

第八步:在“Sources”窗口中,单击“IP Sources”标签。在该标签页中,可以看到添加了名字为“vio_0”的IP核实例,如图所示。找到并展开“vio_0”选项。在展开项中,找到并展开“Instatiation Template”选项。在展开项中,选择并用鼠标左键双击vio_0.veo,打开其例化模板,如下述代码所示。

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

vio_0 your_instance_name (.clk(clk), // input wire clk.probe_in0(probe_in0), // input wire [5 : 0] probe_in0.probe_out0(probe_out0), // output wire [0 : 0] probe_out0.probe_out1(probe_out1), // output wire [0 : 0] probe_out1.probe_out2(probe_out2) // output wire [0 : 0] probe_out2

);

第九步:在“Sources”窗口中,单击“Hierarchy”标签。在该标签页中,找到并展开“Design Sources”选项。在展开项中,找到并用鼠标双击top.v文件,按下述代码修改设计代码,并添加vio的例化代码。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/08/22 23:44:58

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module top(input clk,input a,input b,output reg [5:0] z);

reg [5:0]z_tmp;

wire [5:0] z_vio;

reg a_tmp,b_tmp;

wire a_in,b_in;

wire sel;

wire a_vio,b_vio;

assign a_in=sel ? a : a_vio;

assign b_in=sel ? b : b_vio;

assign z_vio=z;vio_0 Inst_vio (.clk(clk), // input wire clk.probe_in0(z), // input wire [5 : 0] probe_in0.probe_out0(sel), // output wire [0 : 0] probe_out0.probe_out1(a_vio), // output wire [0 : 0] probe_out1.probe_out2(b_vio) // output wire [0 : 0] probe_out2

);

always @(posedge clk)

begina_tmp<=a_in;b_tmp<=b_in;

end

always @(*)

beginz_tmp[0]=a_tmp & b_tmp;z_tmp[1]=~(a_tmp & b_tmp);z_tmp[2]=a_tmp | b_tmp;z_tmp[3]=~(a_tmp | b_tmp);z_tmp[4]=a_tmp ^ b_tmp;z_tmp[5]=a_tmp ~^ b_tmp;

end

always @(posedge clk)

begin

z<=z_tmp;

end endmodule

第 十 步 :保 存 该 设 计 文 件 。

生成比特流文件

下载并调试设计

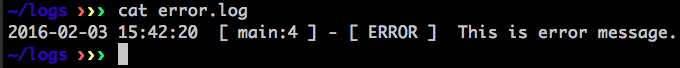

将生成的比特流文件下载到开发板上的FPGA元器件中,并通过VIO对设计进行监控,主要步骤如下所示。

第一步:将JTAG和FPGA板卡链接并和PC连接。

第二步:给开发板上电。

第三步:在“HARDWARE MANAGER”对话框中,单击【Open target】按钮,出现浮动菜单。在浮动菜单内,执行菜单命令【AutoConnect】。

第四步:在“Hardware”窗口中,选择FPGA,单击鼠标右键,出现浮动菜单。在浮动菜单内,执行菜单命令【Program Device】。

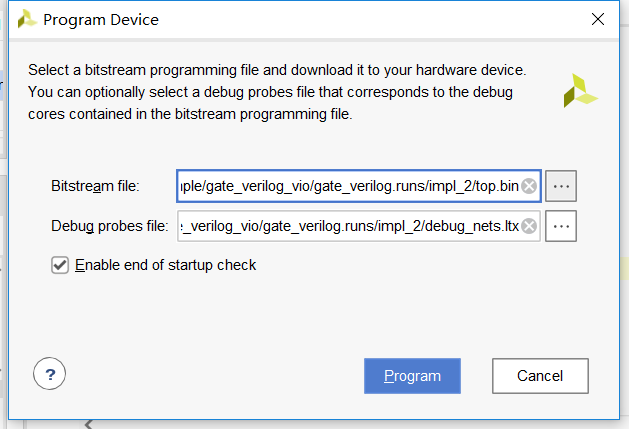

第五步:弹出“Program Device”对话框,如图所示。在该对话框中,选择合适的“Bit stream file”和“Debug probes files”。

第六步:单击【Program】按钮。

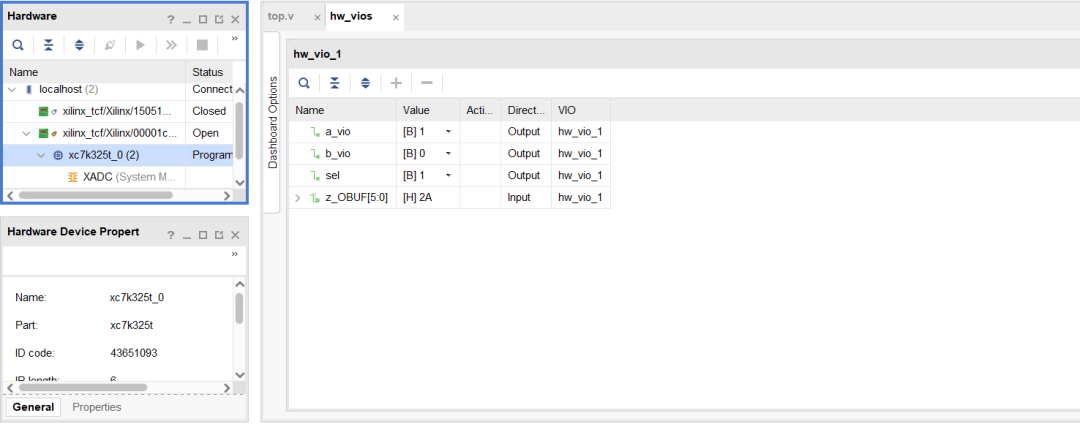

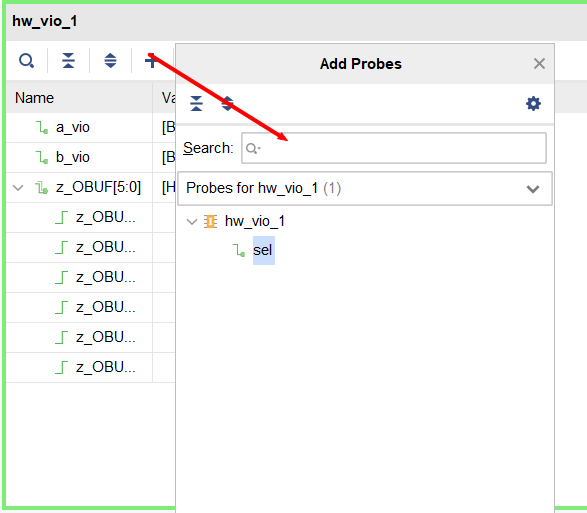

第七步:在Vivado主界面右侧的窗口中,弹出“hw_vio_l”对话框,如图所示。在该对话框中,单击+按钮。出现浮动菜单。在浮动菜单内,分别双击a_vio、b_vio、sel和z_OBUF[5:0],将其添加到“hw_vio_l”对话框中,如图所示。

第八步:在图所示的对话框中,先将sel的“Value”设置为1,此时a_vio和b_vio的值将送给FPGA设计。

第九步:在图所示的对话框中,将“sel”的“Value”设置为0,此时由开发板上开关的设置状态确定a和b的值,并将其送给FPGA设计。

第十步:关闭并退出设计。

工程链接

链接:https://pan.baidu.com/s/11kFLfledKFOmYl8YXwiFjw 提取码:open

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程

【Vivado使用误区与进阶】总结篇

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

SystemVerilog数字系统设计_夏宇闻 PDF

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGA

1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

AD936x+ZYNQ搭建收音机(一)

AD936x+ZYNQ搭建OpenWIFI

无招胜有招-Vivado非工程模式下的详细设计

追寻ARM的起源-Acorn电脑简史及FPGA实现

面试中经常会遇到的FPGA基本概念,你会几个?

Xilinx FPGA MIPI 接口简单说明

介绍一些新手入门FPGA的优秀网站

Vivado ML(机器学习) 2021尝鲜

推荐一些可以获取免费的国外的原版书籍(电子版)网站

【Vivado那些事】FPGA的配置方式

FPGA 的重构

浅析FPGA局部动态可重构技术

ISP(图像信号处理)算法概述、工作原理、架构、处理流程

国产CPU概括

从电子游戏历史看IC发展的助推剂

80年代电子游戏及电脑游戏的发展历史

PCIe总线的基础知识

万字长文带你回顾电子游戏的七十多年历史(完整版)

FPGA中异步复位,同步释放的理解

OpenFPGA系列文章总结

用Verilog设计一个16 位 RISC 处理器

介绍一些新手入门FPGA的优秀网站(新增)

Verilog数字系统基础设计-CRC

FPGA 的布局规划艺术

Verilog数字系统基础设计-奇偶校验

建立和保持时间及时序简单理解

(Xilinx)FPGA中LVDS差分高速传输的实现