错误信息如下:

[DRC NSTD-1] Unspecified I/O Standard: 102 out of 102 logical ports use I/O standard (IOSTANDARD) value ‘DEFAULT’, instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: dout_ch1[23:0], dout_ch2[23:0], dout_ch3[23:0], dout_ch4[23:0], clk, dout_valid_ch1, dout_valid_ch2, dout_valid_ch3, dout_valid_ch4, and rstn.

[DRC UCIO-1] Unconstrained Logical Port: 102 out of 102 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: dout_ch1[23:0], dout_ch2[23:0], dout_ch3[23:0], dout_ch4[23:0], clk, dout_valid_ch1, dout_valid_ch2, dout_valid_ch3, dout_valid_ch4, and rstn.

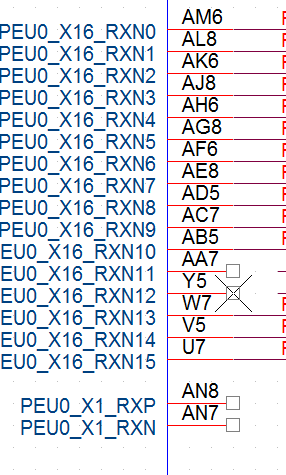

刚开始很奇怪,因为这些报错的信号在bd中是中间信号(如下图),我也没有给它们创建port,这些vivado却要给它们分配引脚,打开IO ports窗口,发现它们都被随机分配了引脚,这是怎么回事呢?

百度发现,有很多人遇到了这个问题,解决方法也记录在Xilinx官网中:

Vivado write_bitstream - ERROR: [Drc 23-20] Rule violation (NSTD-1) Unspecified I/O Standard - X out of Y logical ports use I/O standard (IOSTANDARD) value ‘DEFAULT’, instead of a user assigned specific value

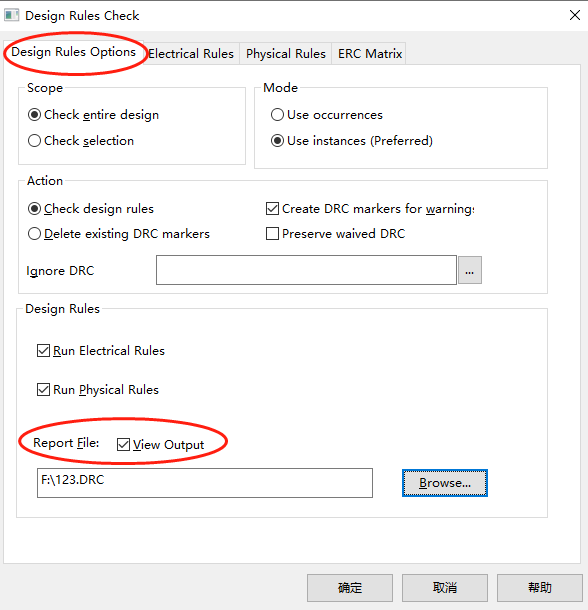

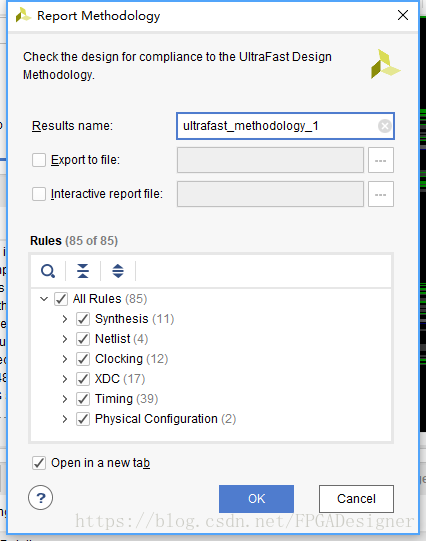

解决方案是对vivado进行设置,让其忽略这些未在约束中分配引脚的信号。这样设置之后可以生成比特流了。

但是这个错误是怎么产生的呢?经过几个小时的折腾,我发现Source中的Top不知道什么时候被改变了,应该是wrapper才对啊,原来是将一个中间文件设为了Top,那当然vivado要给它的端口信号分配引脚了,原来如此!

Top改为wrapper后,生成比特流就不出错了!

记录一下,小问题查起来也很花时间。