Vivado2019.1 ZYNQ7020无Uart SDK调试打印调试信息xil_printf

- Vivado2019.1 ZYNQ7020无Uart SDK调试打印调试信息xil_printf

- 前提条件:

- 步骤:

**

Vivado2019.1 ZYNQ7020无Uart SDK调试打印调试信息xil_printf

**

前提条件:

- Vivado 2019.1已安装并配置好。

- Zynq-7020的FPGA设计已经完成。

- 设计没有Uart硬件

步骤:

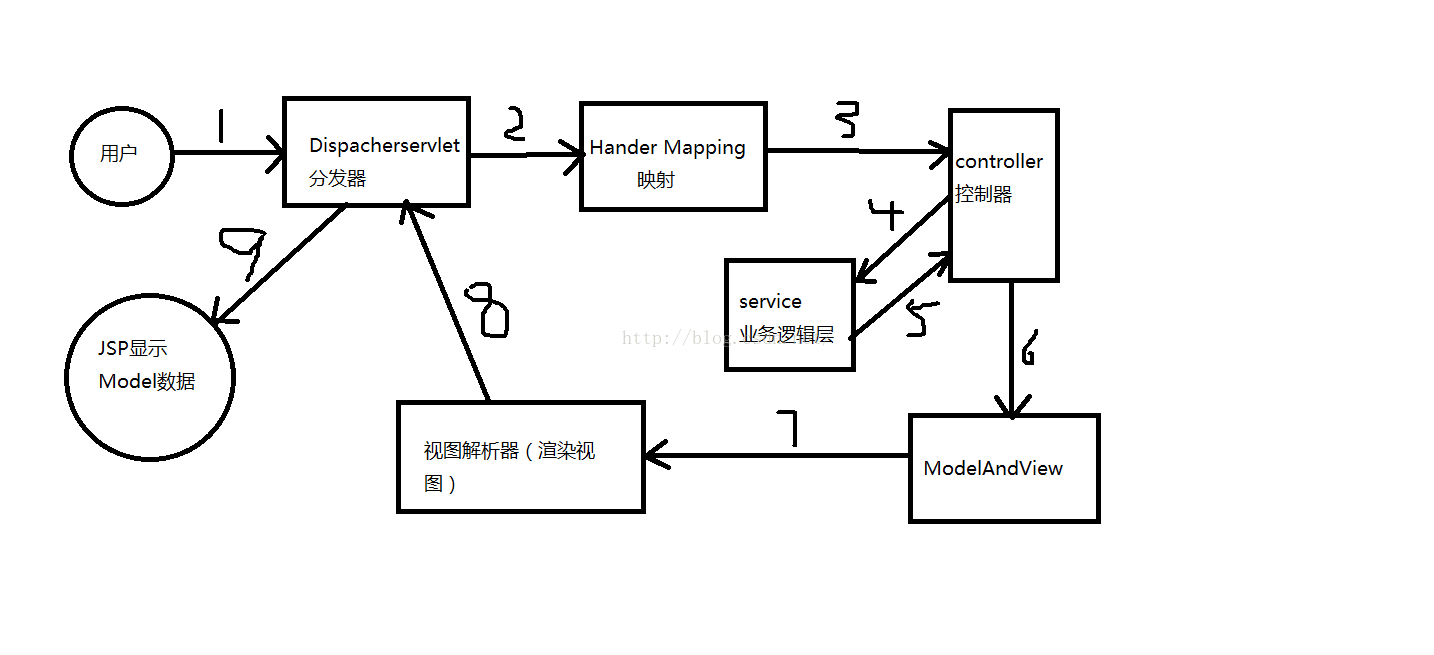

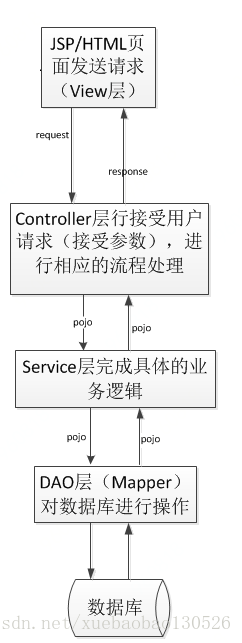

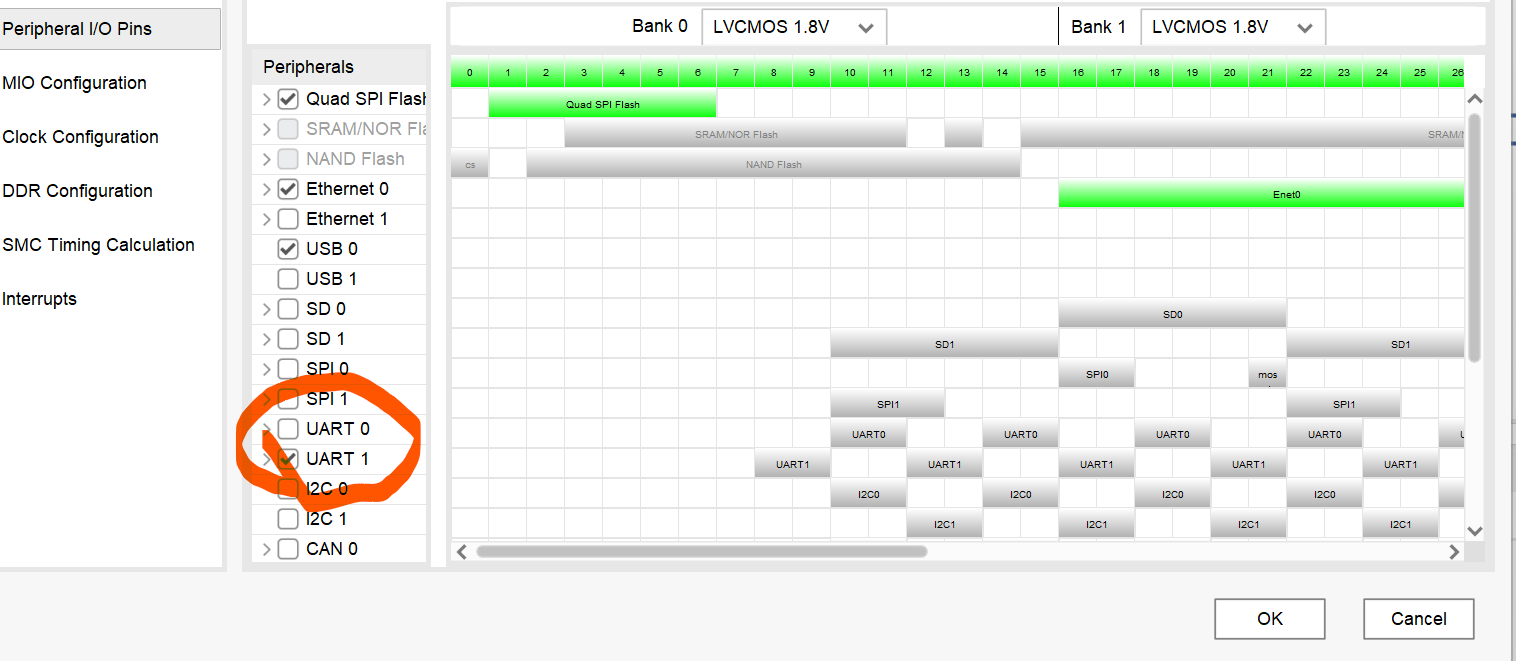

- processing system 7.0设置打开uart 1(不打开SDK无法选中官方模板),配置好其它的选项,特别是DDR。

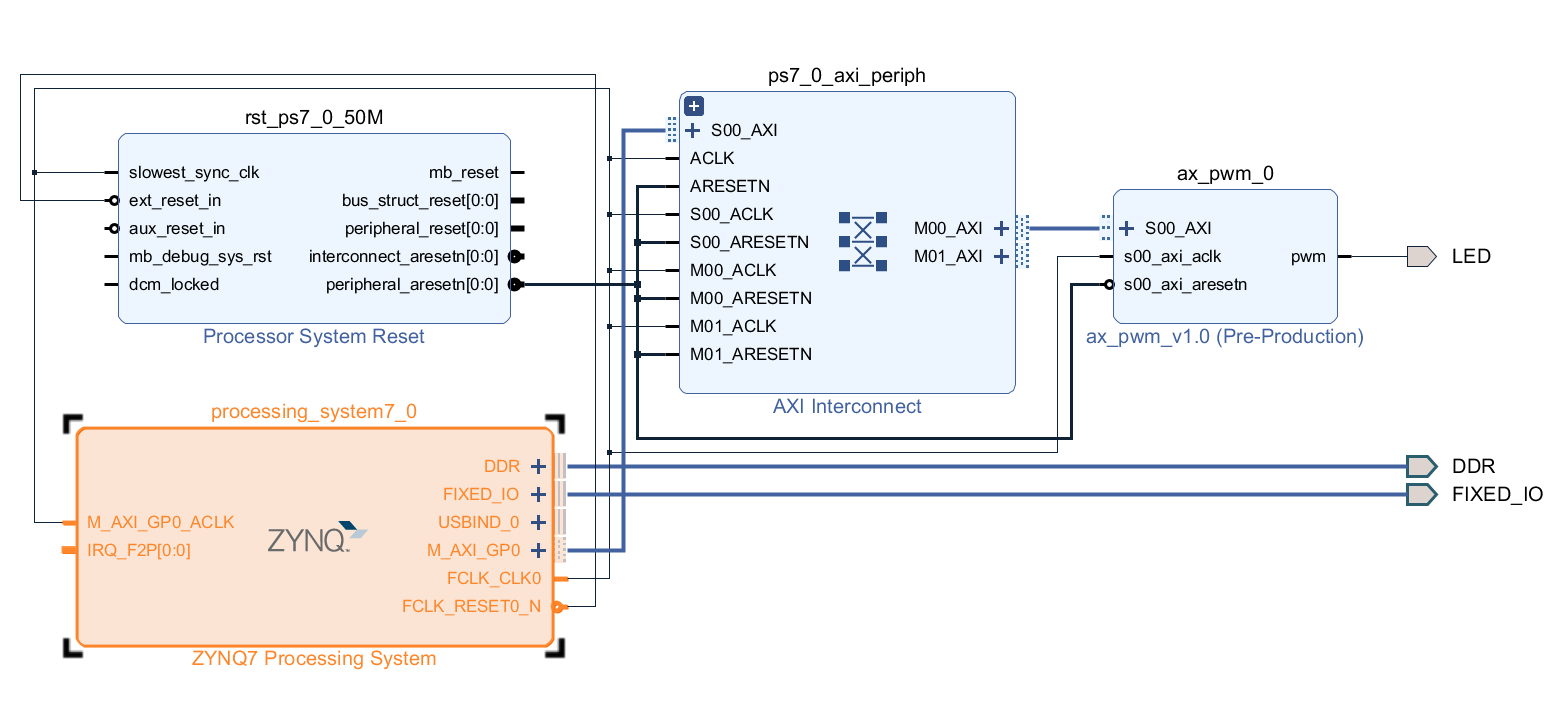

2. “Run Block Automation”,完成block design

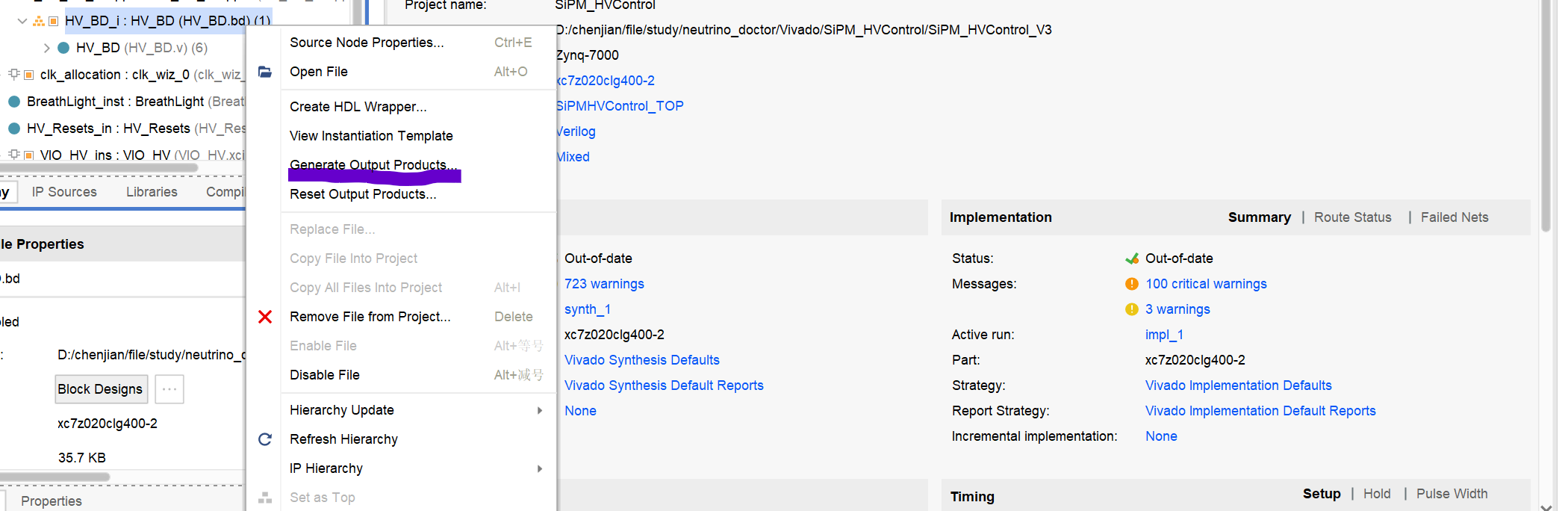

- 生成Output products

-

生成Bitstream和导出硬件:

- 在Vivado中生成Bitstream,并导出硬件(Export Hardware)。

- 在"Export Hardware"对话框中,勾选"Include bitstream"。

-

创建SDK工程:

- 打开Xilinx SDK。

- 创建一个Hello world应用程序项目。

- 将SDK工程连接到Vivado项目导出的硬件平台。

-

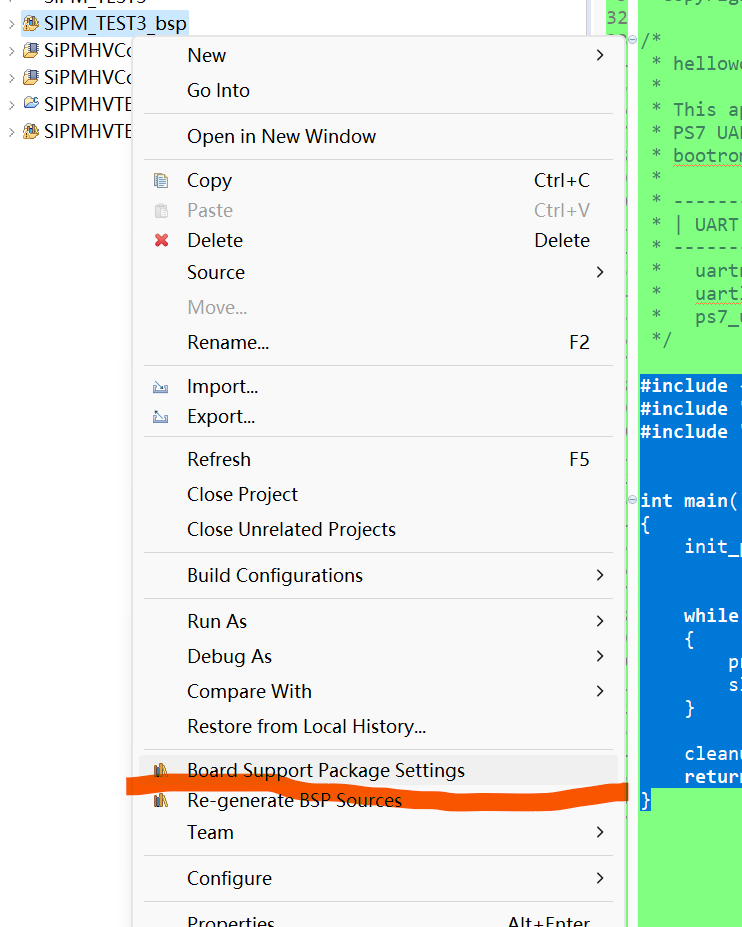

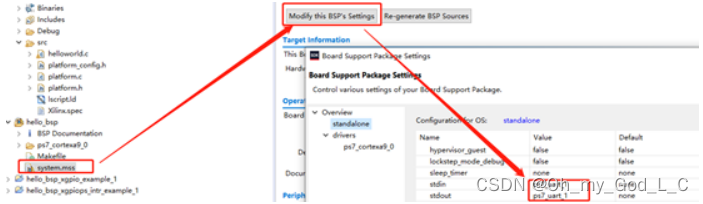

右键bsp,选中Board Suport Package Settings

-

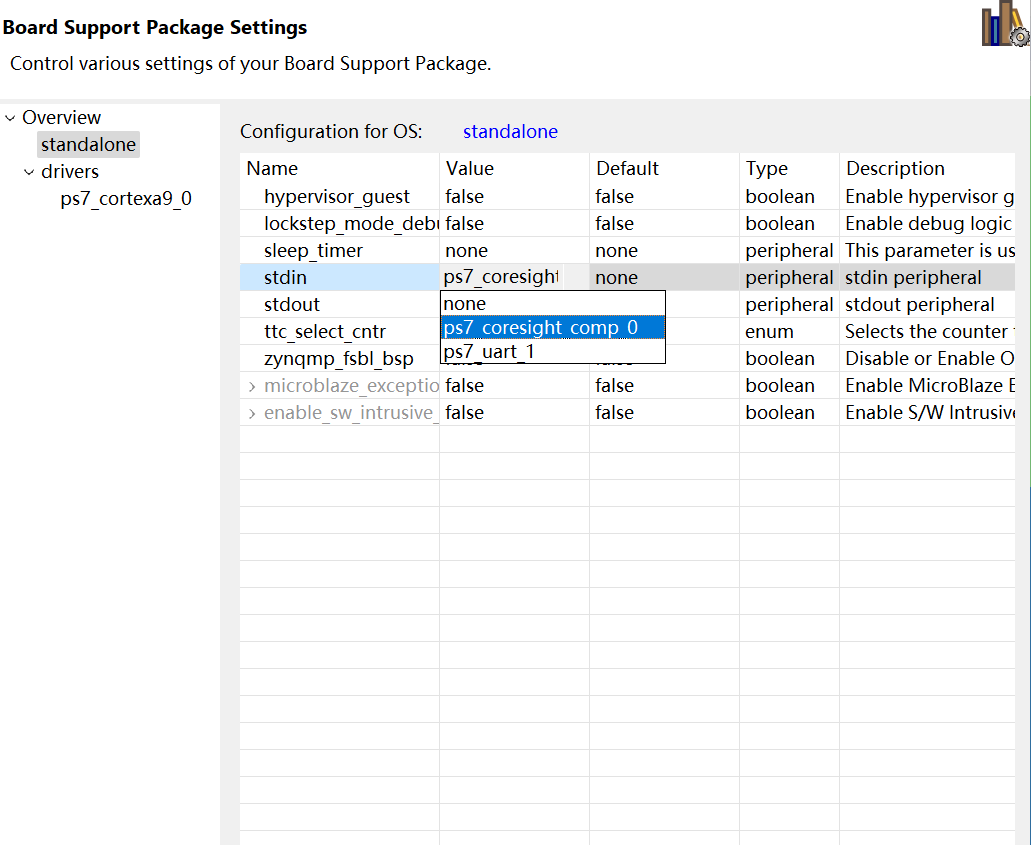

在Configuration for OS里面将stdin、stdout都改为ps7_coresight_comp_0

-

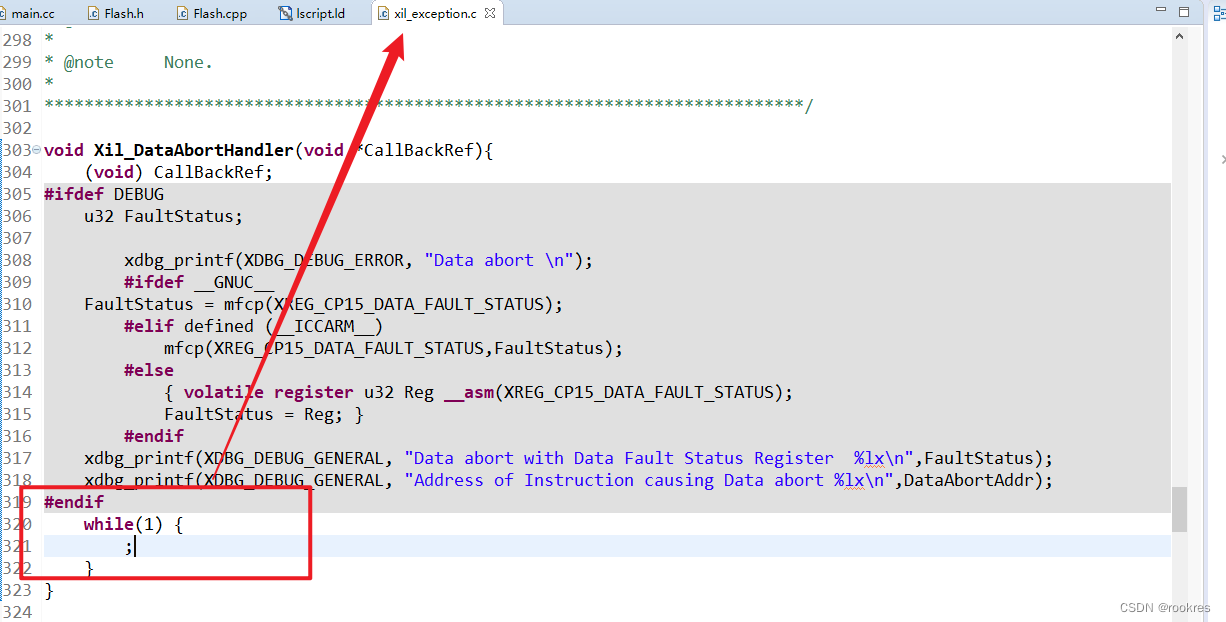

编写C代码:

- 打开SDK工程中的hello world.c文件。

- 在代码中包含头文件:

#include "xil_printf.h" - 使用

xil_printf函数打印调试信息。例如:

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"int main()

{init_platform();while(1){print("Hello world!\n\r");sleep(1);}cleanup_platform();return 0;

}

-

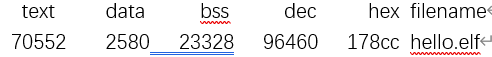

编译和烧写:

- 在SDK中编译应用程序项目。

- 确保Zynq-7020开发板连接到PC,并通过USB或JTAG连接到开发环境。

- 将编译好的应用程序通过JTAG下载到FPGA中。

-

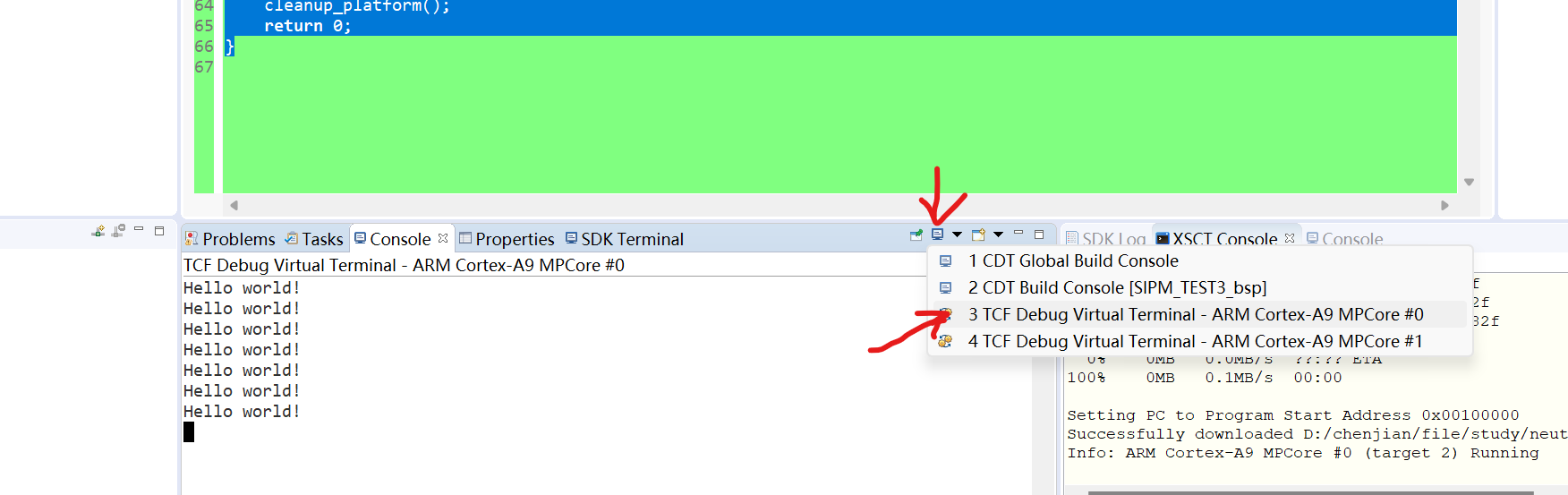

在TCF-Debug Virtual Terminal - ARM cortex-A9 MPcore#0界面就可以看到调试信息了(下拉Console可以切换不同终端)

![vivado 仿真报错:ERROR: [VRFC 10-2987] ‘xxxxx‘ is not compiled in library ‘xil_defaultlib‘](https://img-blog.csdnimg.cn/ddc42048c6a24cb0a0756b7c8145efb6.png)

![仿真出现[VRFC 10-2263] Analyzing Verilog fileinto library xil_defaultlib](https://img-blog.csdnimg.cn/2f3e466be6fd45df81f6f904a77516e9.png)