定时器Timer

- 总结

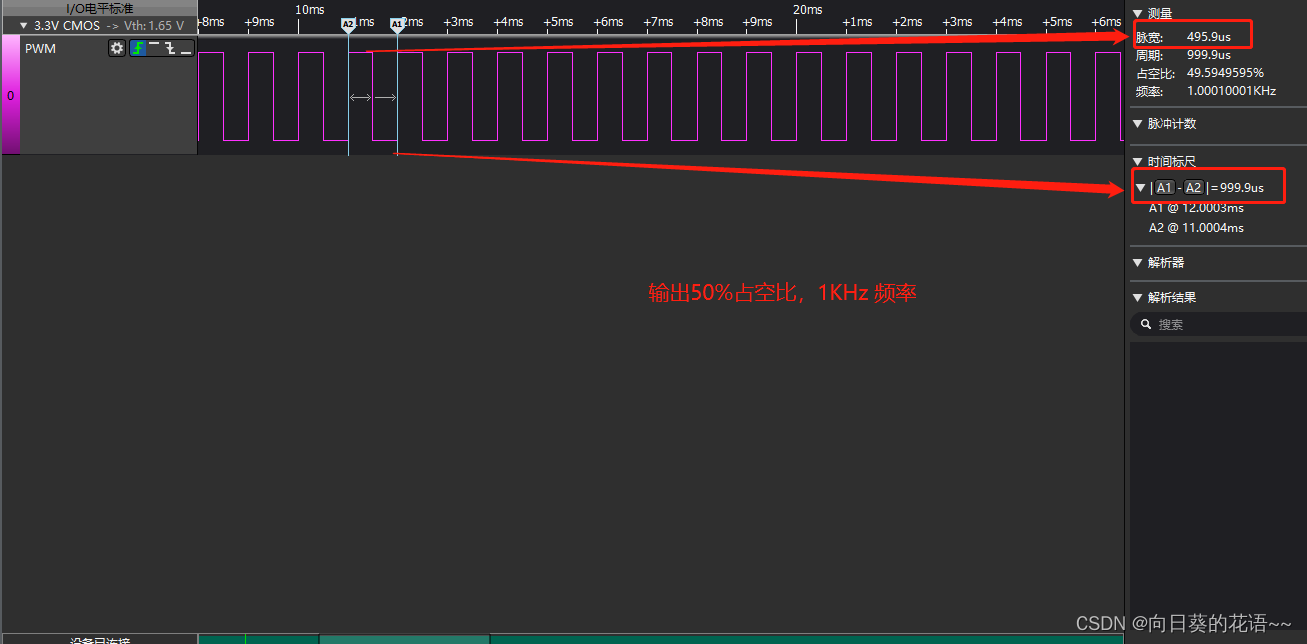

- PWM

- PWM简介

- PWM实现过程

以三星芯片S5P6818_Datasheet为例:

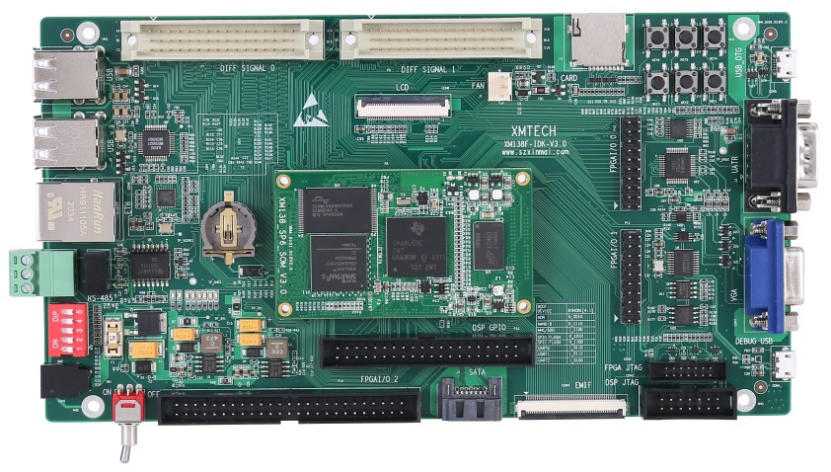

soc:S5P6818

core:A53

总结

定时器设计思路:

(1)时钟源(主频) --> 预分频(一级) --> 选择分频(二级) …:得到分频后的时钟。

(2)计数递减寄存器 = 计数缓存寄存器;//把 计数缓存寄存器中的赋值给计数递减寄存器;

(3)计数递减寄存器在分频后的一个周期到来时,自动减1;

(4)与比较寄存器值对比,控制高低电平的输出和占空比。

PWM定时器,看门狗WTD定时器是硬件产生的中断,属于irq中断。不是软中断:swi指令操作寄存器产生。

PWM

PWM简介

- PWM,英文名Pulse Width Modulation,是脉冲宽度调制缩写,它是通过对一系列脉冲的宽度进行调制,等效出所需要的波形(包含形状以及幅值),对模拟信号电平进行数字编码。

也就是说通过调节占空比的变化来调节信号、能量等的变化。 - 占空比就是指在一个周期内,信号处于高电平的时间占据整个信号周期的百分比。

例如方波的占空比就是50%。

PWM实现过程

-

S5P6818有5个32位脉冲宽度调制(PWM)定时器。这些计时器生成内部中断ARM子系统。

此外,定时器0、1、2和3还包括一个驱动外部I/O信号的PWM函数。

定时器0中的PWM有一个可选的死区发生器功能来支持大电流设备。

定时器4内部计时器没有输出引脚。 -

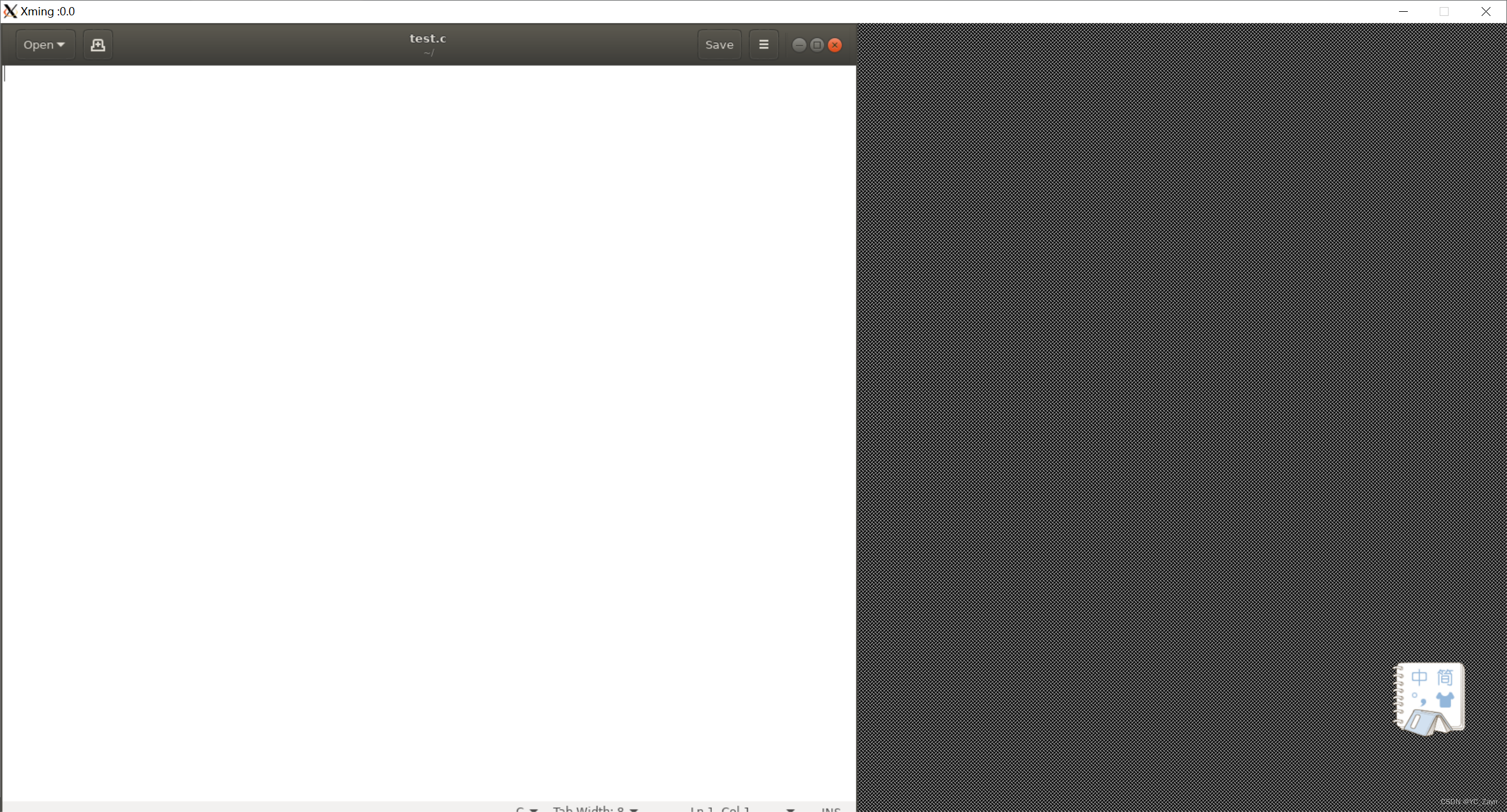

计时器使用APB-PCLK作为源时钟。

定时器0和1共享一个可编程的8位预分频器,为PCLK提供了第一级的划分。定时器2、3和4共享一个不同的8位预调器。

每个定时器都有自己的专用时钟除法器,它提供第二级的时钟除法器(除法器除以2、4、8或16)。 -

每个定时器都有自己的由定时器时钟驱动的32位递减计数器。每个递减计数器最初是从计数缓冲定时器(TCNTBn)加载赋值的。当递减计数器值减到0时,将生成定时器中断请求,以通知CPU定时器操作已经完成。当定时器递减计数器为0时,相应的计数缓冲定时器(TCNTBn)的值又会自动重新加载到下一个计数器递减计数器中,开始下一个循环。

如果在计数器运行期间,通过TCONn清除定时器的使能位, 控制着TCNTBn的值将不会再次加载到递减计数器中。

//意思是:经过分频后的时钟源,每过一个周期,则递减计数器中的值就自动减1。 -

PWM功能使用依赖TCMPBn比较寄存器中的值。如果递减计数器的值与TCMPBn比较寄存器的值相等,则定时器控制逻辑将改变输出的电平。因此比较寄存器TCMPBn决定了PWM输出的高、低电平的时间。TCNTBn和TCMPBn寄存器都是双缓冲的,因此它允许在一个周期的中间更新计时器参数,但是新值直到当前计时器周期完成后才生效。

//意思是:TCNTBn中的值赋值给递减计数器,当递减计数器中的值递减到和TCMPBn寄存器中的值相等时,定时器逻辑控制器输出发生电平取反跳转(高->低,低->高),但是递减计数器继续递减直到为0时,TCNTBn中的值重新加载给递减计数器。形成PWM高、低脉冲信号。 -

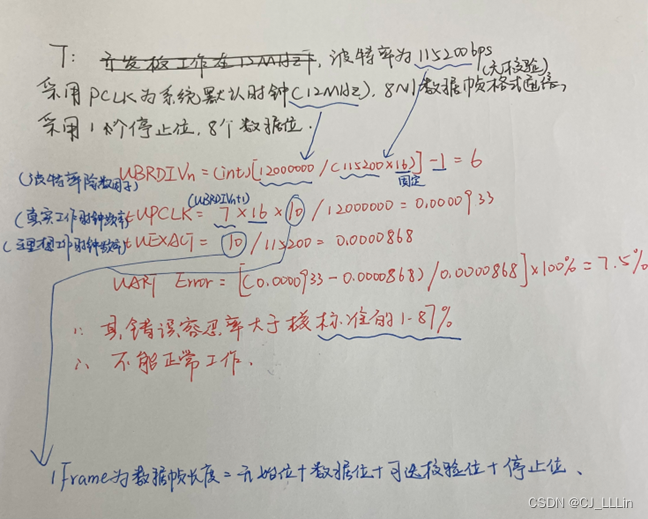

初始化TCNTBn寄存器,使用159(50 + 109)和TCMPBn,使用109。

启动计时器:设置启动位并手动将此位更新为OFF。将159的TCNTBn值加载到下位计数器中。

然后,将输出TOUTn设置为low。在TCMPBn寄存器109中,当down- counter将TCNTBn的值向下计数到数值时,输出将从低变高。当下计数器达到0时,它会生成一个中断请求。下位计数器自动重新加载TCNTBn。这就重新启动了这个循环。下图说明了单个PWM通道的时钟生成方案:

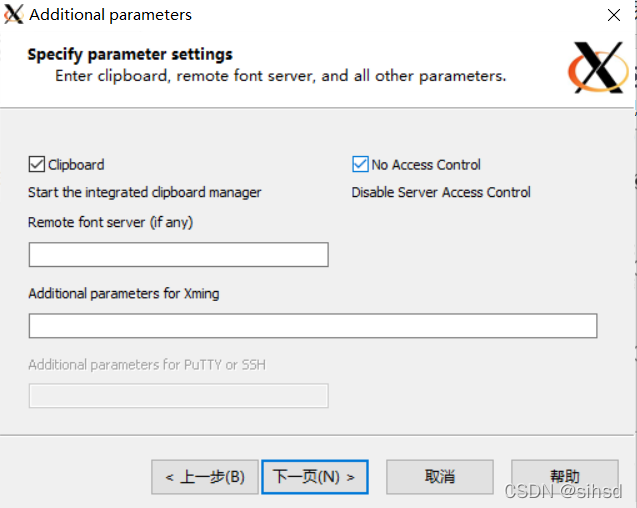

![Xming连接无桌面linux,[转帖]windows+xshell+xming访问非桌面版Linux服务器](https://img-blog.csdnimg.cn/img_convert/08e95fd472a17333efd9f2203ea65290.png)