这篇文章主要记录近几天在使用Vivado以及Synplify工具进行FPGA的Synthesis、Implementation、以及BitStream出现的相关问题。

一、工具使用

RTL代码编辑:修改Vivido内置编辑器为VSCode编辑器,个人习惯,偏好VSCode。修改内置编辑器:Tool -> setting 在Tool Settings里的Text Editor使用Custom Editor,然后配置想要编辑器的文件位置即可。

Simulation:由于最近常使用Vivado,就直接使用的是内置仿真器,如果做SoC设计,更偏好于VCS或者ModeSim。

Synthesis:当Coding量一多,如果只使用Vivado进行Synthesis,会非常慢。通过之前的项目经验,采用算法先进的Synplify对来综合,会使综合效果更好,针对我这个等级的学生来说,主要是综合的越快就更好了。

Implementation:由于使用Xilinx的A7200T系列FPGA芯片,故实现选择在Vivado上进行。

二、记录问题

2.1 Synplify怎么综合带有Vivado IP核的工程呢?

由于我在工程中有使用到,BRAM,PLL这两个IP核,所以如果想在Synplify中综合该Project,必须解决IP核问题。

方法一 white box:将IP核放到Synplify中综合,综合完成后自动导入Synplify的工程。

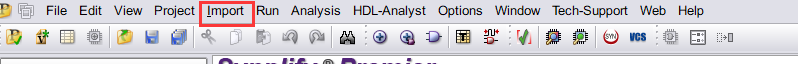

操作步骤:

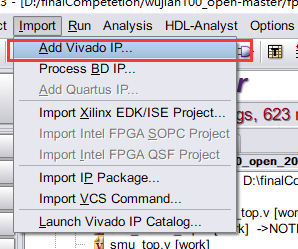

最后点击import即可,不过在综合之前需要配置好vivado的位置,即Synplify中的P& R Implementation。

这样就可以在Synplify中使用在Vivado中定义的IP核,但会出现一个问题,如果使用了两个相同的IP核,但是参数不同。例如,配置两个BRAM,如果BRAM的大小不一样,且COE配置文件也不一样。那就会由两个IP,但是这两个IP都是来自同一个Block Memory Generator。就表明内部实现其实是一样的,但是网表会根据不同配置产生不同的结果。但是如果只是在Synplify生成”white box“,会产生.v文件,那就会产生上述两个IP中可能存在相同子模块,其实经过查看综合后结果,发现各模块名,除了顶层IP模块名有自己定义,其他均一模一样,这样直接综合会导致编译报错:出现了相同的block,当然这个错误在Synplify中通过command可以ignore,但是我在尝试该方法后,电路功能错误。便没有继续在此方法上继续花费时间,主要是该工程用到分布式的RAM,且有多个相同的IP。便继续下述的方法二了。

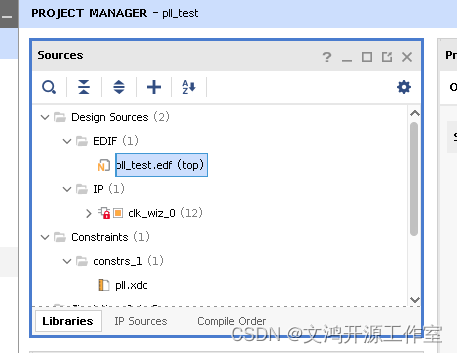

方法二 black box:这个方法在Xilinx官方的User Guide里面的ug994里面的使用第三方工具进行综合中有详细讲解。基本思想主要是将加入的IP核当成一个黑盒,在Synthesis的时候不对其进行优化,所以我们仅需要在Synplify的Project中加入生成IP核时的×××_stub.v文件即可,这是Vivado自动生成的文件,也是非常的人性化。最后点击RUN进行Synthesis即可生成网表以及约束文件,该网表是可以直接给Vivado进行实现的。

2.2 如何Implementation呢?

根据基础的知识,想要对设计进行Implementation,必须要有综合后的门级电路网表以及时序约束核管脚约束等文件。电路网表已经在Synplify中生成,时序约束也自动生成了,不过要根据具体的约束以及结果进行修改和编写。管教约束为自己根据FPGA的引脚以及顶层输入输出引脚进行配置。最后,只差了IP核的电路网表,在 Xilinx的ISE中,使用IP核是会直接生成网表的,但在升级后的Vivado中,会生成DCP文件或者更高级的XCI文件。其实在这里使用DCP文件即可了。最后各个文件加入,点击Implementation即可。